CUDA C++最佳实践指南:评估、并行化与优化

需积分: 9 37 浏览量

更新于2024-07-09

收藏 2.35MB PDF 举报

"CUDA_C_Best_Practices_Guide.pdf"是一份CUDA编程的最佳实践指南,由NVIDIA发布,适用于CUDA 11.2版本。该文档旨在帮助开发者优化和充分利用GPU(图形处理单元)进行并行计算,特别是在C++环境中。以下是该文档的核心内容概览:

1. 评估应用 (Chapter 1)

- 开篇部分强调了评估应用程序的重要性,包括确定哪些部分适合在GPU上执行,以及理解CPU和GPU间的差异。开发者应分析其代码性能瓶颈,找出潜在的并行化机会。

2. 异构计算 (Chapter 2)

- 这一章节深入讨论了主机(CPU)与设备(GPU)之间的区别,如内存访问模式、数据传输效率等。同时,介绍CUDA设备上可以运行的计算任务类型。

3. 应用性能分析 (Chapter 3)

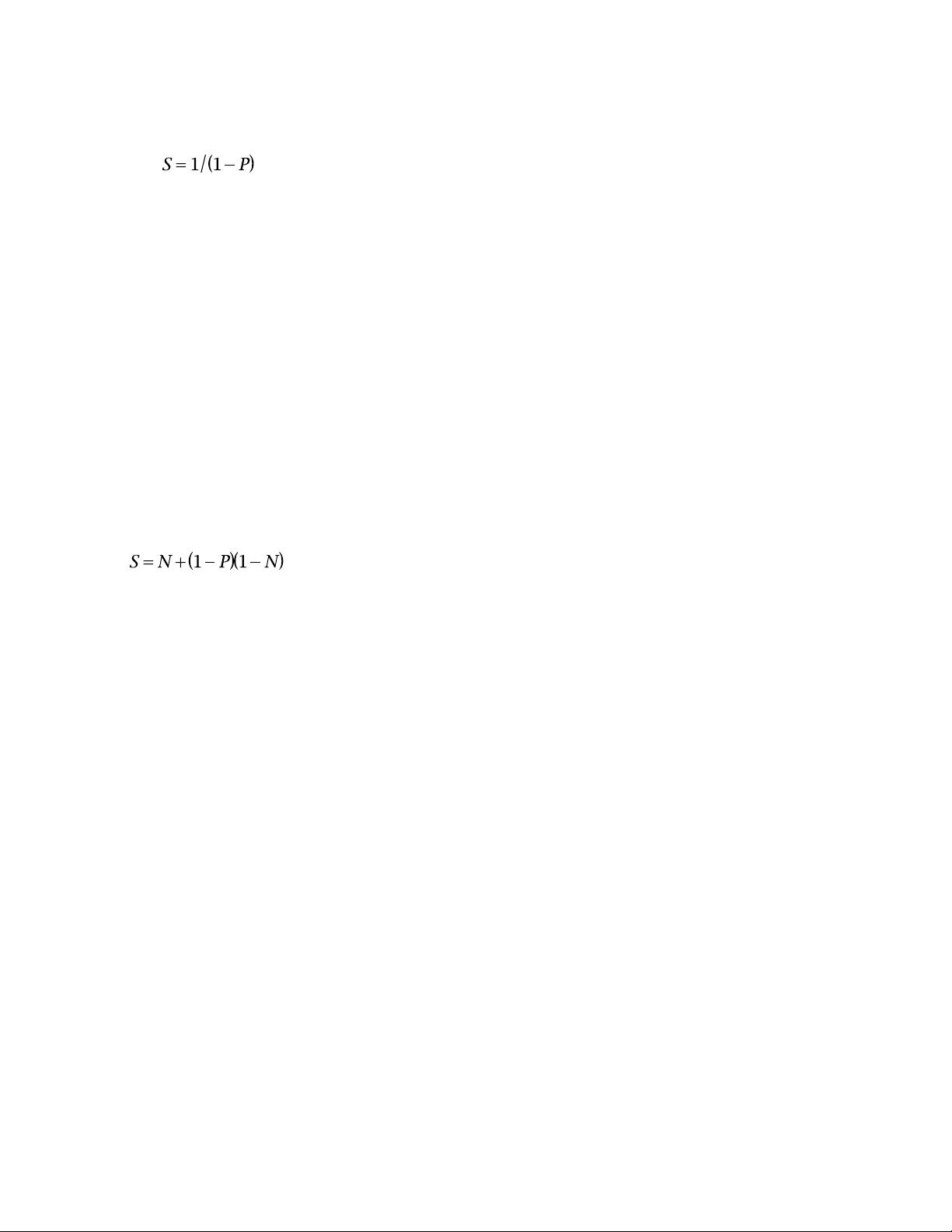

- 应用程序性能剖析是提升效率的关键步骤。讲解如何创建性能报告、识别热点区域(性能消耗高的部分),并运用强(理想情况下的加速)和弱(所有处理器都能扩展的问题)规模法则来理解代码的可扩展性。

4. 并行化策略 (Chapter 4)

- 详细阐述如何将代码转化为利用CUDA并行库或通过编译器选项来暴露并行性,以便让GPU执行多线程任务。

5. 入门指导 (Chapter 5)

- 提供了开始CUDA编程的实用建议,涉及使用并行库、选择支持CUDA的编译器,以及如何编写能有效利用GPU的代码。

6. 确保正确性 (Chapter 6)

- 介绍了验证结果的方法,如使用参考代码对比和单元测试。同时,还强调了调试技巧以及保持数值准确性的必要性。

这份最佳实践指南不仅提供了理论指导,还包括了许多实用的编码技巧和性能调优策略,旨在帮助开发者更有效地设计、实现和部署高性能的GPU应用程序。通过阅读和遵循这些指南,开发者可以避免常见的错误,提高代码效率,并最大化CUDA设备的性能潜力。

2021-10-03 上传

199 浏览量

132 浏览量

214 浏览量

2014-12-22 上传

2012-03-20 上传

112 浏览量

128 浏览量

111 浏览量

乖抱熊

- 粉丝: 4

- 资源: 9

最新资源

- 一个帮助实现条形码扫描的库-Android开发

- casile:CaSILE工具包,采用SILE和其他向导的图书出版工作流程

- TextureSwiftSupport:一个使我们获得DSL来在Texture中定义布局规范的库[如SwiftUI]

- 高端大气星级酒店展示网站静态模板.zip

- PING-开源

- 雷达成像中的时频分析成像

- WebRtcAecmSample:这是一个aecm示例(使用webrtc)

- bluetooth.rar_android 蓝牙_android bluetooth_android蓝牙_蓝牙_蓝牙通信

- area_of_a_regular_polygon

- LibraryPractice_20210327

- ruby-on-rails-cassandra:Ruby on Rails与Cassandra

- 泛型MakeGeneric方法应用实例.rar

- 影刀RPA系列公开课3:网页自动化——数据抓取.rar

- formation_control-master.zip_formation control_formation_control

- matlab标注字体代码-MATLAB-Tools:为MATLAB生成的一组脚本,这些脚本可能在您自己的项目和文件中有用

- flex-masonry:用CodeSandbox创建