5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

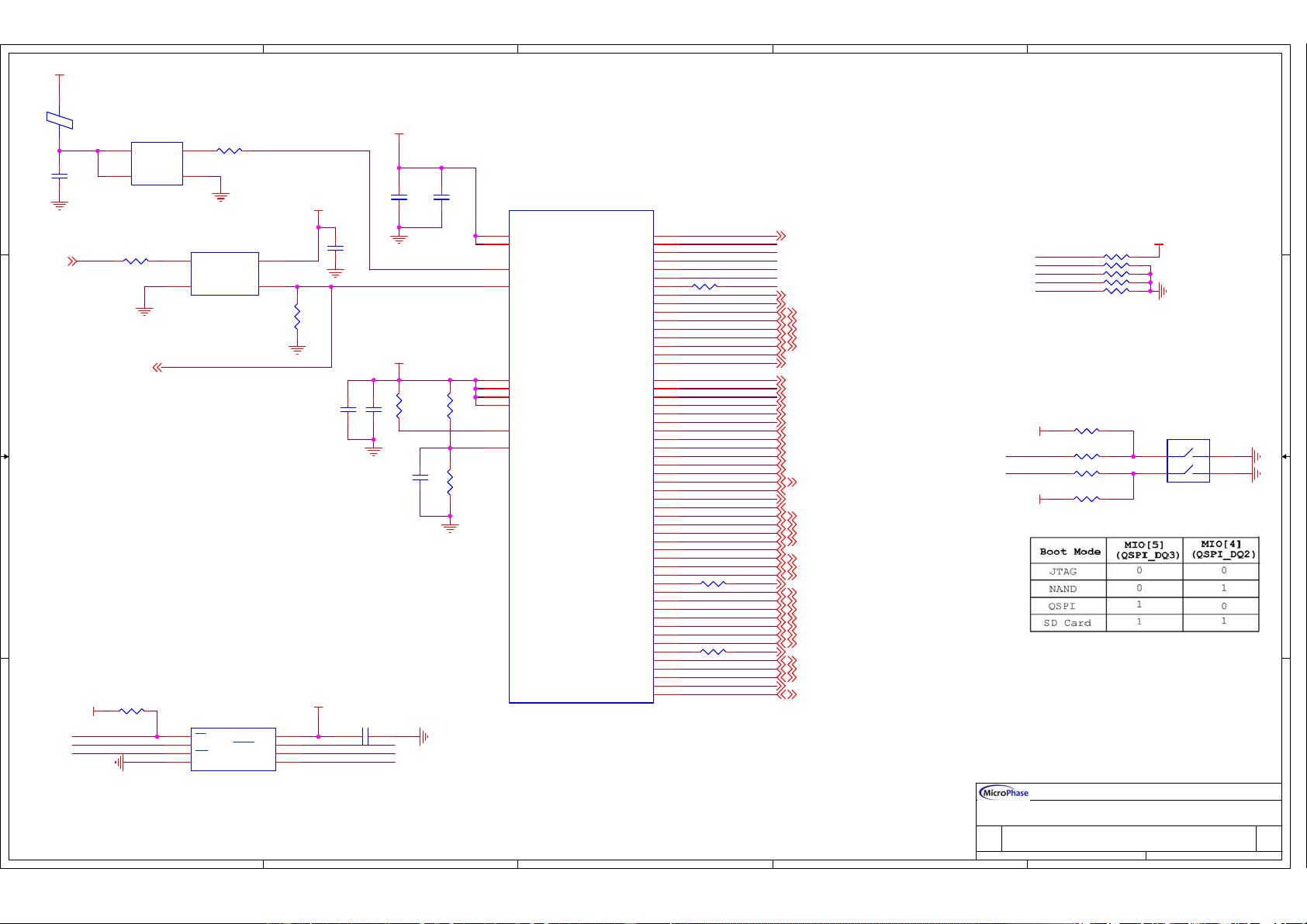

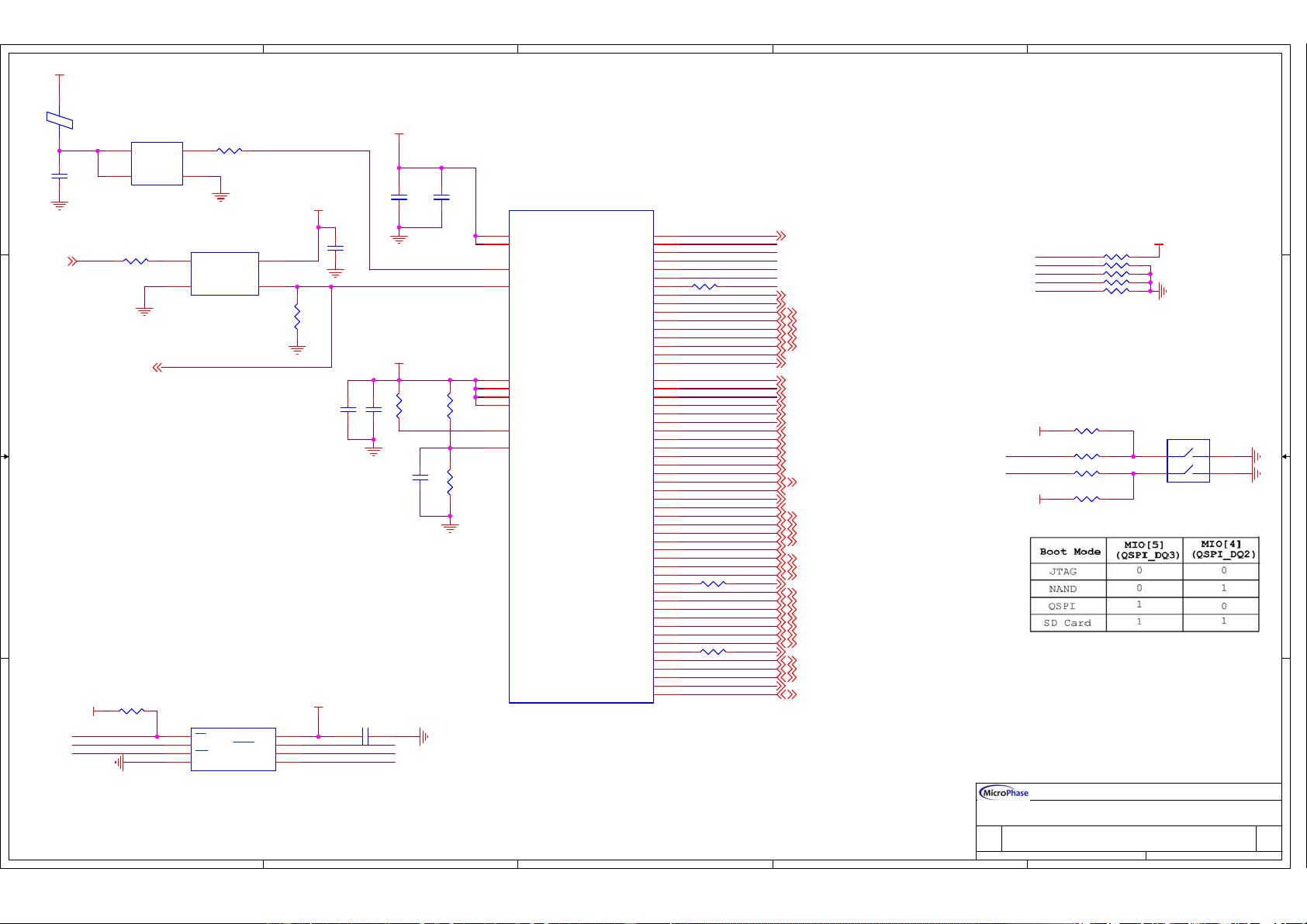

MIO[8] =1 ----MIO bank1 voltage=1.8V

MIO[2] =0 ----cascaded JTAG

MIO[3] =0 ----JTAG/NAND/Quad-SPI/SD

MIO[6] =0 ----PLL used

MIO[7] =0 ----MIO bank0 voltage=3.3V

B2B CON

B2B CON

SPI

BOOT

BOOT

B2B CON

B2B CON

B2B CON

B2B CON

B2B CON

B2B CON(UART)

ETH

ETH

ETH

ETH

ETH

ETH

ETH

ETH

ETH

ETH

ETH

ETH

B2B CON(USB)

B2B CON(USB)

B2B CON(USB)

B2B CON(USB)

B2B CON(USB)

B2B CON(USB)

B2B CON(USB)

B2B CON(USB)

B2B CON(USB)

B2B CON(USB)

B2B CON(USB)

B2B CON(USB)

B2B CON(SD)

B2B CON(SD)

B2B CON(SD)

B2B CON(SD)

B2B CON(SD)

B2B CON(SD)

eMMC

eMMC

eMMC

eMMC

eMMC

eMMC

ETH

ETH

SPI/BOOT

SPI/BOOT

SPI/BOOT

SPI/BOOT

SPI/BOOT

B2B CON(UART)

MIO8

MIO2

MIO3

MIO6

MIO7

QSPI_DQ2

QSPI_DQ3

OTG_nRST

ETH_nRST

QSPI_CLK

QSPI_DQ1

QSPI_DQ0

QSPI_CLK

QSPI_DQ0

QSPI_CS

QSPI_DQ3

QSPI_DQ2

QSPI_DQ1

ETH_nRST

PS_LED

QSPI_CS

QSPI_DQ0

QSPI_DQ1

OTG_nRST

MIO9

MIO10

MIO11

MIO12

MIO13

UART_RX

UART_TX

QSPI_DQ2

QSPI_DQ3

ETH_TXCK

ETH_TXD0

ETH_TXD1

ETH_TXD2

ETH_TXD3

ETH_TXCTL

ETH_RXCK

ETH_RXD0

ETH_RXD1

ETH_RXD2

ETH_RXD3

ETH_RXCTL

OTG_DATA4

OTG_DIR

OTG_STP

OTG_NXT

OTG_DATA0

OTG_DATA1

OTG_DATA2

OTG_DATA3

OTG_CLK

OTG_DATA5

OTG_DATA6

OTG_DATA7

SD_CMD

SD_DATA0

SD_DATA1

SD_DATA2

SD_DATA3

MMC_DATA0

MMC_CMD

MMC_DATA1

MMC_DATA2

MMC_DATA3

ETH_MDC

ETH_MDIO

SD_CLK

MMC_CLK

PS_CLK_33d3

QSPI_CLK

RESET_N

PS_POR_B

VCC_3V3

VCC_1V8

VCC_3V3

VCC_3V3

VCC_3V3

VCC_3V3

VCC_3V3

VCC_3V3

VCC_3V3

RESET_N14

PS_POR_B10

ETH_nRST 11

OTG_nRST 12

UART_TX 14

UART_RX 14

MIO9 14

MIO10 14

MIO11 14

MIO12 14

MIO13 14

ETH_TXD0 11

ETH_TXD1 11

ETH_TXD2 11

ETH_TXD3 11

ETH_TXCK 11

ETH_TXCTL 11

OTG_DATA4 12

OTG_DATA0 12

OTG_DATA1 12

OTG_DATA2 12

OTG_DATA3 12

OTG_DATA5 12

OTG_DATA6 12

OTG_DATA7 12

OTG_STP 12

OTG_DIR 12

OTG_NXT 12

OTG_CLK 12

SD_CMD 14

SD_DATA0 14

SD_DATA1 14

SD_DATA2 14

SD_DATA3 14

MMC_DATA0 10

MMC_CMD 10

MMC_DATA1 10

MMC_DATA2 10

MMC_DATA3 10

ETH_MDIO 11

MMC_CLK 10

ETH_MDC 11

SD_CLK 14

ETH_RXCK 11

ETH_RXD0 11

ETH_RXD1 11

ETH_RXD2 11

ETH_RXD3 11

ETH_RXCTL 11

PS_LED 2

Title

Size

Document Number Re v

Date: Sheet

of

MicroPhase Inc. www.microphase.cn

XME0715 SoC Module

1.0

PS BANK500, BANK501

B

315Wednesday, October 09, 2019

Title

Size

Document Number Re v

Date: Sheet

of

MicroPhase Inc. www.microphase.cn

XME0715 SoC Module

1.0

PS BANK500, BANK501

B

315Wednesday, October 09, 2019

Title

Size

Document Number Re v

Date: Sheet

of

MicroPhase Inc. www.microphase.cn

XME0715 SoC Module

1.0

PS BANK500, BANK501

B

315Wednesday, October 09, 2019

U4

W25Q256FVEI

CS

1

DO(IO1)

2

WP(IO2)

3

GND

4

DI(IO0)

5

CLK

6

HOLD(IO3)

7

VCC

8

R8 33R

R21 10K

C5

0.1uF

BANK500&501

XC7Z015CLG485

U1-2

PS_MIO3_500

F17

PS_MIO2_500

A21

PS_MIO1_500

A22

PS_MIO0_500

G17

PS_CLK_500

F16

PS_POR_B_500

B18

PS_MIO15_500

E17

PS_MIO14_500

B17

PS_MIO13_500

A17

PS_MIO12_500

C18

PS_MIO11_500

B19

PS_MIO10_500

G16

PS_MIO9_500

C19

PS_MIO8_500

E18

PS_MIO7_500

D18

PS_MIO6_500

A19

PS_MIO5_500

A20

PS_MIO4_500

E19

VCCO_MIO0_500

B20

VCCO_MIO0_500

C17

PS_MIO16_501

D17

PS_MIO17_501

E14

PS_MIO18_501

A16

PS_MIO19_501

E13

PS_MIO20_501

A15

PS_MIO21_501

F12

PS_MIO22_501

A9

PS_MIO23_501

E12

PS_MIO24_501

B16

PS_MIO25_501

F11

PS_MIO26_501

A10

PS_MIO27_501

D16

PS_MIO28_501

A11

PS_MIO29_501

E15

PS_MIO30_501

A12

PS_MIO31_501

F14

PS_MIO32_501

C16

PS_MIO33_501

G11

PS_MIO34_501

B11

PS_MIO35_501

F9

PS_MIO36_501

A14

PS_MIO37_501

B9

PS_MIO38_501

F10

PS_MIO39_501

C10

PS_MIO40_501

E9

PS_MIO41_501

C15

PS_MIO42_501

D15

PS_MIO43_501

B12

PS_MIO44_501

E10

PS_MIO45_501

B14

PS_MIO46_501

D11

PS_MIO47_501

B13

PS_MIO48_501

D12

PS_MIO49_501

C9

PS_MIO50_501

D10

PS_MIO51_501

C13

PS_MIO52_501

D13

PS_MIO53_501

C11

VCCO_MIO1_501

A13

VCCO_MIO1_501

B10

VCCO_MIO1_501

D14

VCCO_MIO1_501

E11

PS_MIO_VREF_501

F15

PS_SRST_B_501

C14

R16 20K

R15

4.7K

R24 33R

C9

0.1uF

R25 33R

R19 10K

C4

47uF/6.3V

B3

BLM15AX601SN1D

1 2

C3

470nF

C10

0.1uF

R13 20K

R22

3.32K 1%

U3

ADM6711SAKSZ

GND

1

#RESET

2

#MR

3

VDD

4

C11 0.1uf

J1

SW4

1

2 3

4

R14 33R

R9 330R

R10 20K

R12 20K

R26 NC

U2

33.3333M

OE

1

GND

2

OUT

3

VDD

4

C7

47uF/6.3V

R23 10K

R18

3.32K 1%

C6

0.1uF

R11 20K

R17

4.7K

R20 10K