8x8乘法器后端流程详解:入门指南

版权申诉

本篇文档《IC设计后端流程初学必看.pdf》旨在为初学者提供一个8*8乘法器设计的简化版后端流程指南,以帮助理解数字集成电路设计的基本步骤。流程主要包括以下几个关键环节:

1. **逻辑综合**:这是将高级语言(如Verilog)转换成低级硬件描述语言(HDL),如门级网表的过程。逻辑综合确保了设计意图的有效实现。

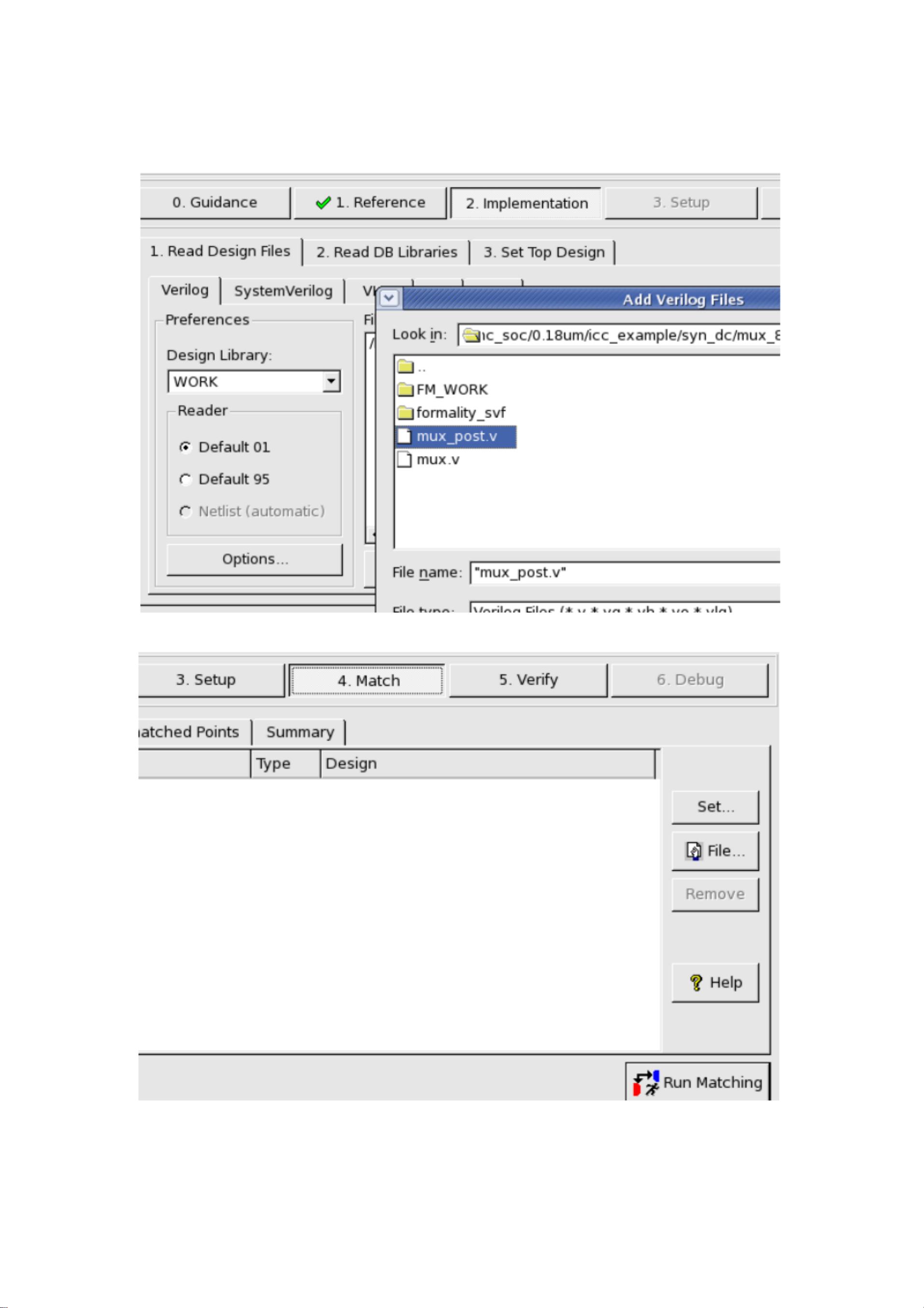

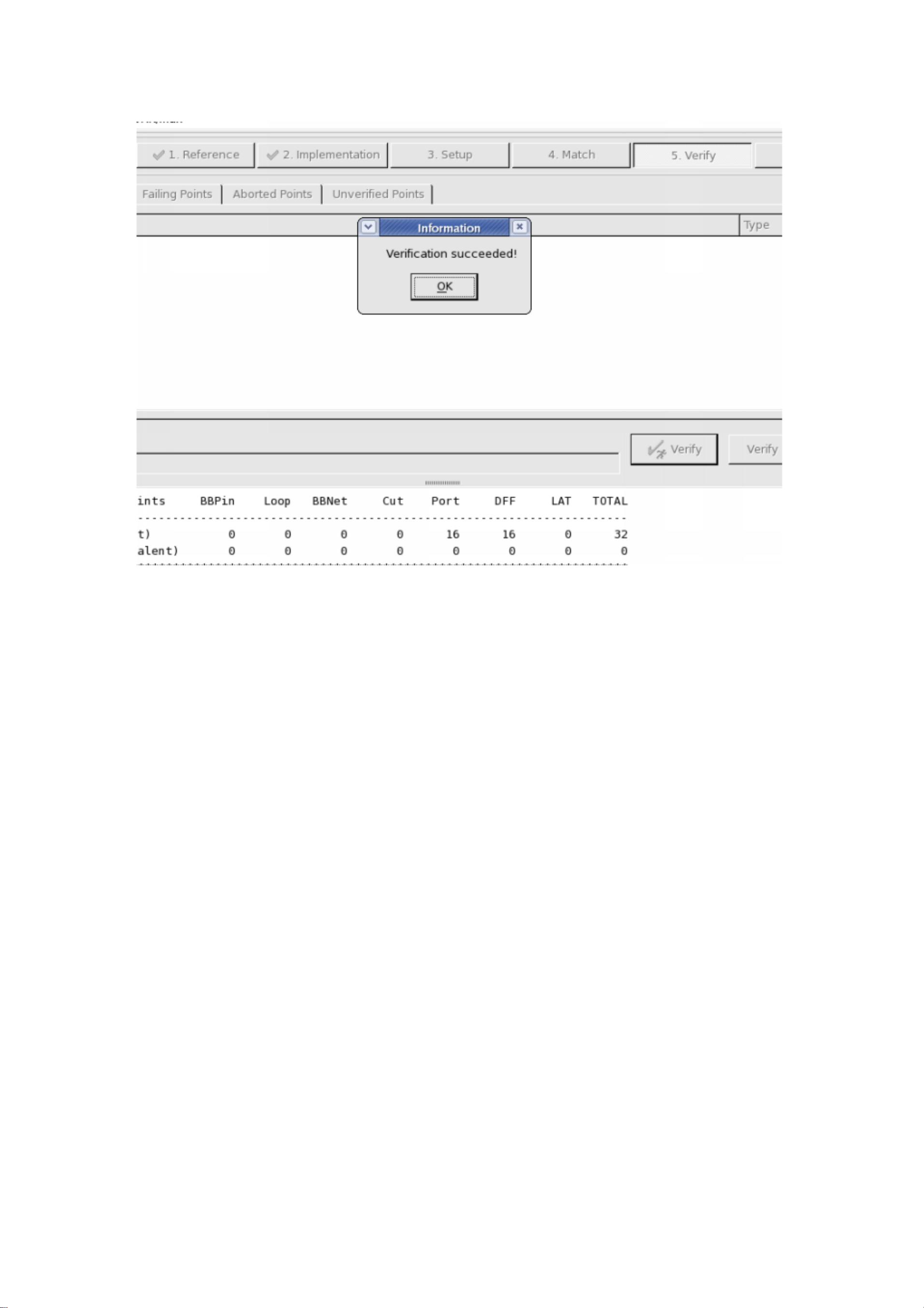

2. **设计形式验证**:利用工具如Formality进行功能验证,检查从RTL代码到综合后的网表逻辑一致性。由于大尺寸设计的动态仿真耗时过长,形式验证成为快速验证设计的重要手段,可以在几小时内完成大规模验证。

3. **静态时序分析 (STA)**:使用Primetime进行布图前的时序分析,确保电路工作在预定的时序规范内。若发现时序问题,可能需要重新综合。

4. **自动布局与布线 (APR)**:CADENCE的SOC Encounter用于自动化布局和布线,生成具体延迟信息,SDF文件记录寄生和互联电阻引起的延迟。

5. **重复静态时序分析**:结合APR的结果进行多次迭代,直至满足时序要求。

6. **门级功能仿真**:在APR后可能需要进一步进行功能仿真,确认设计行为正确。

7. **设计规则检查 (DRC) 和逻辑验证 (LVS)**:这两个步骤确保设计符合工艺规则和逻辑一致性,通过后继续流程。

8. **抽象与抽取**:使用抽象技术(如Abstract)将乘法器设计转化为LEF文件,形成硬宏(hard macro),便于在其他设计中复用。

9. **模块集成**:将硬宏作为模块在顶层设计(top design)中调用,构建完整的系统架构。

10. **ASIC设计流程**:整个过程是为了设计一个全新的ASIC,从高级代码到实际芯片制造,每个环节都至关重要,且需要严谨的流程控制和不断优化。

通过这个教程,学习者可以了解到IC设计后端流程的核心要素和技术挑战,为进一步深入学习打下基础。但要注意,由于教程基于个人实验,内容可能存在不完善和错误,作者承诺将在后续学习中不断更新和修正。

2020-08-09 上传

2020-12-18 上传

2020-12-18 上传

2019-09-24 上传

2021-04-12 上传

ll17770603473

- 粉丝: 0

- 资源: 6万+