CPLD电子钟设计教程:河北大学实践与MAX+plusII应用

需积分: 9 157 浏览量

更新于2024-08-02

收藏 5.47MB PPT 举报

本文档主要介绍了CPLD电子钟的设计原理和制作过程,以河北大学电信学院的教程形式呈现,旨在为编程爱好者提供一个实践平台。以下是详细内容概述:

1. **课程背景**:文章首先明确了课程的目的,即通过数字电路课程设计,使学生掌握MAX+plusII软件的使用,理解CPLD/FPGA的一般开发步骤,并熟悉如何用这些器件替代传统中小规模集成电路,实现数字电路与系统的创新设计。

2. **学习内容与要求**:

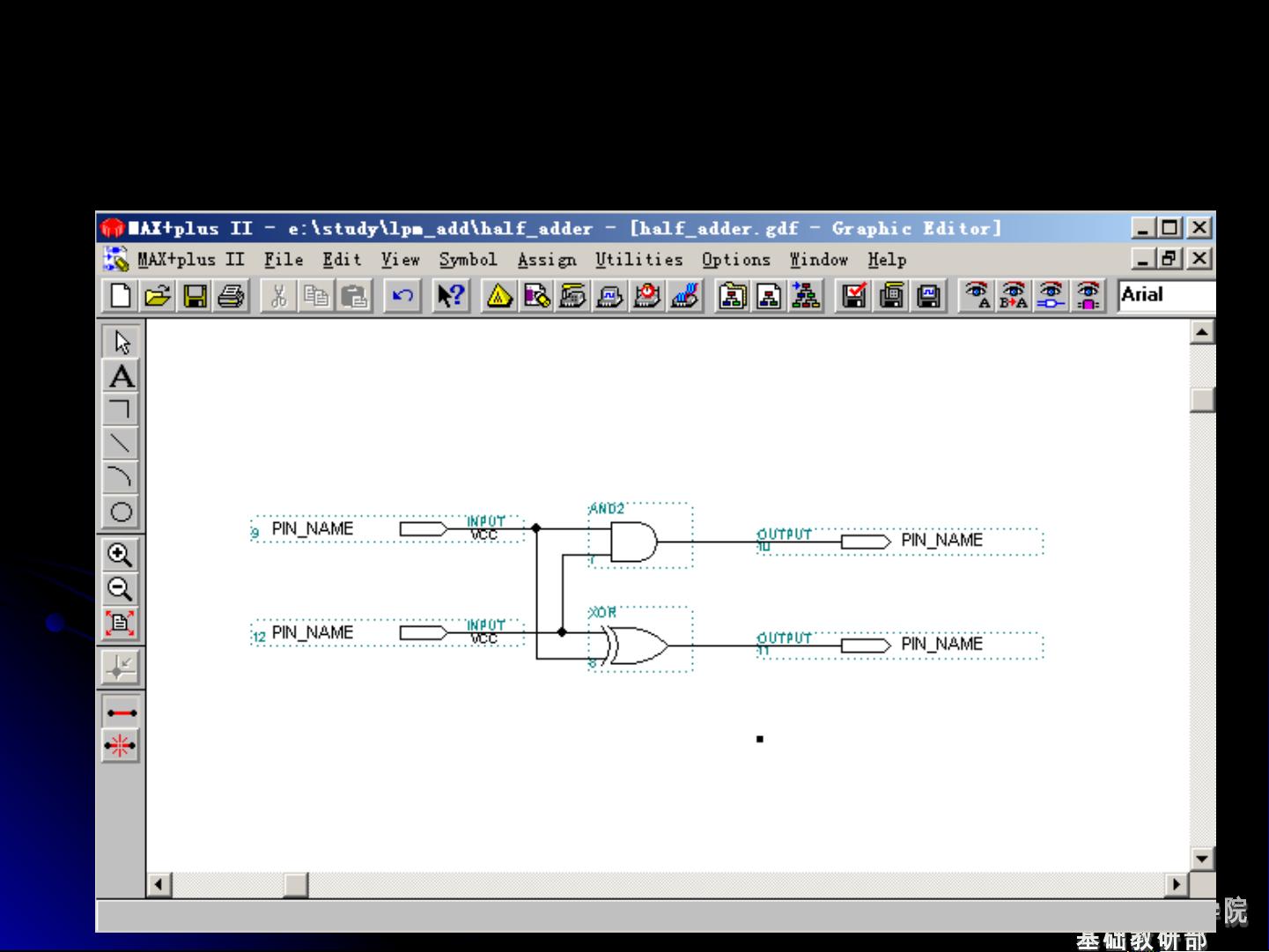

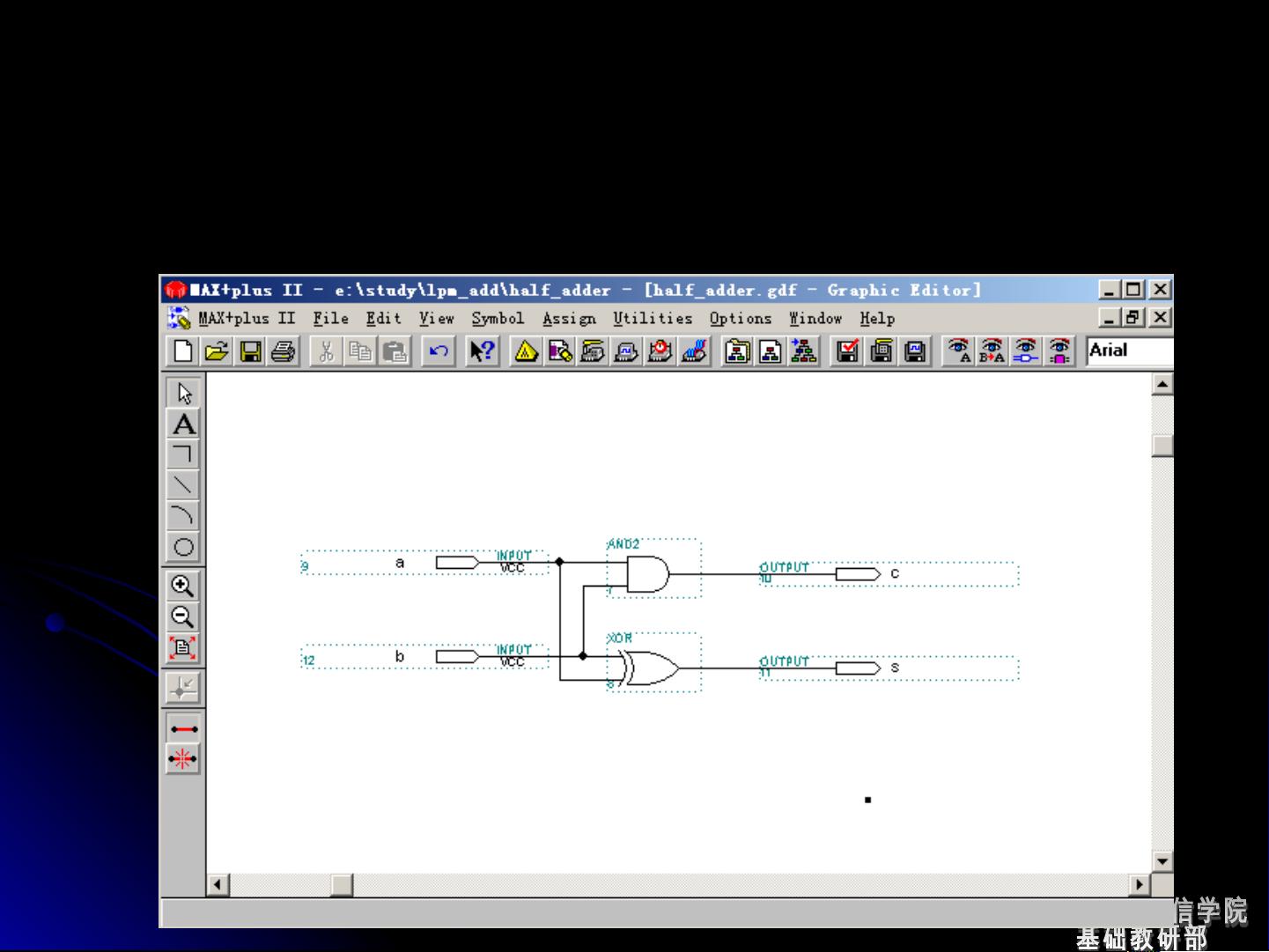

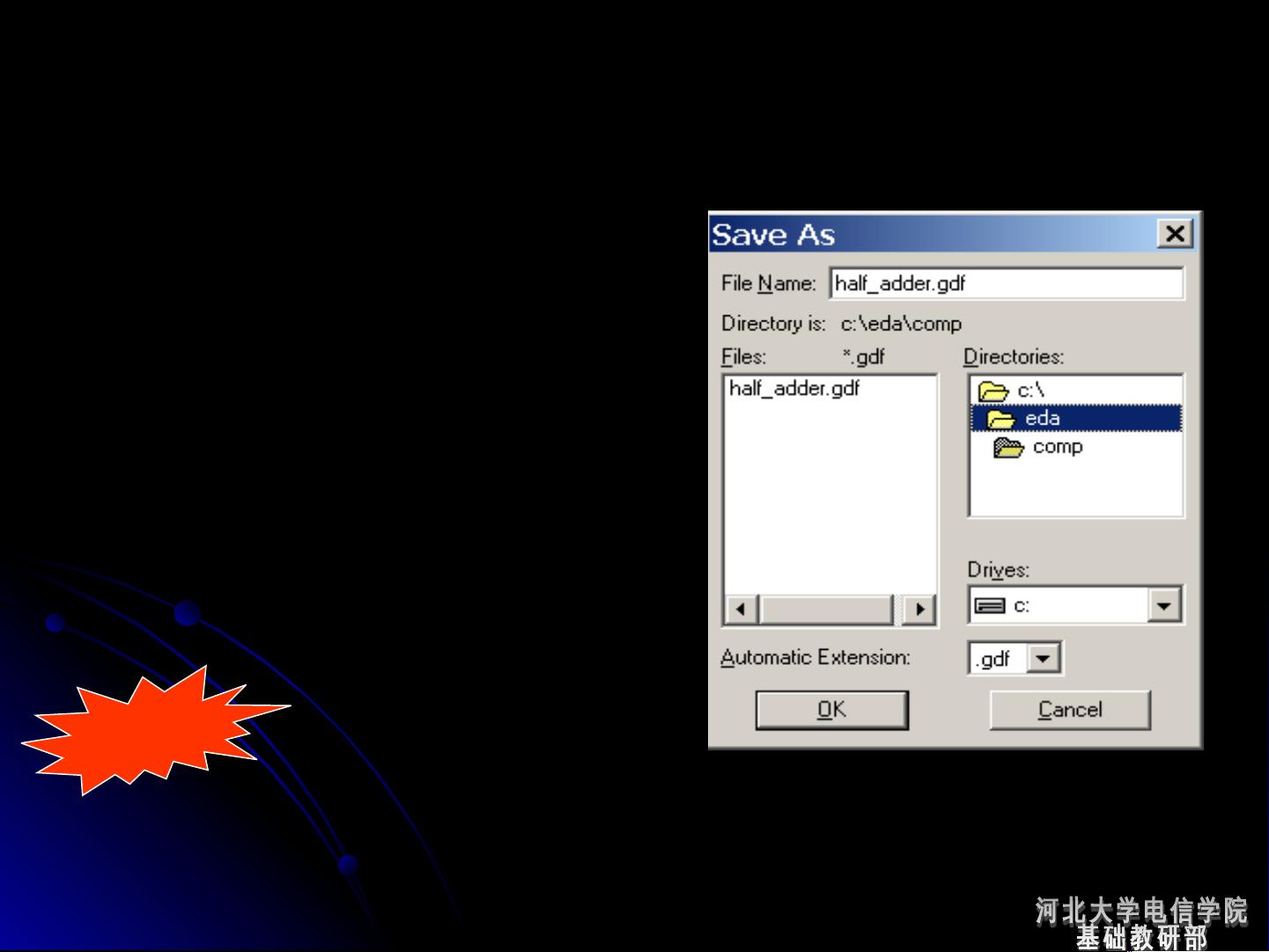

- 学生需要掌握MAX+plusII软件的基本操作,软件的学习以加法器为例,通过实际操作演示如何创建原理图、输入逻辑功能图元、保存文件、设定项目名称以及检查错误。

- 了解CPLD/FPGA的一般开发流程,包括器件的选择、设计策略和编程过程。

- 熟悉CPLD/FPGA在数字钟中的应用,理解数字钟的功能需求及其设计方法。

- 学习常用元件的识别和使用注意事项,确保设计过程中的正确性和安全性。

3. **设计流程**:

- 设计输入阶段包括创建原理图文件(如half_adder.gdf),这涉及到文件创建、逻辑功能图元的添加、文件保存和命名等步骤。

- 采用自底向上的层次设计方法,从最简单的加法器开始,逐步构建更复杂的电路,如进位加法器,然后进行仿真分析,并将设计下载到CPLD芯片中。

4. **结果形式与成绩评定**:课程设计的结果将以实物或电路模型的形式呈现,设计的正确性、创新性以及对软件工具的熟练运用都会影响成绩评定。

5. **MAX+plusII软件介绍**:软件操作指南详细地介绍了如何使用MAX+plusII进行电路设计,如创建新项目、输入图形编辑器界面等,通过实例教学帮助学生理解和掌握。

通过这个教程,学习者不仅能提升数字电路设计技能,还能了解CPLD电子钟的实际应用,从而更好地应用于实际项目中,提高电子设计能力。

2009-11-06 上传

2021-03-03 上传

2021-08-07 上传

2021-10-10 上传

2007-08-28 上传

2013-07-13 上传

2009-10-18 上传

2010-04-09 上传

aicyou

- 粉丝: 0

- 资源: 3

最新资源

- 掌握压缩文件管理:2工作.zip文件使用指南

- 易语言动态版置入代码技术解析

- C语言编程实现电脑系统测试工具开发

- Wireshark 64位:全面网络协议分析器,支持Unix和Windows

- QtSingleApplication: 确保单一实例运行的高效库

- 深入了解Go语言的解析器组合器PARC

- Apycula包安装与使用指南

- AkerAutoSetup安装包使用指南

- Arduino Due实现VR耳机的设计与编程

- DependencySwizzler: Xamarin iOS 库实现故事板 UIViewControllers 依赖注入

- Apycula包发布说明与下载指南

- 创建可拖动交互式图表界面的ampersand-touch-charts

- CMake项目入门:创建简单的C++项目

- AksharaJaana-*.*.*.*安装包说明与下载

- Arduino天气时钟项目:源代码及DHT22库文件解析

- MediaPlayer_server:控制媒体播放器的高级服务器