解决Veristand下cRIO-9047混合编程时的性能问题及Scan+FPGA部署教程

需积分: 0 102 浏览量

更新于2024-08-05

1

收藏 697KB DOCX 举报

在使用NI cRIO-9047控制器在Veristand环境中进行混合编程时,遇到了两个主要问题。首先,用户在尝试通过DAQmx模式采集板卡数据(包括NI9219、NI9205、NI9375、NI9213等)时,发现最大时钟频率限制为100Hz,这显著降低了数据交换速度,导致控制流程延时。原本30秒的数据交互需花费7分钟,影响了系统的实时性。

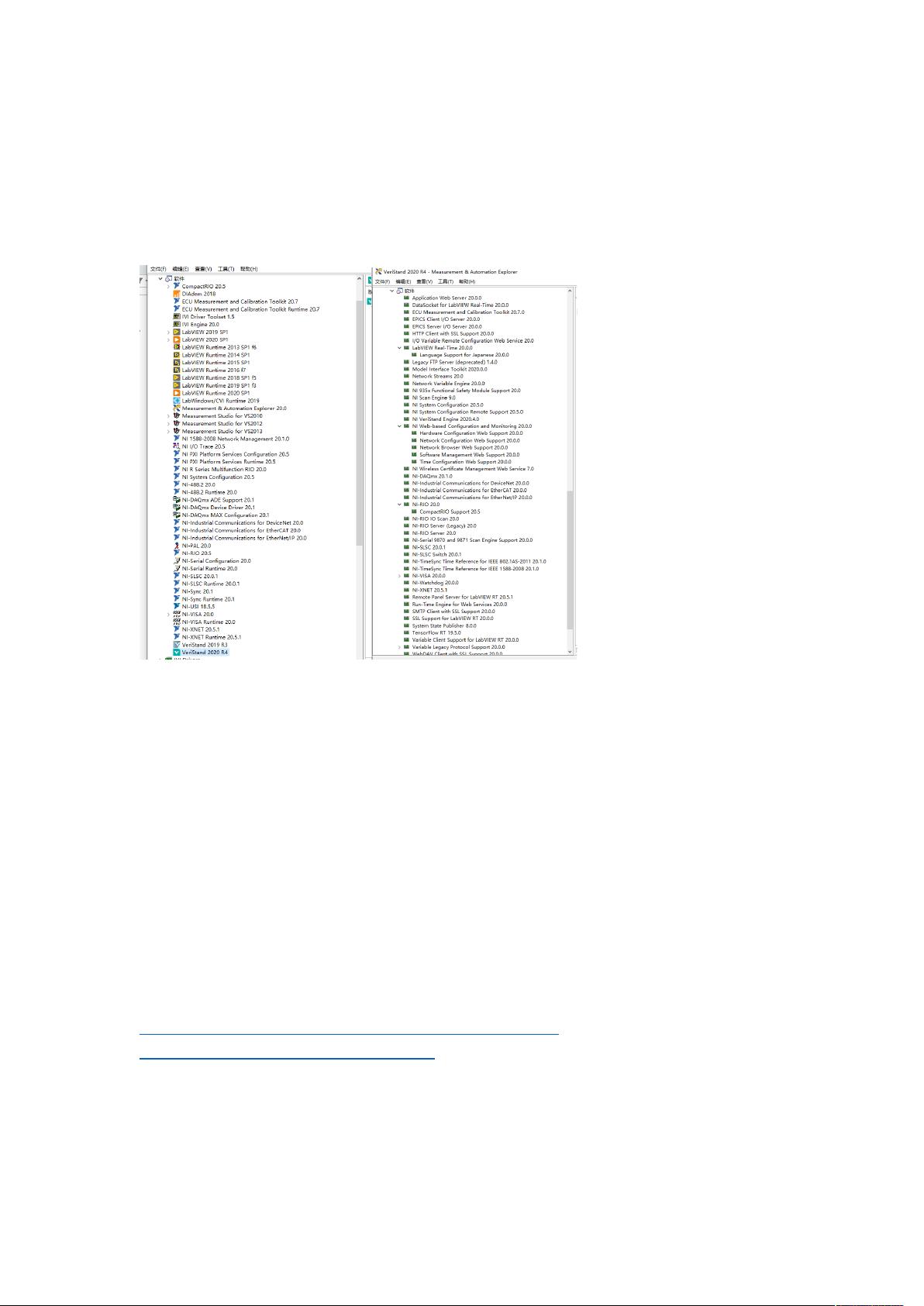

为解决这个问题,用户试图通过提高TargetRate至1000Hz并增加TargetDecimations来加速处理,但结果是Veristand崩溃。随后,用户发现了一种可能的解决方案,即利用Customdevices中的ScanEngineandEtherCAT模块实现FPGA与SCAN的混合编程。这个方法要求在Labview中创建项目并将其部署到FPGA,否则Labview无法识别UDV中定义的变量,从而引发错误。

现存问题有两个:

1. 如果仅手动添加未经过部署的SCAN模式板卡,下位机的用户界面(UI)在Veristand中会崩溃,上位机报错。这意味着只有当使用已经部署过的程序编译生成的bit文件时,加载才能成功。

2. 当尝试以特定的加载模式,比如遇到错误537702,这可能是由于未正确配置或部署FPGA与Labview的连接导致的。这提示用户在进行混合编程时,必须确保所有相关的硬件和软件配置都是同步且正确的。

为解决这些问题,用户应遵循以下步骤:

- 确保DAQmx采集的配置优化到实际需求的时钟频率,同时保持合理的数据处理延迟。

- 根据官方文档(如链接中的知识库文章)使用ScanEngineandEtherCAT进行FPGA与SCAN的混合编程,确保Labview项目部署到FPGA。

- 在添加新板卡或更新配置前,务必先确保其已在FPGA中正确部署,避免因变量识别问题导致的错误。

- 针对崩溃问题,检查下位机UI和Veristand之间的通信是否稳定,以及是否存在兼容性问题。

通过这些调整和优化,可以提升混合编程模式下的NI cRIO-9047控制器在Veristand环境中的性能和稳定性。

2022-07-14 上传

2019-10-18 上传

2019-09-25 上传

2021-03-20 上传

2021-02-13 上传

2021-02-14 上传

2021-05-26 上传

2021-04-01 上传

YANG-SHawn

- 粉丝: 4

- 资源: 1

最新资源

- JavaScript DOM事件处理实战示例

- 全新JDK 1.8.122版本安装包下载指南

- Python实现《点燃你温暖我》爱心代码指南

- 创新后轮驱动技术的电动三轮车介绍

- GPT系列:AI算法模型发展的终极方向?

- 3dsmax批量渲染技巧与VR5插件兼容性

- 3DsMAX破碎效果插件:打造逼真碎片动画

- 掌握最简GPT模型:Andrej Karpathy带你走进AI新时代

- 深入解析XGBOOST在回归预测中的应用

- 深度解析机器学习:原理、算法与应用

- 360智脑企业内测开启,探索人工智能新场景应用

- 3dsmax墙砖地砖插件应用与特性解析

- 微软GPT-4助力大模型指令微调与性能提升

- OpenSARUrban-1200:平衡类别数据集助力算法评估

- SQLAlchemy 1.4.39 版本特性分析与应用

- 高颜值简约个人简历模版分享