数字钟设计:功能与实现

需积分: 10 16 浏览量

更新于2024-09-14

1

收藏 177KB DOC 举报

【资源摘要信息】: "本资源是一份关于数字钟设计的本科实验报告,涉及数字电路的知识,使用VHDL语言进行设计。实验目标是构建一个具备时间显示、手动校时、定时闹钟和整点报时功能的数字钟。报告详细介绍了设计要求、系统方案、硬件电路设计等内容,并提到了实验设备FLEX10K/EPF10K10L84-8。"

在数字电路领域,设计一个数字钟是一项典型的项目,它涉及到多个关键知识点。首先,这个数字钟设计要求显示小时、分钟和秒,且小时范围从00到23,这意味着需要使用二进制编码十进制(BCD)技术来转换十进制数为适合七段数码管显示的二进制编码。每一路数字显示由四个二进制位组成,分别对应BCD编码的四个二进制数位。

其次,手动校时和校分功能需要通过特定的输入信号(如按键)来实现,这些输入会触发时钟内部状态机的更新,使得时间能够增加或减少。这需要设计逻辑电路来处理这些输入并控制时间的增减。

再者,定时与闹钟功能涉及到定时器的设计,这通常通过计数器实现,当达到预设的小时和分钟组合时,触发闹钟信号。在这个设计中,可能还需要一个比较器来检查当前时间和设定的闹钟时间是否匹配,匹配时触发闹钟。

此外,整点报时功能则需要一个特殊的计时器,从59分50秒开始,每隔两秒发出低音“嘟”的信号,共五次,最后一次是高音“嘀”。这需要精确的定时机制,并结合声音发生器来生成不同频率的声音信号。

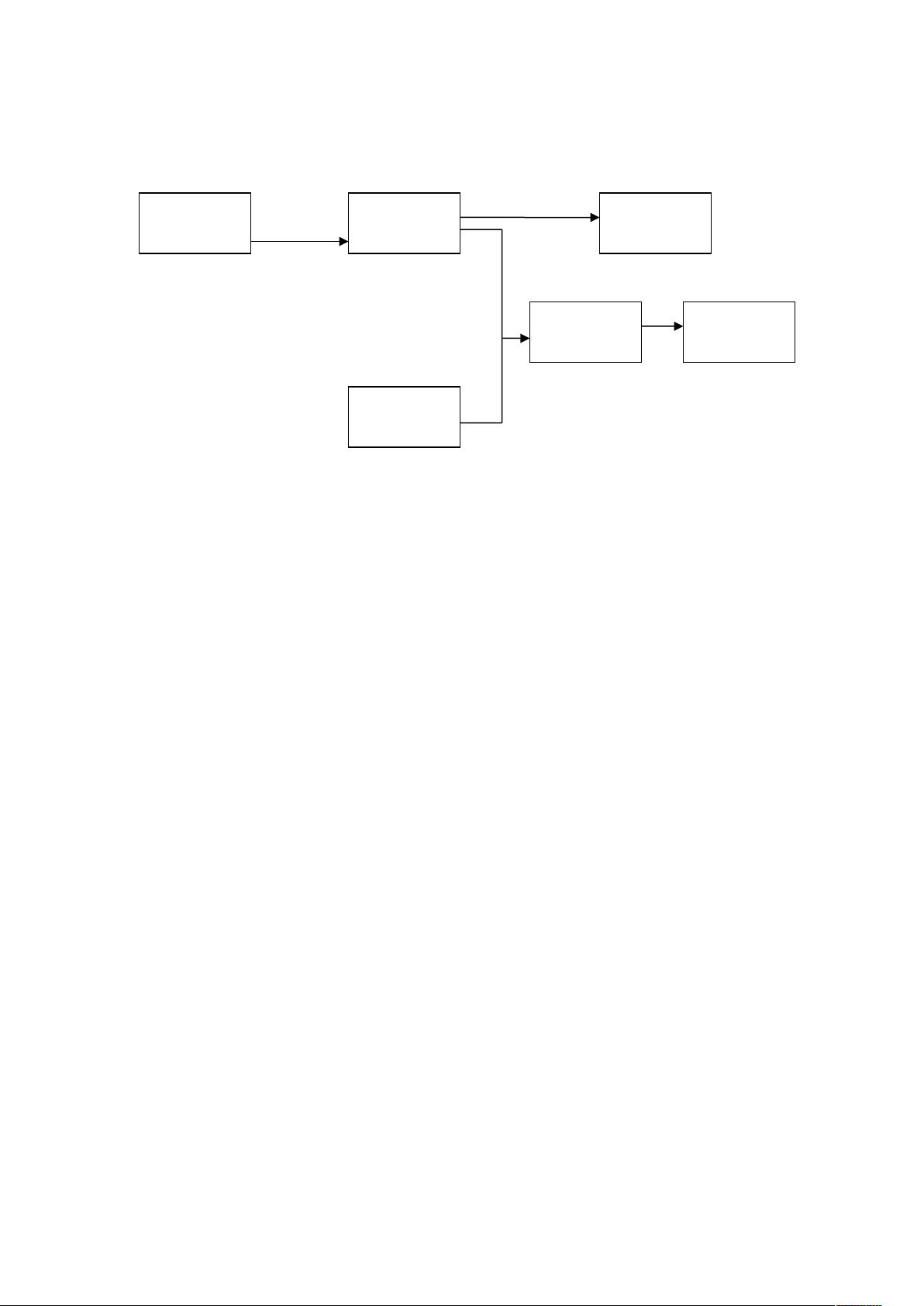

在系统方案设计部分,报告提到了几个关键模块,如控制模块(处理按键输入)、显示模块(负责驱动数码管显示)和时钟逻辑模块(包含计数器和比较器)。这些模块可以通过VHDL等硬件描述语言进行编程,并在FPGA(如FLEX10K/EPF10K10L84-8)上实现。

硬件电路设计部分则涉及如何将这些逻辑设计映射到实际的电子元件上,包括按键、数码管显示和可能的音频发生器。每个按键都会连接到FPGA的输入引脚,而数码管的显示则需要通过并行接口控制。

这个数字钟设计涵盖了数字逻辑、计数器、比较器、状态机、BCD编码、时序电路、硬件描述语言和FPGA编程等多个重要的数字电路和嵌入式系统知识。

2017-02-21 上传

2023-06-02 上传

2023-06-09 上传

2023-08-30 上传

2023-06-06 上传

2023-02-11 上传

2024-06-04 上传

wh__yeah

- 粉丝: 0

- 资源: 1

最新资源

- 达梦数据库DM8手册大全:安装、管理与优化指南

- Python Matplotlib库文件发布:适用于macOS的最新版本

- QPixmap小demo教程:图片处理功能实现

- YOLOv8与深度学习在玉米叶病识别中的应用笔记

- 扫码购物商城小程序源码设计与应用

- 划词小窗搜索插件:个性化搜索引擎与快速启动

- C#语言结合OpenVINO实现YOLO模型部署及同步推理

- AutoTorch最新包文件下载指南

- 小程序源码‘有调’功能实现与设计课程作品解析

- Redis 7.2.3离线安装包快速指南

- AutoTorch-0.0.2b版本安装教程与文件概述

- 蚁群算法在MATLAB上的实现与应用

- Quicker Connector: 浏览器自动化插件升级指南

- 京东白条小程序源码解析与实践

- JAVA公交搜索系统:前端到后端的完整解决方案

- C语言实现50行代码爱心电子相册教程