时序逻辑电路解析:从基本概念到RS锁存器

版权申诉

87 浏览量

更新于2024-07-03

收藏 1010KB PPT 举报

"数字逻辑电路课程课件:第5章 时序逻辑电路.ppt"

在数字逻辑电路中,时序逻辑电路是一个重要的概念,它与组合逻辑电路不同,因为时序逻辑电路不仅取决于当前输入,还依赖于电路的前一状态。这种电路通常包含反馈回路,使得电路的状态随着时间的推移而变化,从而具备记忆功能。

时序逻辑电路的特征在于,它们的输出不仅由当前的输入信号决定,还与之前的电路状态有关。这一特性使得时序逻辑电路能用于存储和处理信息,例如计数器、寄存器和各种类型的存储器。

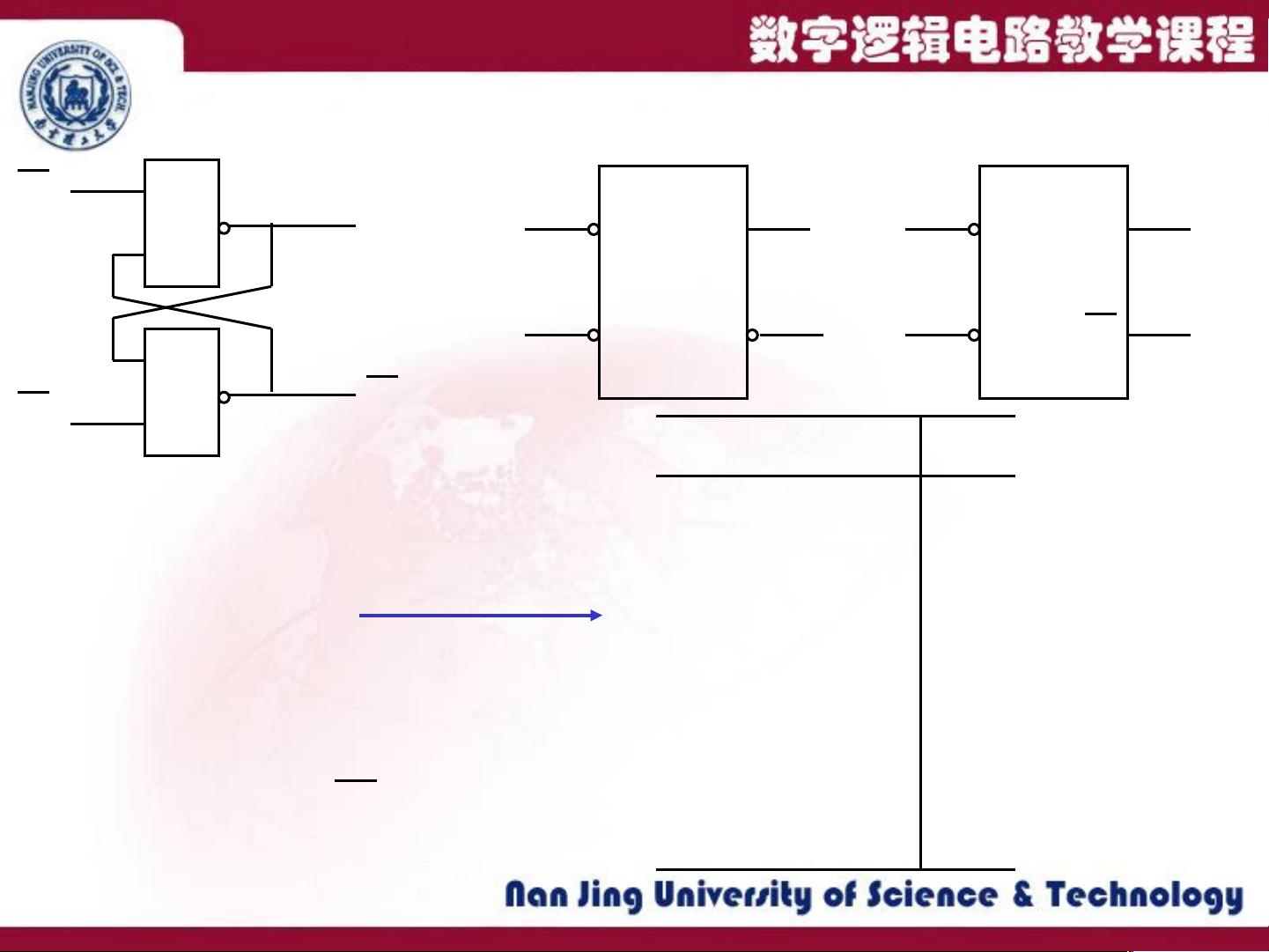

时序逻辑电路的结构模型包括两部分:组合电路和存储电路。组合电路根据输入和当前状态产生输出,而存储电路则保持电路的状态。外部输入信号进入电路,经过组合电路处理后,通过驱动信号影响存储电路,改变电路状态。输出信号则是电路对外部世界的表现,它们是输入和状态的函数。

描述时序逻辑电路的方法主要有以下几种:

1. **逻辑方程**:通过输出方程、驱动方程和状态方程来表达电路的工作原理。输出方程描述了当前输出如何依赖于输入和状态;驱动方程定义了状态变化的触发条件;状态方程则表明下一个状态如何由当前状态和驱动信号决定。

2. **状态表**:以表格形式列出所有可能的输入、当前状态以及由此产生的新状态和输出,直观地展示了电路的行为。

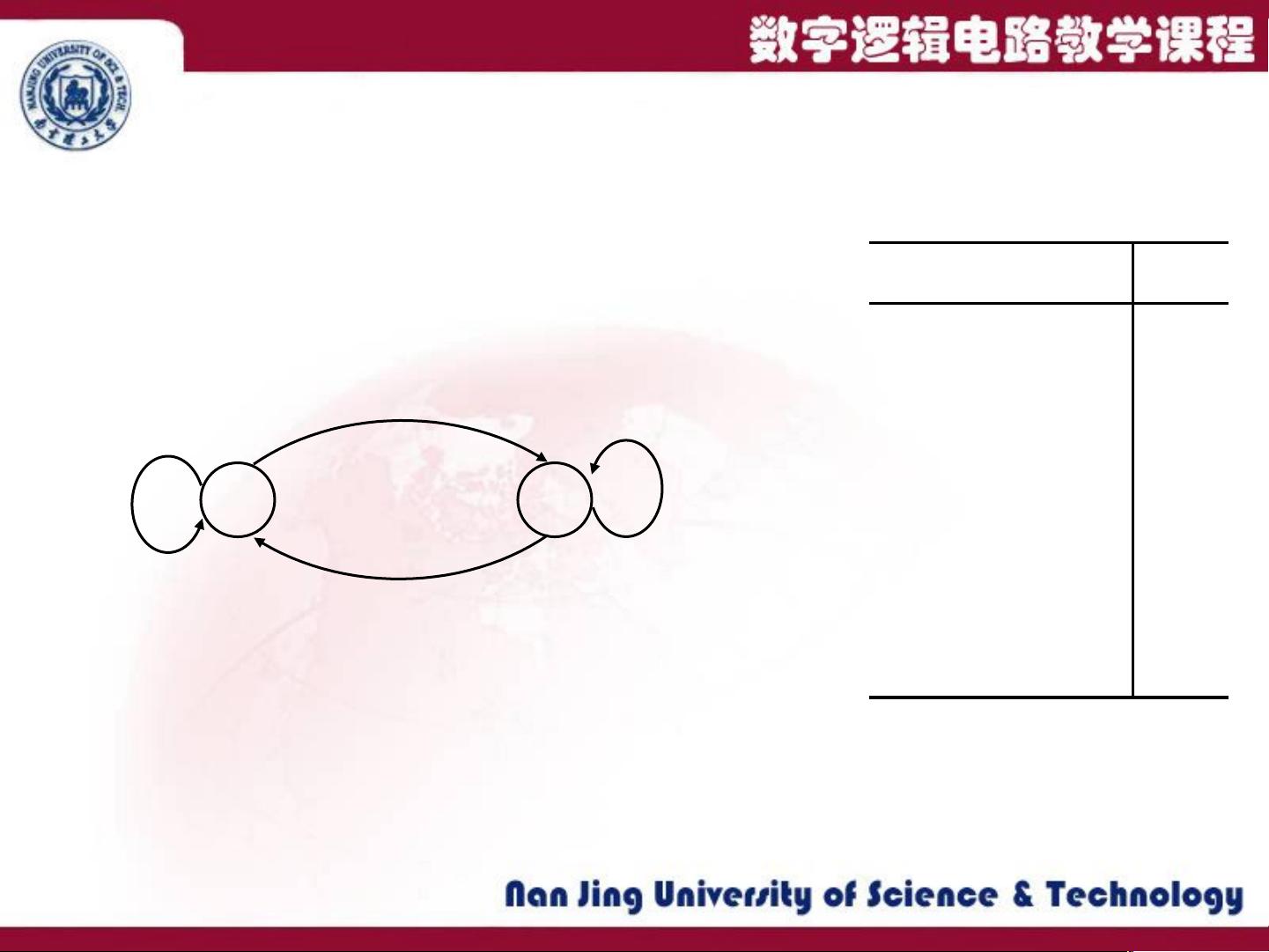

3. **状态图**:利用有向图来表示状态转移,每个节点代表一个状态,箭头指示状态之间的转换。

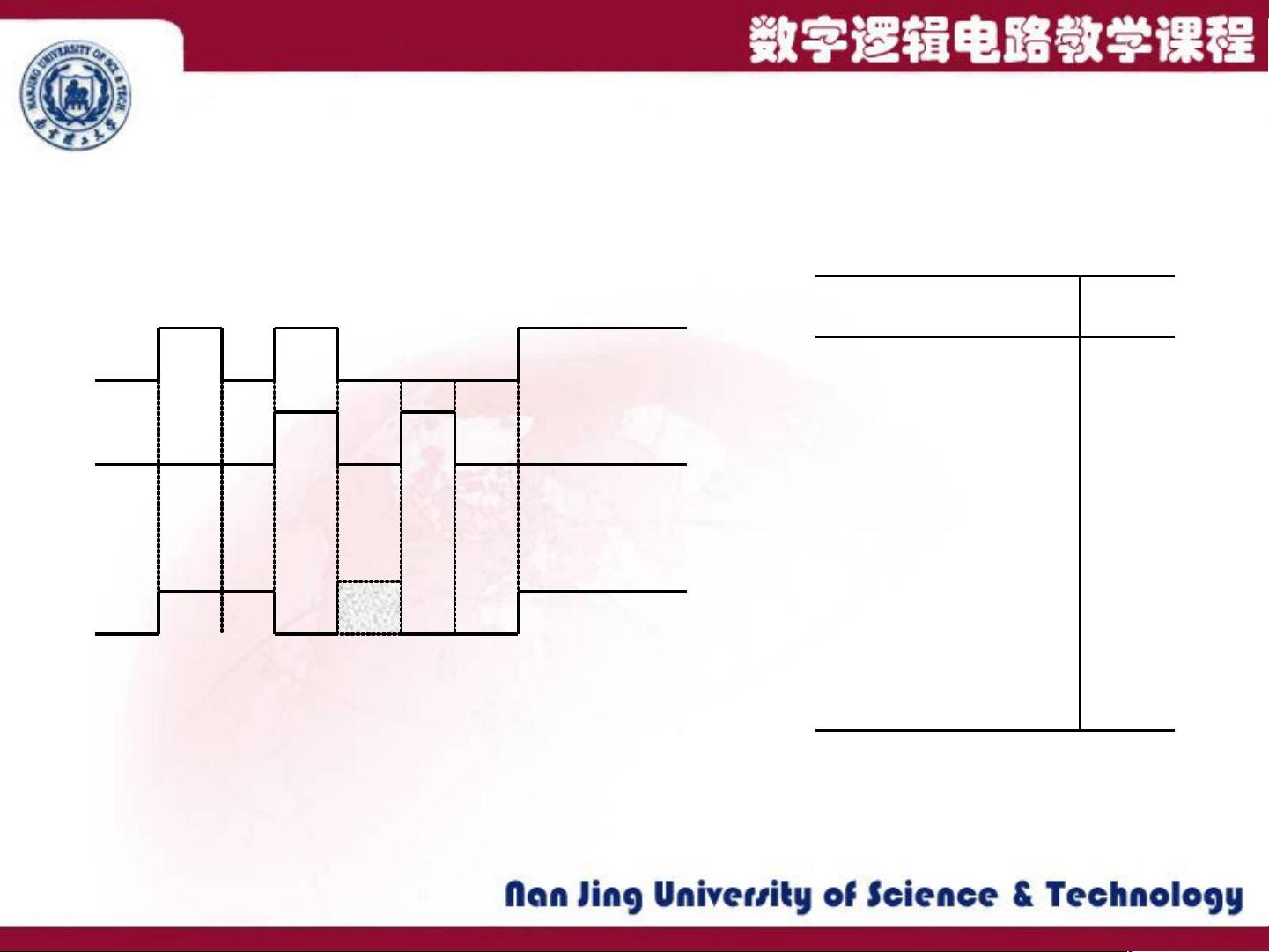

4. **时序图(定时波形图)**:绘制出随时间变化的信号波形,有助于理解电路动态行为。

5.2.1 普通锁存器,如RS锁存器,是时序逻辑电路中的基本单元。RS锁存器有两个控制输入:置位端(SD)和复位端(RD)。其逻辑功能如下:

- 当SD=0且RD=1时,电路处于复位状态,Qn+1=0。

- 当SD=1且RD=0时,电路被置位,Qn+1=1。

- 当SD=0且RD=0时,如果没有额外的激励,Qn+1将保持当前状态Qn,这称为“保持”状态。

- 然而,当SD=1且RD=1时,电路状态不确定,通常这种情况应避免,因为这违反了RS锁存器的约束条件,即SD和RD不应同时为1。

RS锁存器由与非门(NAND gate)构建的例子展示了如何实现这些功能。在这种配置下,SD和RD的逻辑操作与上述逻辑分析相符,但实际应用中,SD=RD=1的条件应避免,以防止电路进入不确定状态。

时序逻辑电路是数字系统设计的基础,它们在计算机内存、微处理器以及各种数据处理设备中扮演着关键角色。理解其工作原理和描述方法对于设计和分析复杂的数字系统至关重要。

107 浏览量

2021-09-21 上传

2021-09-21 上传

2022-06-16 上传

2021-09-21 上传

2022-06-17 上传

2025-03-12 上传

智慧安全方案

- 粉丝: 3861

最新资源

- NesEmulator: 开发中的Java NES模拟器

- 利用MATLAB探索植物生长新方法

- C#实现条形码自定义尺寸生成的简易方法

- 《精通ASP.NET 4.5》第五版代码完整分享

- JavaScript封装类实现动态曲线图绘制教程

- 批量优化图片为CWEPB并生成HTML5图片标签工具

- Jad反编译工具:Jadeclipse的下载与安装指南

- 基于MFC的图结构实验演示

- Java中的邮件推送与实时通知解决方案

- TriMED方言技术的最新进展分析

- 谭浩强C语言全书word版:深入浅出学习指南

- STM32F4xx开发板以太网例程源码解析

- C++实现的人力资源管理系统,附完整开发文档

- kbsp_schedule:实时监控俄技大IKBiSP项目日程变更

- Seqspert: 提升Clojure序列操作性能的高效工具

- 掌握Android反编译:jdgui、dex2jar、apktool工具应用