高速电路板设计指南:信号完整性和材料选择

需积分: 10 170 浏览量

更新于2024-07-31

收藏 1.4MB PDF 举报

"AD_高速电路板布板指南"

在高速电路设计中,印刷电路板(PCB)的布板策略至关重要,特别是在使用如Altera器件这样具有高速I/O特性的集成电路时。随着技术的进步,器件引脚密度和系统工作频率不断提高,布板的复杂性也随之增加。为了确保信号传输的效率和系统的稳定性,需要遵循一系列关键原则。

首先,电源管理是高速电路设计的基础。所有器件都需要电源滤波以减少噪声,并确保电源分布均匀,从而降低整个系统的噪声水平。这可以通过使用去耦电容和适当的电源层设计来实现。

其次,信号线的匹配是减少信号反射的关键。不匹配的线路可能导致信号质量下降,甚至引起错误的信号检测。匹配可以通过添加匹配网络,如串联电阻或电容,以及使用等长布线来实现。

并行线路间的串扰是另一个需要关注的问题。降低串扰可以通过采用差分信号、使用屏蔽层、增加线路间距或者采用低串扰布线策略来解决。此外,使用正确的布线规则和布线顺序可以有效减少相邻走线之间的相互影响。

地平面设计也是确保信号完整性的关键因素。减少地弹(ground bounce)现象可以防止信号质量受到噪声的影响。优化的地平面布局应该能提供一个低阻抗的返回路径,以减小信号线上的电压波动。

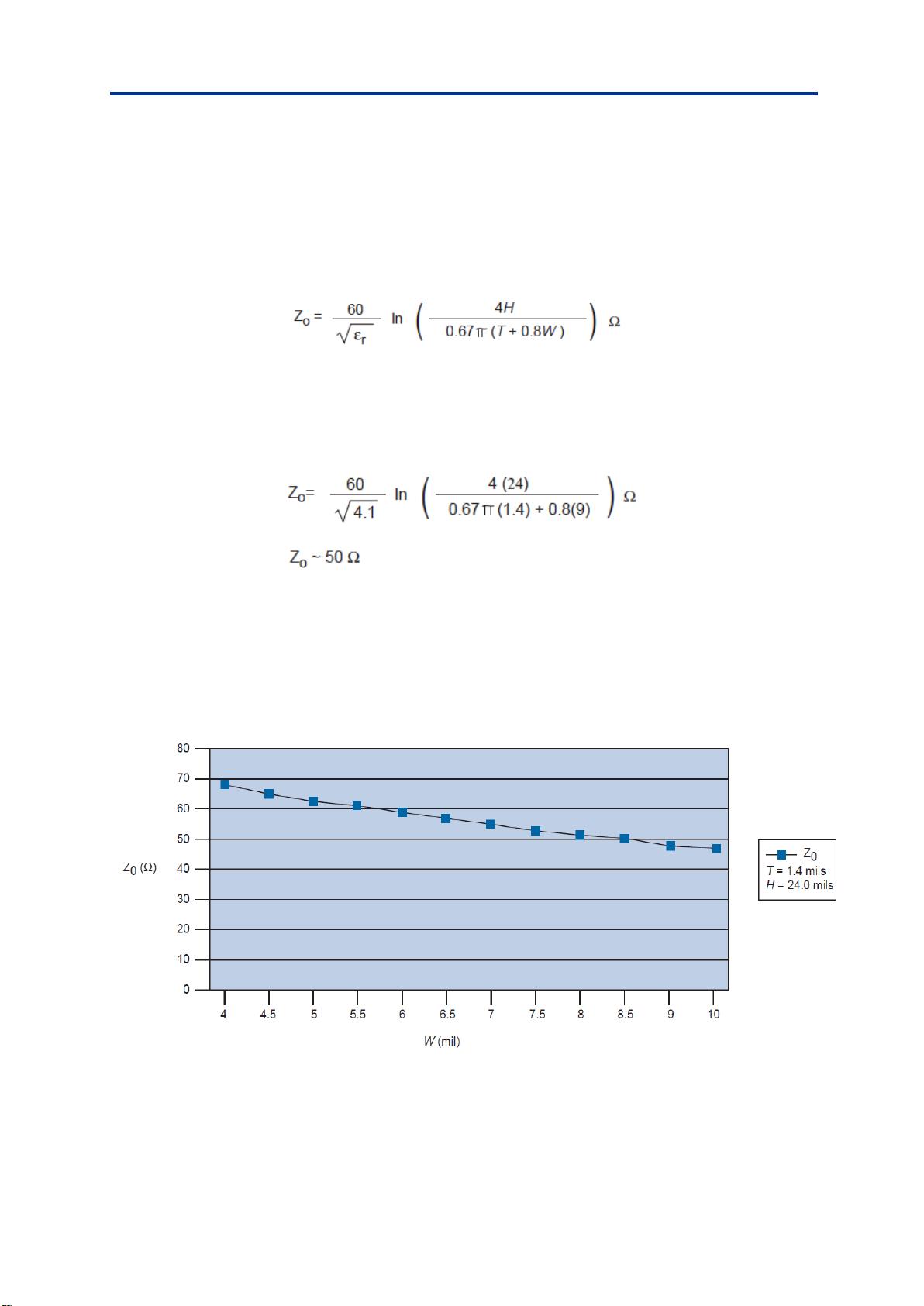

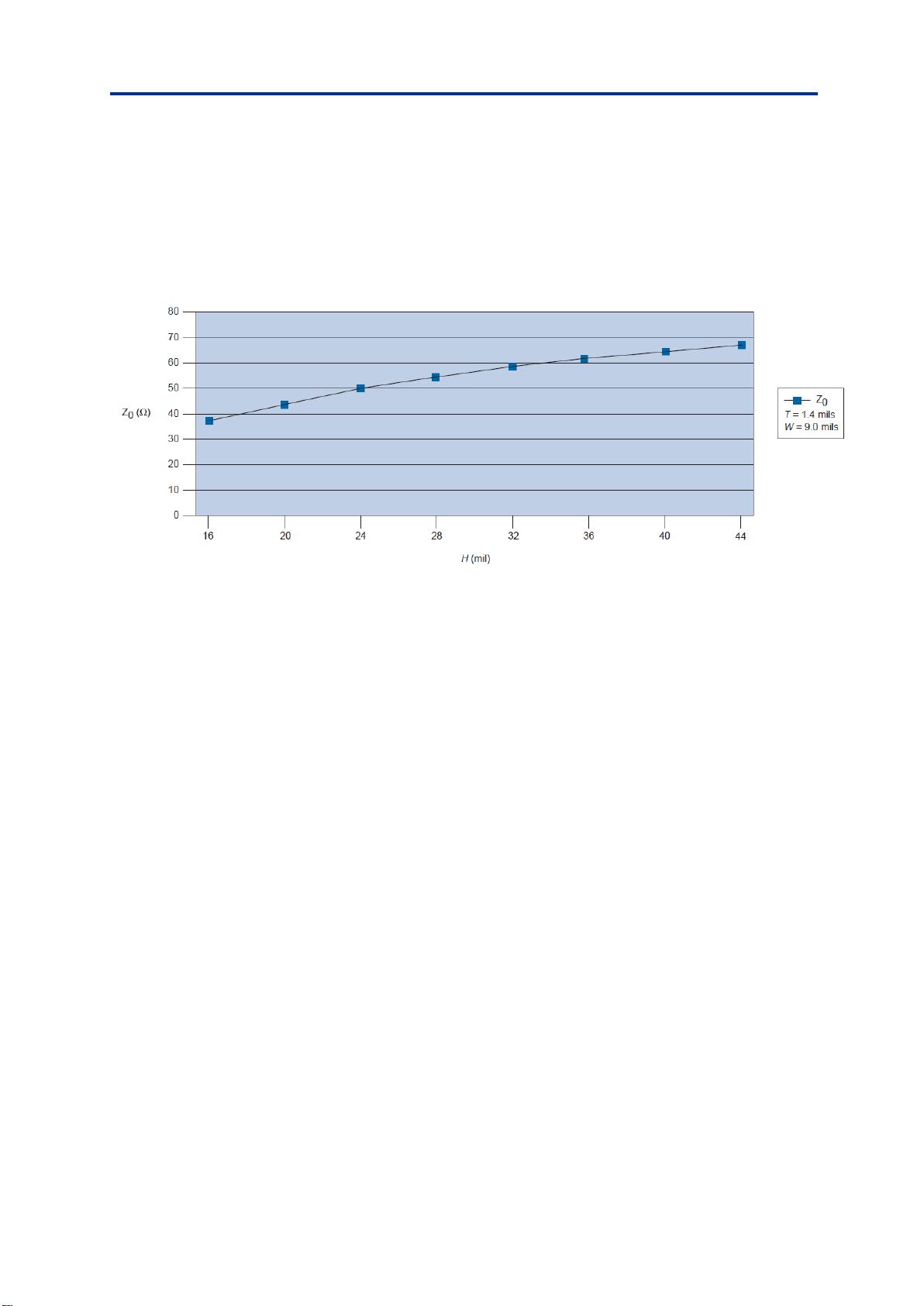

阻抗匹配是高速电路设计中的核心概念,尤其是在处理高速I/O标准时。正确匹配传输线的阻抗可以避免反射,保持信号的完整性。阻抗匹配通常通过调整线路的宽度、厚度以及介质层的厚度来实现。

传输线的选择和设计对于高速信号的传输至关重要。不同的材料,如FR-4和GETEK,具有不同的相对介电常数(εr)和损耗因数。较低的εr使得信号传输速度更快,而损耗因数决定了材料对高频信号的吸收程度。例如,FR-4的εr通常在4.1至4.5之间,而GETEK的εr在3.6至4.2之间,且GETEK的损耗因数可能更小,更适合高速应用。

此外,同步开关噪声(SSN)是高速电路中必须考虑的另一个因素。当多个开关元件在同一时刻切换时,可能会产生大的瞬态电流,导致电源噪声。控制SSN可以通过优化布局、使用缓冲器和分布式去耦电容等方式来减轻。

最后,电路板设计中还有许多其他的信号完整性技巧,如使用适当的过孔设计、避免尖角布线以减少电磁辐射、以及使用适当的层堆栈结构来管理信号层和电源/地层的关系。

设计高速电路板需要深入理解材料特性、传输线理论、信号匹配、电源管理、地平面设计以及信号完整性概念。通过这些综合策略,设计师可以创建出高效、可靠的高速电路板。

点击了解资源详情

点击了解资源详情

150 浏览量

167 浏览量

159 浏览量

148 浏览量

138 浏览量

238 浏览量

2024-04-27 上传

ly1910014346

- 粉丝: 0

最新资源

- 易二维码签到系统:会议活动签到解决方案

- Ceres库与SDK集成指南:C++环境配置及测试程序

- 深入理解Servlet与JSP技术应用与源码分析

- 初学者指南:掌握VC摄像头抓图源代码实现

- Java实现头像剪裁与上传的camera.swf组件

- FileTime 2013汉化版:单文件修改文件时间的利器

- 波斯语话语项目:实现discourse-persian配置指南

- MP4视频文件数据恢复工具介绍

- 微信与支付宝支付功能封装工具类介绍

- 深入浅出HOOK编程技术与应用

- Jettison 1.0.1源码与Jar包免费下载

- JavaCSV.jar: 解析CSV文档的Java必备工具

- Django音乐网站项目开发指南

- 功能全面的FTP客户端软件FlashFXP_3.6.0.1240_SC发布

- 利用卷积神经网络在Torch 7中实现声学事件检测研究

- 精选网站设计公司官网模板推荐