华为FPGA设计高级技巧详解

需积分: 9 75 浏览量

更新于2024-07-25

收藏 2.94MB PDF 举报

"FPGA设计高级技巧篇,是华为技术有限公司内部使用的一份教程,主要讲解Xilinx FPGA的设计策略和优化方法。这份资料共63页,涵盖了从基础的FPGA结构到高级的设计技巧,旨在帮助设计师提升FPGA设计的效率和性能。"

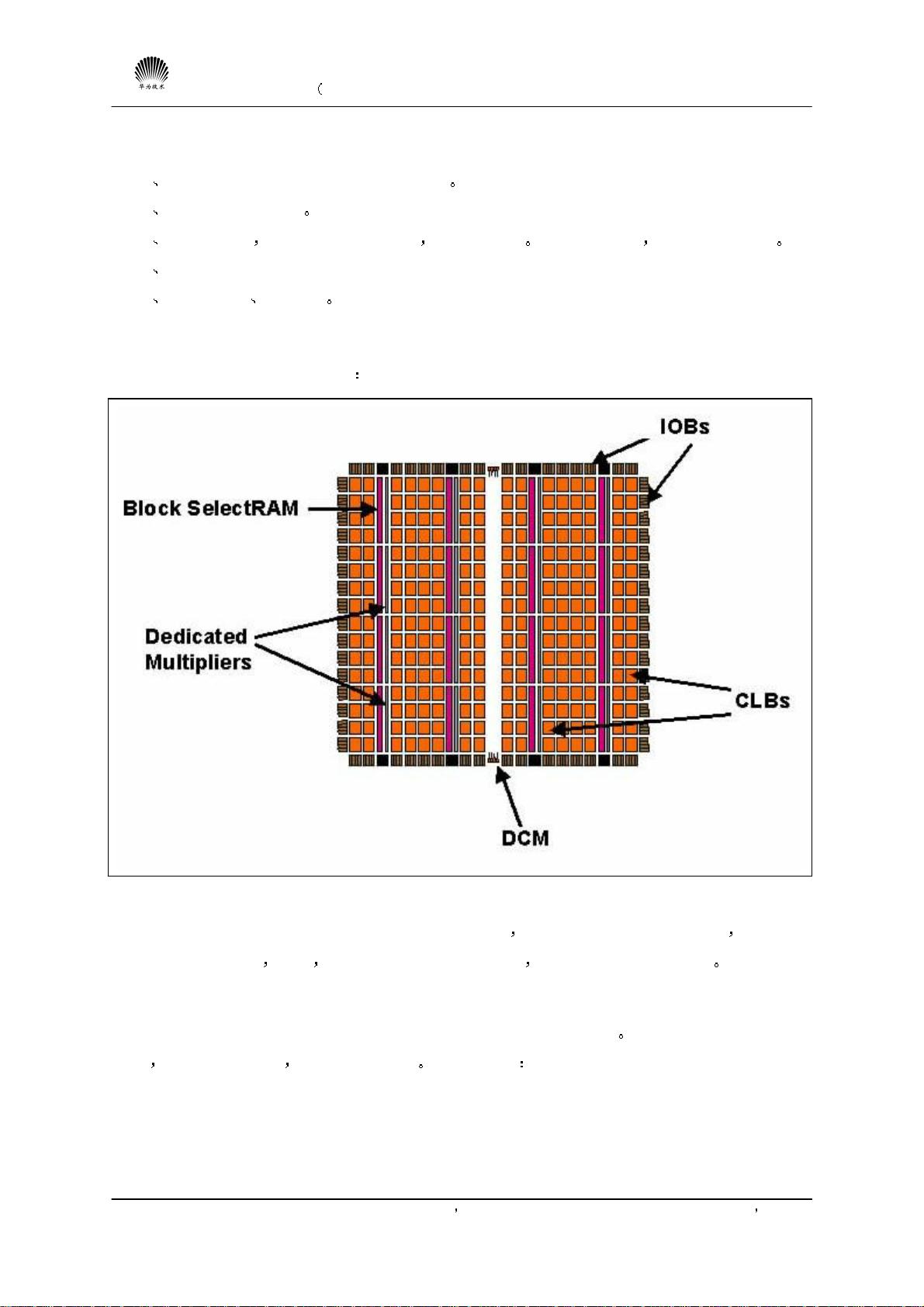

在FPGA设计中,理解基础架构至关重要。文档首先介绍了Xilinx Virtex II系列FPGA的基本结构,包括CLB(Configurable Logic Block), LUT(查找表),Slice,以及各种类型的存储资源如Distributed RAM和Block RAM。CLB是FPGA的基本逻辑构建单元,而LUT则用于实现组合逻辑功能。理解这些基本组件的工作原理有助于优化设计。

设计技巧部分强调了如何有效地利用FPGA资源。例如,合理选择加法电路,可以采用串行进位或超前进位方式来平衡速度和面积。使用括号处理多个加法器能减少逻辑级数,从而提高速度。此外,文档还讨论了如何配置LUT以实现更高效的组合逻辑电路,以及如何解剖并利用Block Select RAM的内部结构。

在时钟资源管理方面,文档提到了DCM(Digital Clock Manager)、CLKMUX和Global Clock等,这些都是确保系统时钟同步和高效运行的关键。了解如何正确使用这些时钟资源可以显著提升设计的时序性能。

对于I/O管理,文档详述了IOB(Input/Output Block)结构,以及如何通过DCI和SelectI/O进行灵活配置,以适应不同的接口需求。此外,乘法器资源的使用,如BlockRAM和分布式RAM的优化,也是提升设计性能的重要环节。

最后,文档还涉及了编码风格对设计的影响,比如对比ASIC结构和FPGA结构下的编码差异,以及如何利用FFX/FFY、SOP、CarryLogic、ArithmeticLogicGates、MUXFX、ShiftRegisterLUT(SRL)和LUT等基本逻辑元素来优化设计。

这份FPGA设计高级技巧篇为深入理解和优化Xilinx FPGA设计提供了丰富的指导,通过学习和应用这些技巧,设计师可以更好地发挥FPGA的潜力,实现更高效、高性能的数字系统设计。

2009-08-03 上传

2013-08-28 上传

2021-11-19 上传

2009-10-30 上传

点击了解资源详情

wanghw1003

- 粉丝: 5

- 资源: 13

最新资源

- ConcurrentStudy:Java并发编程和netty中学习加强相关代码

- 与一只巨大的鸡战斗至死:一场史诗般的最终幻想风格的战斗,对抗具有动态界面的 AI 控制的鸡:P-matlab开发

- Parstagram

- dsc字符串实验室在线ds-pt-090919

- UMLS-explorer

- txline,微带线计算工具

- OPPOR9S OPPOR9Splus原厂维修图纸电路图PCB位件图资料.zip

- stocks-chaser-frontend:库存跟踪应用

- 通过非线性导数进行边缘检测:这个简短的演示展示了一种有效的边缘检测算法。-matlab开发

- mariebeigelman.github.io

- AnoClient

- 开发基于JSP Servlet JavaBean的网上交易系统(JSP Servlet JavaBean Web Service

- Weather Forecast-crx插件

- go-jsonrpc-websocket.rar

- AM调制和解调研究:这个演示有助于研究和分析AM MOD和DEMOD。-matlab开发

- gocloud-secrets-awssecretsmanager