Verilog HDL教程:组合电路设计与三种描述方法详解

需积分: 1 190 浏览量

更新于2024-07-22

收藏 376KB PDF 举报

本教程是关于Verilog HDL(Hardware Description Language)的设计,这是一种广泛用于硬件描述语言的高级编程语言,主要用于描述数字逻辑电路的行为。Verilog被广泛应用于电子设计自动化(EDA)工具中,尤其是在系统级设计和集成电路(ASIC)设计中。

在第0.2章中,主要介绍了组合电路的设计方法,这是Verilog设计的基础。组合电路通常通过逻辑表达式、真值表和逻辑电路图来表示。逻辑表达式是一种简洁明了的方式来编写电路的功能,如例0.19所示的电路,其功能可以用`y = (~a && d) || (~a && ~b && c) || (~b && c && d) || (b && ~c && d)`这样的表达式来描述,其中`a`, `b`, `c`, `d`为输入,`y`为输出。

从真值表出发设计组合电路的方法是另一种实用技巧,通过枚举所有可能的输入情况和对应的输出结果来构建逻辑结构。例如,模块`prime`的代码展示了如何使用`always@(*)`语句和`case`结构根据输入`a`, `b`, `c`, `d`的不同组合设置输出`y`。这种方法强调了行为描述的重要性,每个输入状态都对应一个明确的输出响应。

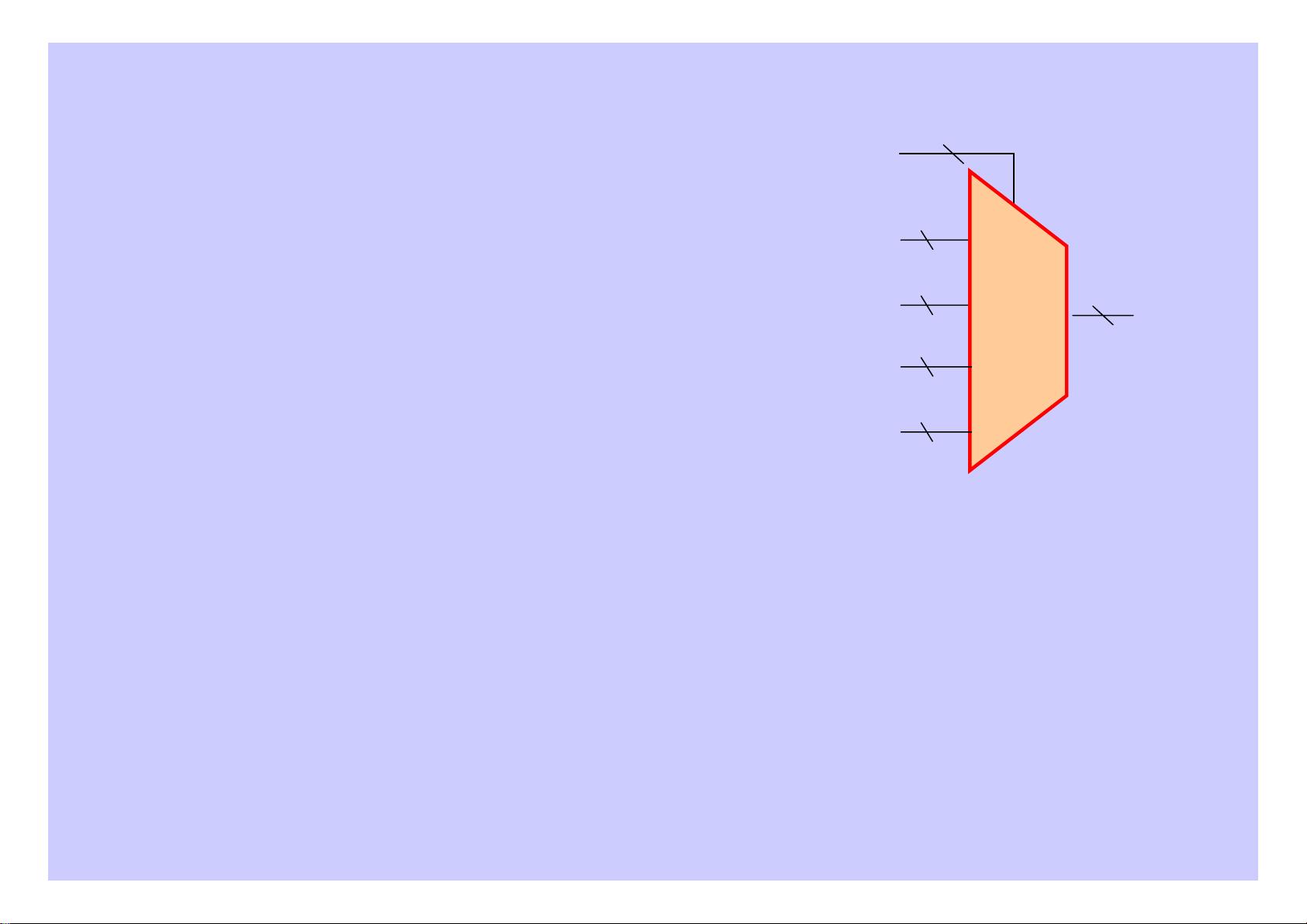

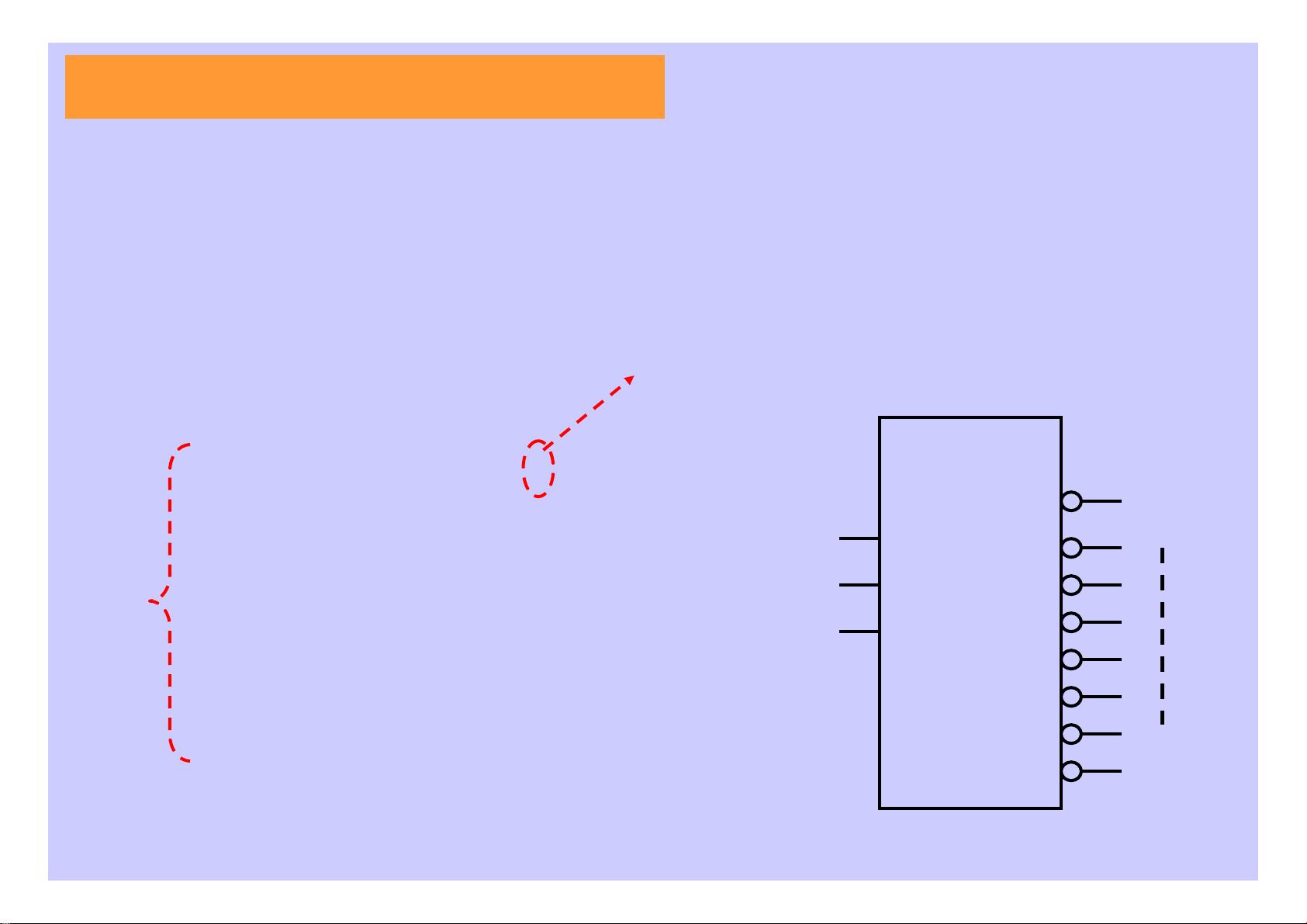

第三种方法是从电路图出发,这通常用于采用结构化描述,即先分解电路为更小的子模块(如非门、与门、或门等),然后将它们组合成整个电路。在示例中,非门(not)实例化为`notnot_a(na,a), not_b(nb,b), not_c(nc,c)`,这些非门的输出分别连接到后续的逻辑结构中,如`y0`, `y1`, `y2`, 和 `y3`,最后综合这些信号得到`y`的输出。

此外,本教程还提到了Verilog中的`input`、`output`、`wire`等关键字,以及`assign`、`reg`等信号声明方式,这些都是理解Verilog编程的基础概念。通过实例学习,读者可以掌握如何将电路原理转化为可编程的Verilog代码,以便在实际项目中进行硬件描述和验证。

总结来说,这个verilog开发教程深入浅出地讲解了如何通过三种不同的方式设计和实现组合电路,包括逻辑表达式、真值表驱动和基于电路图的结构化设计,同时涵盖了基础的Verilog语法和信号处理,为初学者和进阶者提供了实用的学习资源。

117 浏览量

2025-02-17 上传

2025-02-17 上传

PID、ADRC和MPC轨迹跟踪控制器在Matlab 2018与Carsim 8中的Simulink仿真研究,PID、ADRC与MPC轨迹跟踪控制器在Matlab 2018与Carsim 8中的仿真研

2025-02-17 上传

2025-02-17 上传

2025-02-17 上传

2025-02-17 上传

flashts

- 粉丝: 0

最新资源

- OpenGL实现旋转的glut代码教程

- Diagramos:一元逻辑公式证明工具的应用介绍

- Spring Security 2.0.4 完整包及源码下载

- 雪球用户数据爬取及多维数据集导入教程

- MARC2015实例教程第5-6-9章节及常见问题解析

- Qt与Matlab混合编程实现加法教程及文件下载

- PHP分页类实现数据库操作教程

- 基于MSP430F149实现的12864显示屏简便串口通信

- HashUtil:简易校验和哈希计算器工具使用指南

- PHPUnit代码测试库dbunit下载与应用

- C#实现调用本机摄像头及截图操作

- 高中生Santhosh探索自动化、AI与TensorFlow学习之路

- C#实现24路舵机控制板编程及USB通信

- 银行家算法在vc++环境下的实现教程

- 探索 Maven Findbugs 插件在 Java 开发中的应用

- RecruitHerd Mini-crx插件: 招聘软件解决方案的简化版