"FPGA实现的多功能数字钟设计及实现(基于VHDL语言)"

版权申诉

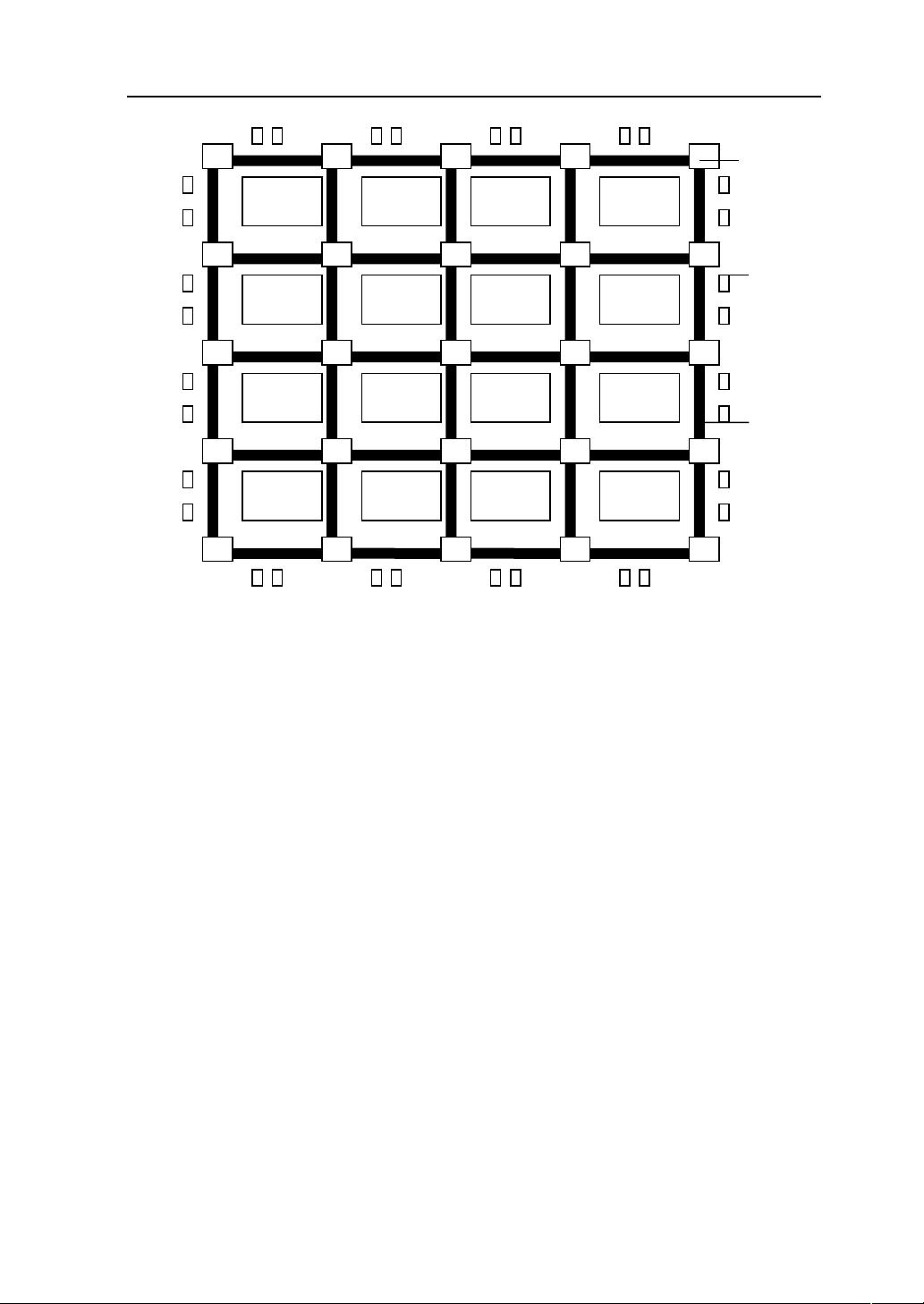

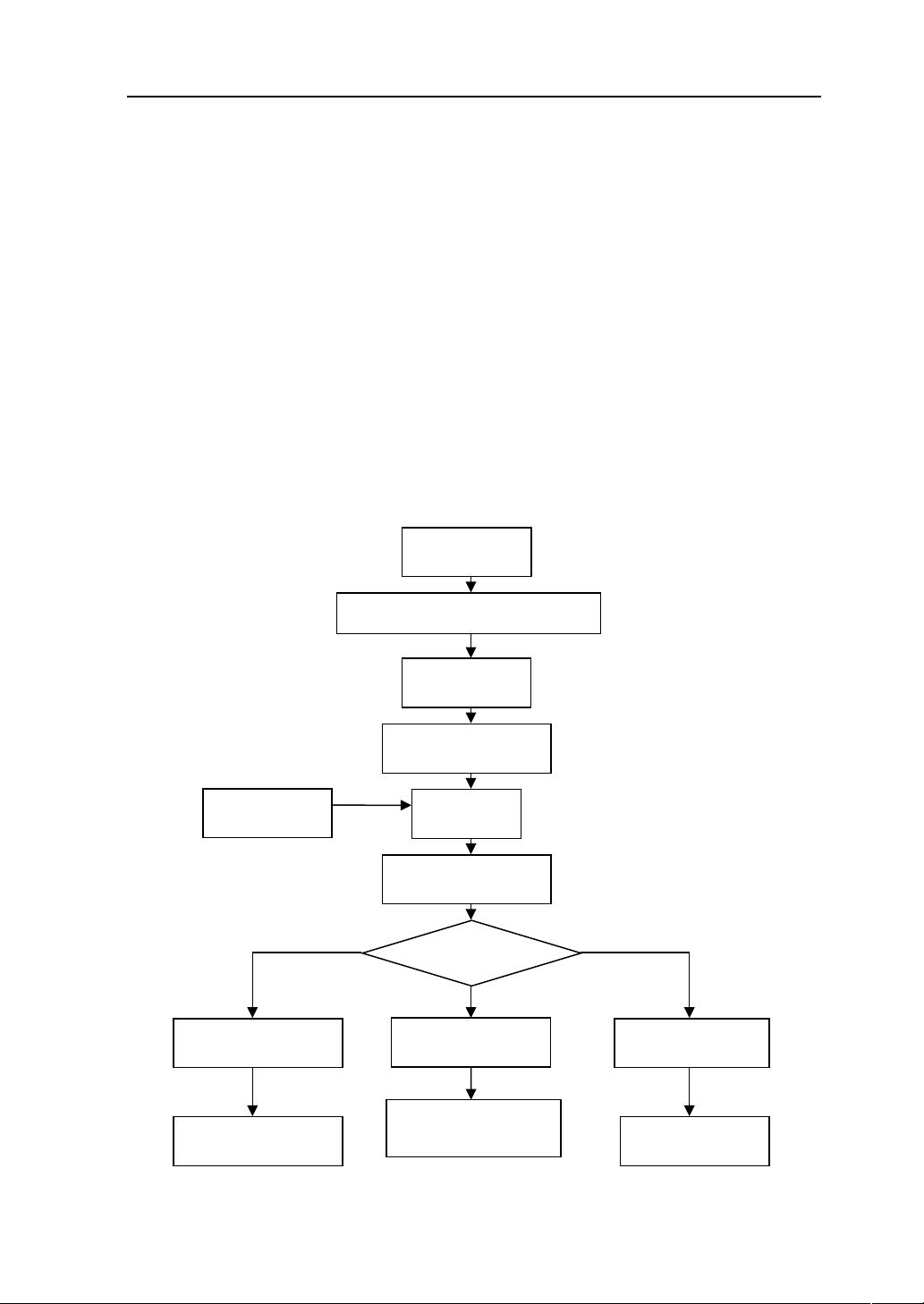

Based on the VHDL language and implemented on FPGA, this design utilizes EDA technology to create a digital clock system. Using a top-down design approach in the MaxplusII software environment, various basic modules are integrated to form the clock system, which consists of a clock module, control module, timing module, data decoding module, display module, and timekeeping module. The EP1K100QC208-3 chip is used to execute the program, allowing for the display of year, month, day, hours, minutes, and seconds, along with features such as setting the clock, resetting it, and starting and stopping it via keyboard input. Through compilation and simulation, the program is downloaded onto a programmable logic device for verification. This system effectively demonstrates the functionality of a digital clock and showcases the capabilities of hardware description languages, FPGA technology, and keyboard interfaces.

7941 浏览量

2024-04-16 上传

216 浏览量

323 浏览量

2021-10-04 上传

2021-09-30 上传

2023-06-20 上传

zzzzl333

- 粉丝: 818

最新资源

- C++ STL编程指南:设计组件解析

- 网站数据加密技术解析:DES、三重DES与RSA算法

- 单片机实验:LED闪烁灯实现与延时程序设计

- ABAP开发中常见问题及表结构查询方法

- RESTful HTTP应用实践与关键原则解析

- Java初学者指南:抽象类与接口解析

- CA3140A高增益运算放大器:集成MOSFET与双极晶体管的高性能解决方案

- 提升效率:Eclipse快捷键大全

- ActionScript 3.0 动画基础教程:从入门到精通

- AVR单片机实现的数字式SF6气体密度继电器设计

- ViSAGE:社会群体演化模拟与分析虚拟实验室

- Spring整合Struts与Hibernate:业务系统开发实践

- ActionScript 3.0 Cookbook 中文版:权威指南

- 信息技术在教务管理中的应用:Visual Basic6.0环境下的学生管理系统

- DIV+CSS学习难点实战经验梳理

- EJB设计模式解析:门面模式的应用与优势