Verilog HDL华为内部培训教程:基础语法与建模

需积分: 3 154 浏览量

更新于2024-07-31

收藏 687KB PDF 举报

"这是一份华为内部的Verilog HDL入门教程,主要涵盖了Verilog的基本语法、建模方式和一些关键概念。"

这篇教程是针对Verilog HDL的学习者,特别是对于那些在华为工作或者对华为内部培训有兴趣的人非常有价值。Verilog HDL是一种广泛用于数字系统设计的硬件描述语言,它允许工程师以结构化、行为和数据流的方式描述硬件。

教程从基础开始,讲解了Verilog HDL的基本语法,包括标识符的定义、关键词、书写规范建议以及注释的使用。这些基础知识是编写任何Verilog代码的起点。接着,教程深入到数据类型,区分了线网类型和寄存器类型,并介绍了常量和数字值集合的概念。

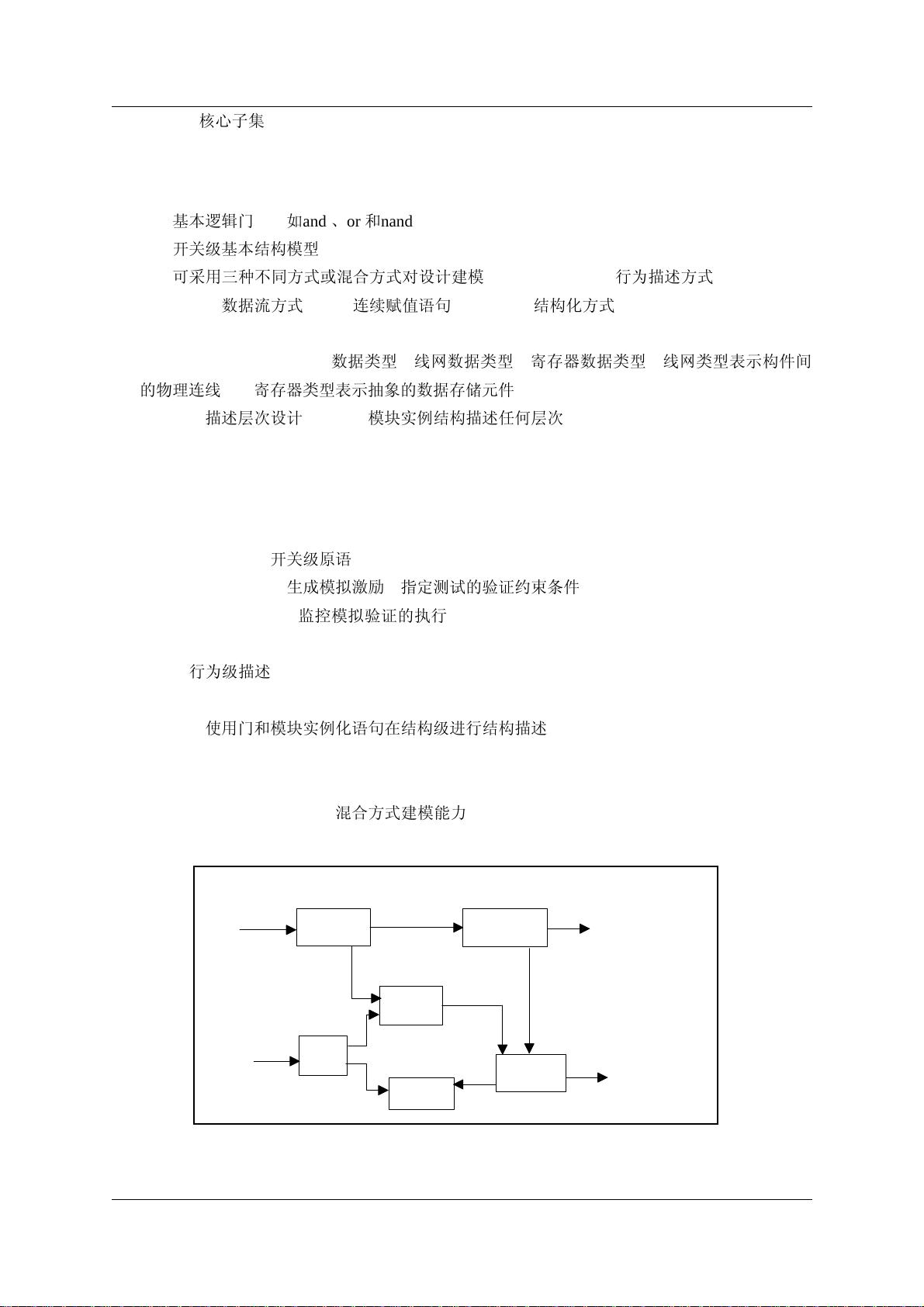

在建模部分,教程详细阐述了三种建模方式:结构化描述(描述硬件的并行行为)、数据流描述(基于运算符的连续赋值)和行为描述(基于事件驱动的过程)。这些建模方式让设计者能够灵活地表达数字系统的不同层面。

运算符和表达式的使用在教程中占据了重要位置,包括算术运算符、逻辑运算符、按位逻辑运算符、条件运算符以及case语句和条件语句,这些都是构建复杂逻辑功能的关键工具。此外,教程还提到了连接运算符,这对于组合信号和创建大型数据对象非常有用。

在建模的具体实例中,教程介绍了顺序语句块、过程赋值语句以及行为建模的用法,这些都是实现动态行为和控制流程的核心。同时,教程还涉及到了时延的概念,这对于理解硬件执行的时间特性至关重要。

此外,教程还包含了一些习题,帮助学习者巩固知识,并且列出了Verilog的保留字,以避免在编写代码时与预定义的关键字冲突。最后,它还讨论了其他一些相关方面,如行为建模的具体实例,展示了如何将理论知识应用到实际设计中。

这份教程为初学者提供了全面的Verilog HDL入门指导,涵盖了从基本语法到高级建模技术的各个方面,是深入理解和掌握这一硬件描述语言的良好起点。对于想要在华为或者其他任何使用Verilog进行设计的公司中提升自己技能的工程师来说,都是非常有价值的资源。

271 浏览量

583 浏览量

2009-11-20 上传

107 浏览量

113 浏览量

128 浏览量

点击了解资源详情

179 浏览量

2023-07-25 上传

Jayshier

- 粉丝: 0

最新资源

- Web远程教学系统需求分析指南

- 禅道6.2版本发布,优化测试流程,提高安全性

- Netty传输层API中文文档及资源包免费下载

- 超凡搜索:引领搜索领域的创新神器

- JavaWeb租房系统实现与代码参考指南

- 老冀文章编辑工具v1.8:文章编辑的自动化解决方案

- MovieLens 1m数据集深度解析:数据库设计与电影属性

- TypeScript实现tca-flip-coins模拟硬币翻转算法

- Directshow实现多路视频采集与传输技术

- 百度editor实现无限制附件上传功能

- C语言二级上机模拟题与VC6.0完整版

- A*算法解决八数码问题:AI领域的经典案例

- Android版SeetaFace JNI程序实现人脸检测与对齐

- 热交换器效率提升技术手册

- WinCE平台CPU占用率精确测试工具介绍

- JavaScript实现的压缩包子算法解读