Verilog模块基础:接口与基本语法讲解

版权申诉

49 浏览量

更新于2024-07-03

收藏 1.62MB PPT 举报

本资源是关于电子电路设计训练中的数字部分,使用Verilog编程语言进行教学的第二讲——Verilog模块与基本语法。Verilog是一种硬件描述语言(Hardware Description Language),在电子设计自动化(EDA)领域中广泛应用,用于描述数字电路的行为。

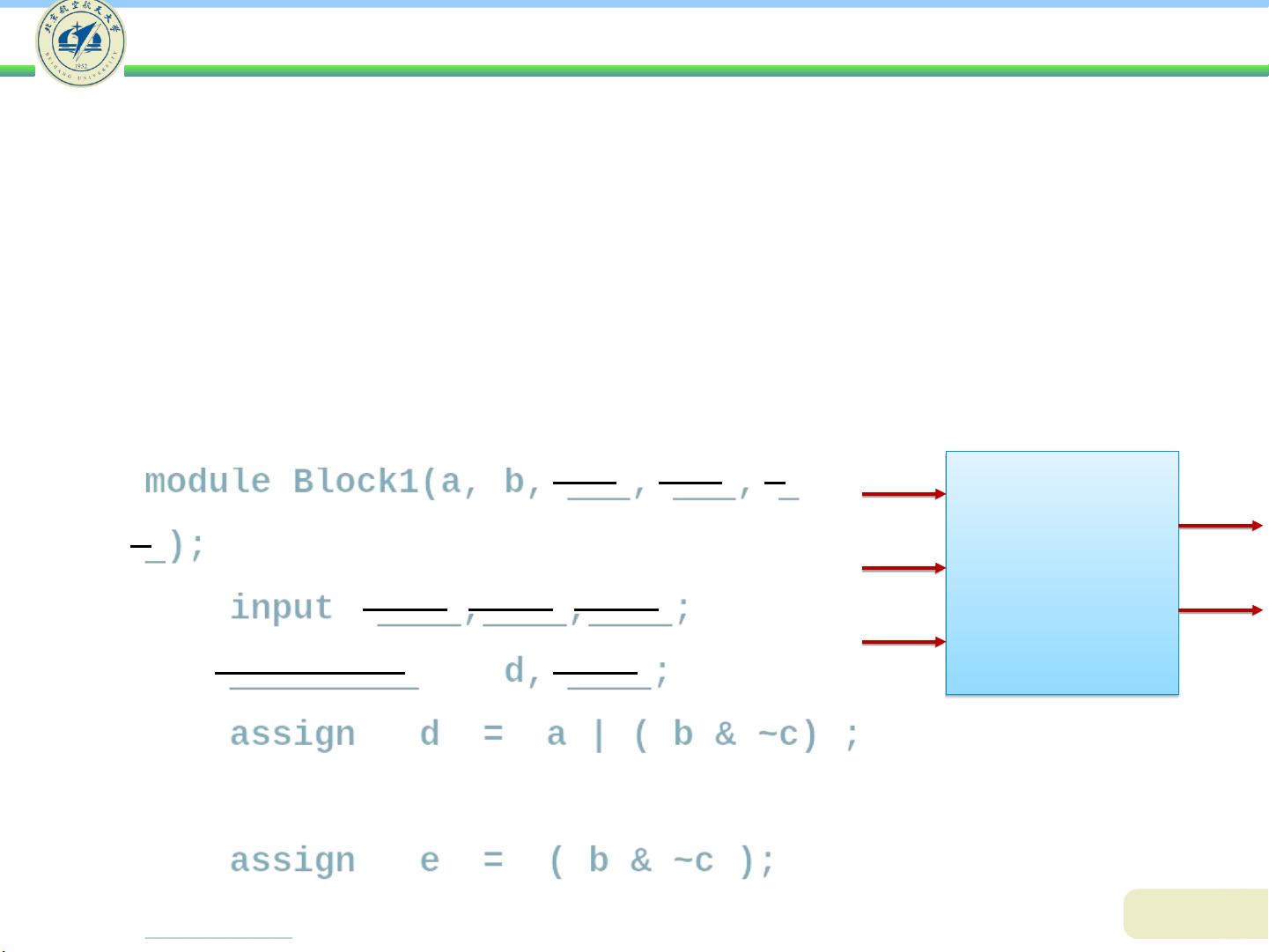

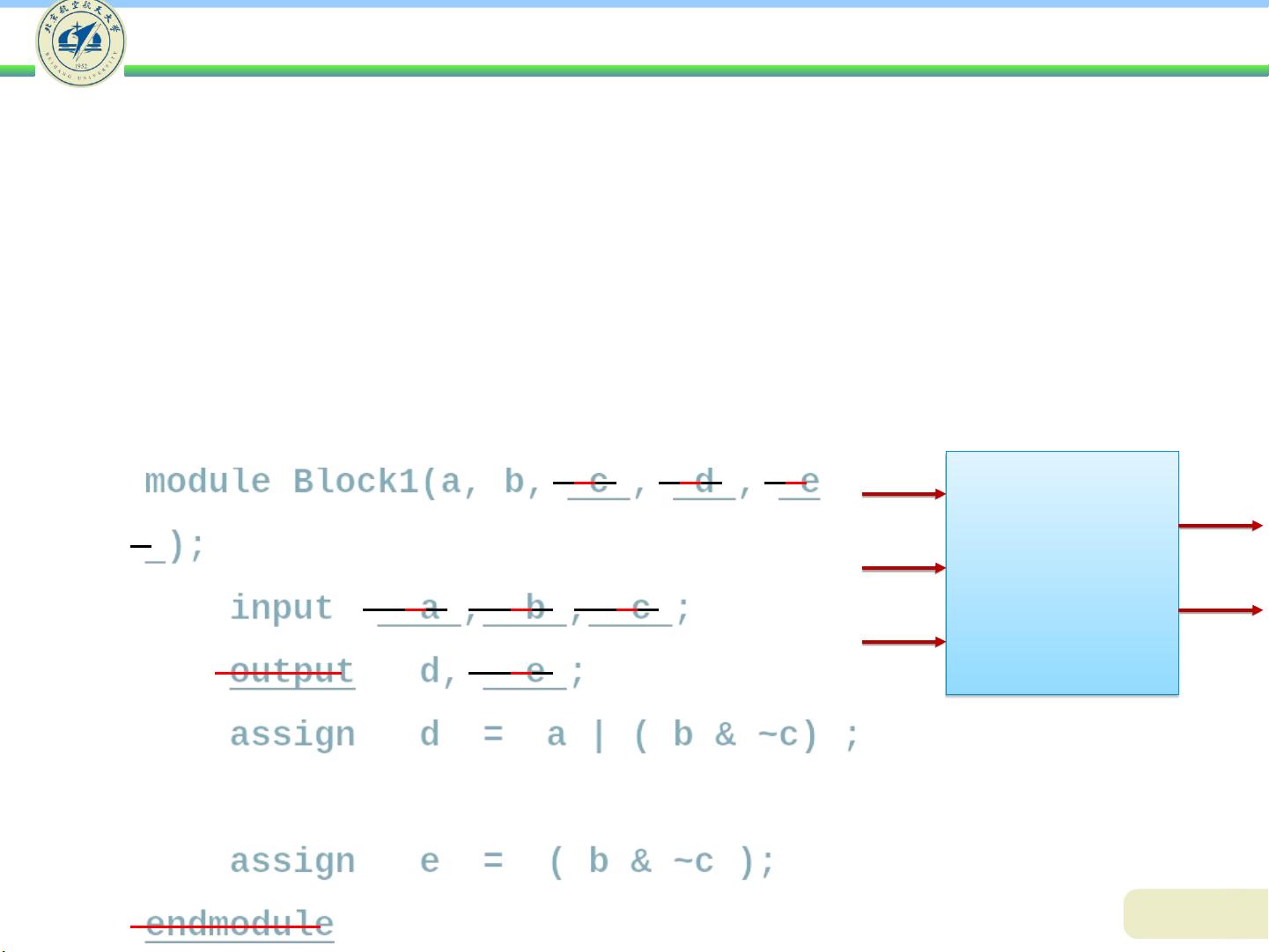

课程大纲首先介绍了Verilog语言的核心概念,强调了模块在设计中的重要性。模块是Verilog设计的基本单元,它由接口描述和逻辑功能实现两部分组成。模块定义中,使用`input`和`output`关键字来声明信号端口,如变量`a`和`b`作为输入,`c`和`d`作为输出。通过`assign`语句,明确定义了输入信号如何影响输出,如逻辑或`c = a | b`和逻辑与`d = a & b`。

电路图的框图在Verilog设计中起到可视化的作用,它映射到程序代码中的模块结构。模块内的设计包括端口声明,即电路符号的接口;I/O声明,明确输入、输出和双向信号;以及内部信号的数据类型定义。此外,课程还涵盖了连续赋值语句、行为描述语句(如`initial`和`always`),这些用于描述模块的行为模式。模块还可以包含任务(task)和函数(function)的定义,以及对低层次模块的实例化。

在模块结构中,`parameter`用于常量定义,`delay`块用于处理时间延迟,而`endmodule`则标志着整个模块的结束。通过学习这部分内容,学生可以掌握如何在Verilog中组织和构建复杂的数字电路设计,并理解如何将电路图的概念转化为可执行的程序代码。

这门课程的重点在于帮助学员掌握Verilog模块的构建和基础语法,以便他们在实际的电子电路设计中能够高效地应用这种高级编程语言。这对于电子工程师来说,是一项至关重要的技能,因为它允许他们描述和验证复杂的数字电路系统,提升设计的效率和准确性。

2021-09-24 上传

2020-04-30 上传

2021-09-21 上传

2010-04-23 上传

2022-06-18 上传

智慧安全方案

- 粉丝: 3795

- 资源: 59万+

最新资源

- 明日知道社区问答系统设计与实现-SSM框架java源码分享

- Unity3D粒子特效包:闪电效果体验报告

- Windows64位Python3.7安装Twisted库指南

- HTMLJS应用程序:多词典阿拉伯语词根检索

- 光纤通信课后习题答案解析及文件资源

- swdogen: 自动扫描源码生成 Swagger 文档的工具

- GD32F10系列芯片Keil IDE下载算法配置指南

- C++实现Emscripten版本的3D俄罗斯方块游戏

- 期末复习必备:全面数据结构课件资料

- WordPress媒体占位符插件:优化开发中的图像占位体验

- 完整扑克牌资源集-55张图片压缩包下载

- 开发轻量级时事通讯活动管理RESTful应用程序

- 长城特固618对讲机写频软件使用指南

- Memry粤语学习工具:开源应用助力记忆提升

- JMC 8.0.0版本发布,支持JDK 1.8及64位系统

- Python看图猜成语游戏源码发布