RS与SR触发器详解:逻辑功能与分类

需积分: 4 40 浏览量

更新于2024-07-21

3

收藏 7.72MB PPT 举报

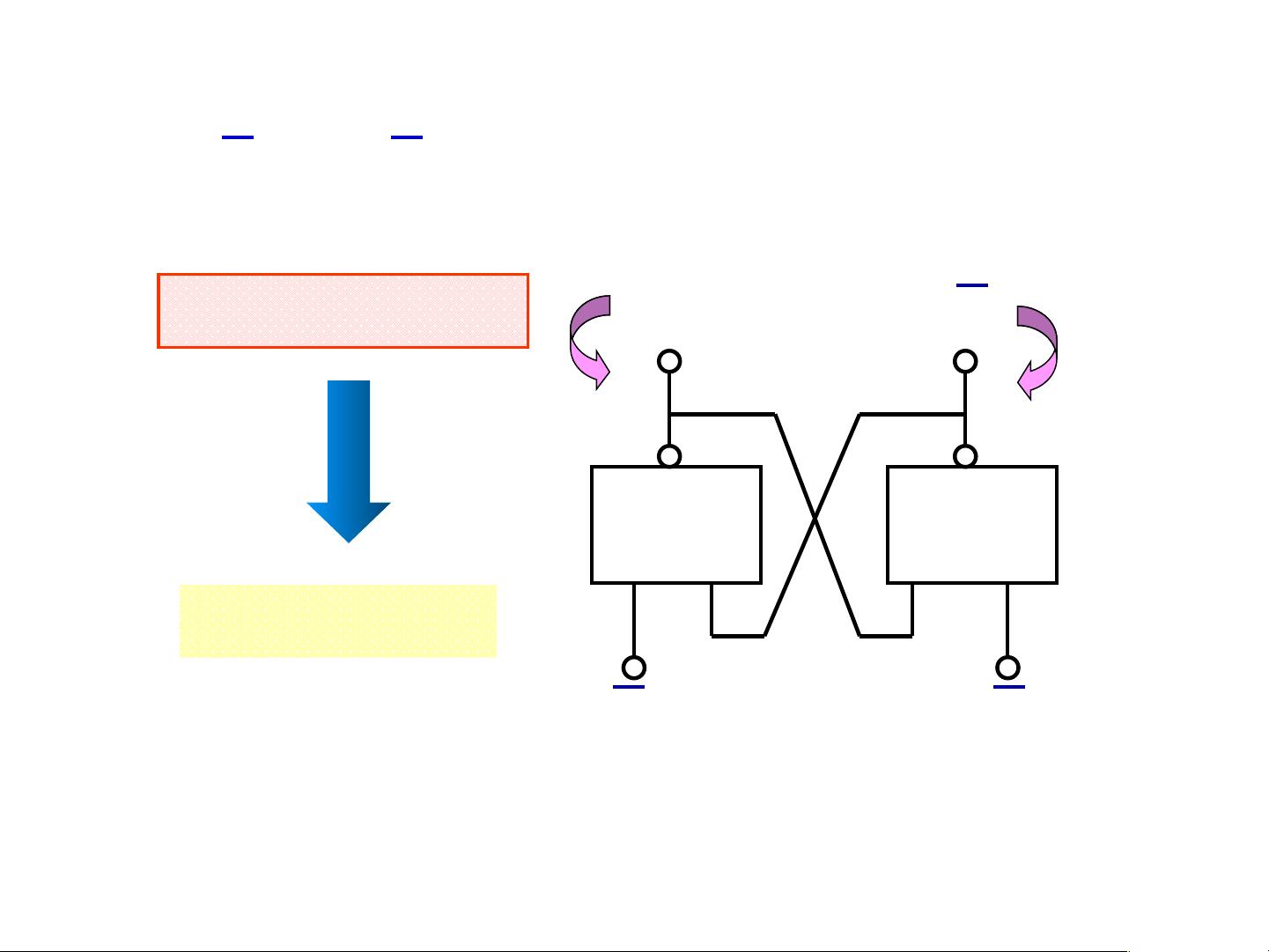

本资源详细介绍了RS触发器和SR触发器在时序逻辑电路中的核心地位。触发器作为构成时序逻辑电路的基础单元,其主要特点是具有记忆功能,能够存储一位二进制数码,并在适当条件下维持稳定状态(0和1)并进行状态转换。触发器根据触发方式可以分为电平触发、边沿触发和脉冲触发。

首先,SR触发器(Set-Reset触发器)是一种基本的逻辑门电路组合,包括由或非门和与非门组成的两种类型。在正常情况下,两个互补输出端Q的状态保持相反,通过S(置位)和R(复位)输入控制触发器的状态变化。当S为1且R为0时,触发器从"1"态翻转到"0"态,反之亦然。这种触发器能够实现从一个稳定状态切换到另一个状态,并在输入信号消失后保持新状态。

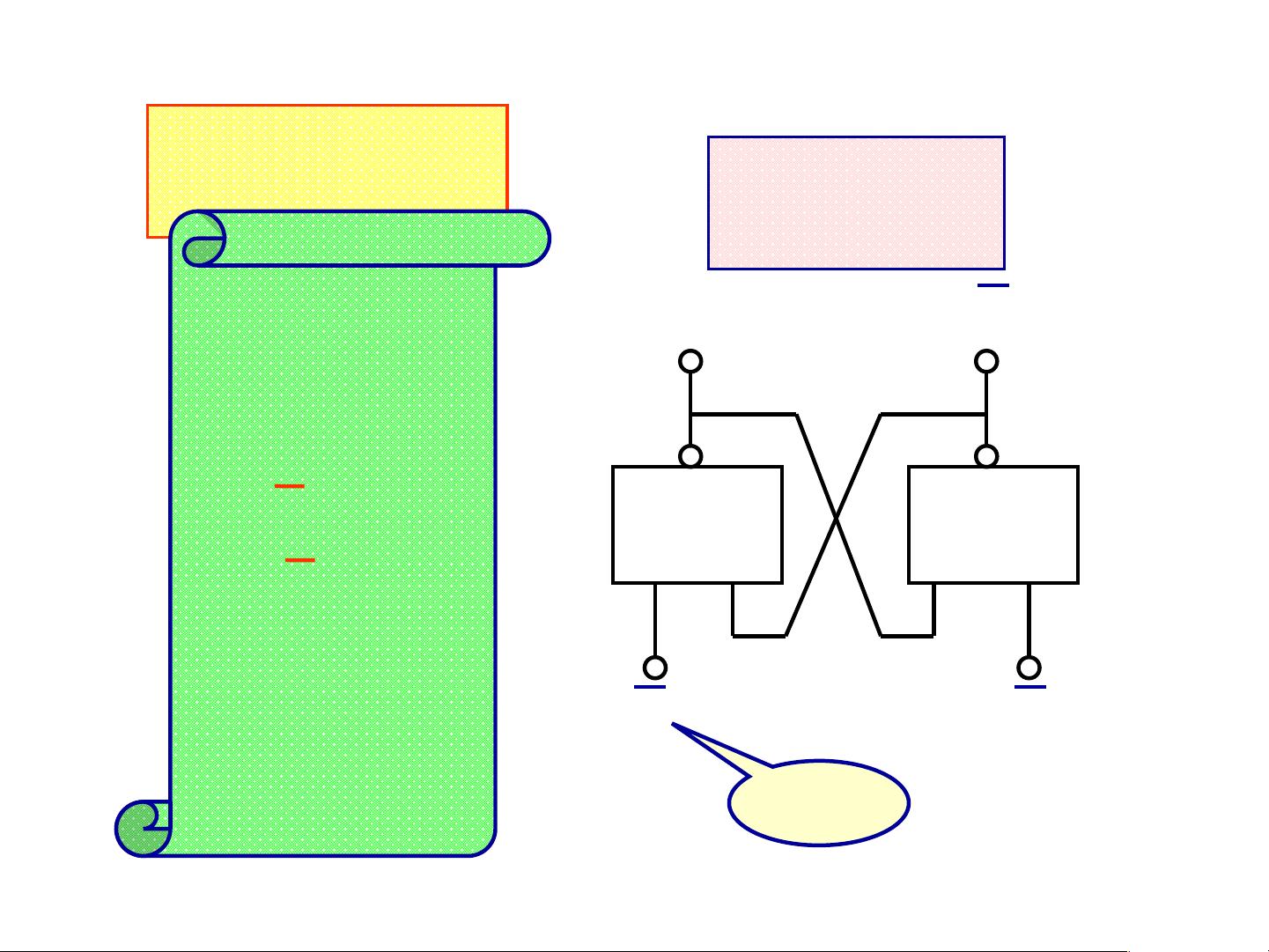

接着,讨论了JK触发器和D触发器,它们是根据逻辑功能进行分类的。JK触发器通常用于通用的逻辑设计,允许用户通过不同的输入组合进行状态切换,而D触发器则基于数据输入D决定当前状态,它在没有外部控制信号的情况下保持数据不变。

总结来说,RS触发器和SR触发器是基本的时序逻辑电路元件,它们在设计和理解数字系统中起着关键作用。理解这些触发器的工作原理和特性对于构建和调试复杂的时序电路至关重要。通过掌握它们,工程师可以灵活地创建各种时序逻辑电路,如计数器、寄存器和更复杂的逻辑功能。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2024-03-22 上传

2021-09-18 上传

2020-07-17 上传

2020-07-19 上传

2024-06-21 上传

2023-03-30 上传

pcdhacker

- 粉丝: 1

- 资源: 11

最新资源

- mp3-文件-

- mR-zUnnu

- C#-Leetcode编程题解之第22题括号生成.zip

- jquery打分评星级效果

- bootstrap-wysiwyg-notes:简易富文本编辑器bootstrap-wysiwyg原始注解,可用于学习富文本实现原理

- Mutilsim 设计一个串行数据检测电路. 当连续出现4个和4个以上的1时, 检测输出信号为1, 其余情况下的输出信号为0

- online-vet-clinic:基于Spring宠物诊所项目的在线兽医诊所

- hyperdrive-network-speed:跟踪Hyperdrive存档上的上传和下载速度

- git-github的

- original

- 5953281,c语言源码反码补码转换,c语言

- uniapp + vue3 +vite + ts + pinia 框架模板

- LeisureConstructionWebsite:leisureconstruction.com PHPSlim Restful网站源代码-Source website php

- Python库 | sqla_inspect-0.1.6.tar.gz

- 练习:练习会使您的大脑融化

- 蓝色手机APP应用开发网站模板