基于FPGA的数字示波器设计详解与关键参数

需积分: 5 186 浏览量

更新于2024-07-24

收藏 2.48MB PDF 举报

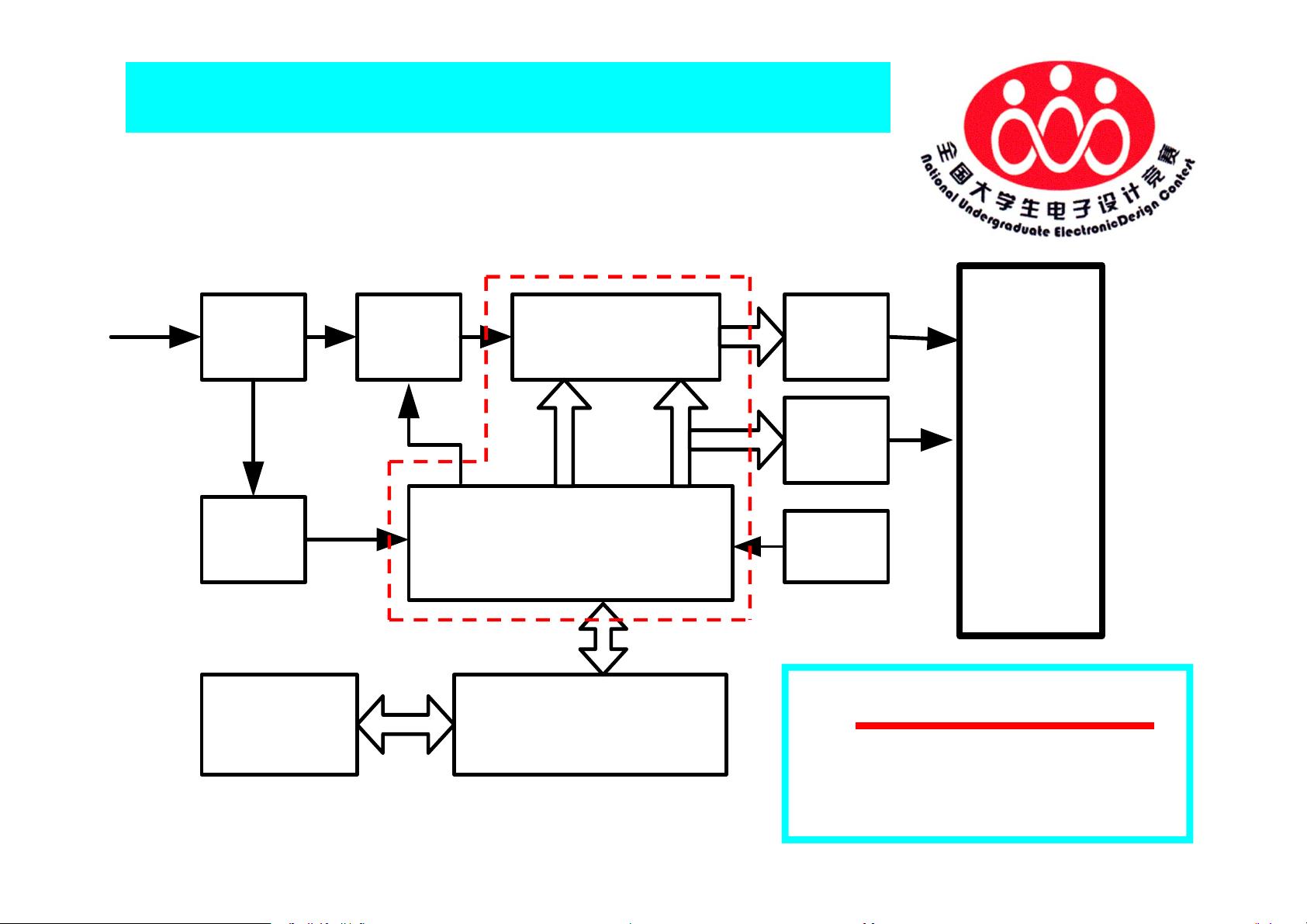

《数字示波器》作品解析深入探讨了一款结合了FPGA技术的实时数字示波器的设计过程。该作品旨在满足特定的技术指标,包括采样速率和分辨率,以实现对电信号的有效捕捉和可视化。

首先,题意分析是关键步骤。参赛者需要理性的评估,确定主要指标,如采样速率,它是衡量示波器性能的重要参数。根据采样定理,对于10Hz至10MHz的频率范围,要求实时采样速率不超过1MSa/s,但为了保证波形的显示质量,同时支持等效采样速率高达200MSa/s,这需要设计高效的A/D转换器,并集成取样保持电路来确保数据的准确捕获。

A/D转换器是示波器的核心组件,其1MSa/s的最高采样速率限制要求设计师选择合适的芯片,并考虑如何实现独立的取样保持电路以克服可能的信号失真。同时,垂直分辨率设定为8位,意味着能够精细地量化电压信号,且设置有不同灵敏度档位,以适应不同应用场景下的测量需求。

显示部分可以选择通用示波器或者液晶显示器,这两种形式都涉及到不同的显示技术和接口设计。实时采样方式与等效采样方式之间的切换,以及扫描速度的不同设置,如20ms/div、2μs/div和100ns/div,确保了波形的动态范围和精确测量。

除了采样速率,频带宽度也是衡量示波器性能的关键,尽管题目强调了A/D转换器的最大速率,但频宽的设计需要综合考虑信号处理能力和显示器的响应特性,以确保不同频率信号的清晰显示。

在输入电路通道的设计中,输入信号的触发机制至关重要,包括触发电路TP的设计,确保能够精确地捕获和分析输入信号。对于低频段,如10Hz,噪声峰-峰值要求小于2mV,以防止误读或干扰。

《数字示波器》作品的完成不仅考验了参赛者的数字信号处理基础,还涵盖了硬件选型、电路设计、信号采样与保持、显示控制以及系统集成等多方面的技能。通过深入理解并实现这些要求,参赛者能够制作出功能强大且实用的数字示波器,适用于教学、科研和工程应用领域。

277 浏览量

333 浏览量

2022-05-04 上传

2024-04-28 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

taoyingjian

- 粉丝: 8

- 资源: 21

最新资源

- Homepare_App_1

- Cine-Data:使用TMDB API的电影搜索器和跟踪器

- brick:Brick Mag 原型

- 如何做好企业的培训(2个PPT)

- 企业大堂3D效果图模型

- 由Arduino提供支持的小吃自动售货机-项目开发

- dflex:JavaScriptJavaScript项目来操纵DOM元素

- Personal-Portfolio-Website:个人投资组合网站

- 集团管理及组织架构培训需求DOC

- color-file:根据模式和文件扩展名为迷你缓冲区中的文件着色

- Visual-Web:用于HTML,CSS和TypeScriptJavaScript的可视工具

- 电力设备新能源年月投资策略国内需求拉动下半年增长电网投资加速-36页.pdf.zip

- jdk-8u151-x64.zip

- doodle-jump

- OpenWrt-Newifi_D2:OpenWrt-Newifi_D2

- Spherium:运用 OpenGL 的力量,创造菊石、克莱因瓶和好奇的球体!-matlab开发