高速数字电路设计:时钟振荡器与晶振分析

需积分: 3 193 浏览量

更新于2024-07-31

收藏 388KB PDF 举报

"高速数字电路设计教材-华为-黑魔手册翻译版-12"

本章节专注于高速数字电路设计中的核心组件——时钟振荡器,特别是壳式晶振的介绍。时钟振荡器是电子系统中的心跳,对系统的稳定性和性能起着至关重要的作用。华为的这份教材详细讲解了相关知识,旨在帮助设计师更好地理解和应用。

12.1 壳式晶振

壳式晶振因其内部元件被密封在金属壳中而得名,通常采用厚膜集成电路技术制造。尽管现在有些新型产品使用塑料外壳替代金属壳,但壳式晶振仍然是现代数字设计的常见选择。压电石英晶体振荡器因其高精度常用于高品质数字设备,其时钟频率的微小变化相对于数字电路的延迟来说可忽略不计。

12.2 时钟抖动

时钟抖动是时钟信号中频率或相位的随机变化,可能导致数据传输错误。教材详细阐述了时钟抖动的成因、测量方法(包括时钟抖动的测量、电源噪声的测量)以及减少抖动的策略。时钟抖动对复杂的数字系统尤为重要,例如在两个独立时钟设备间的数据传输,可能需要高度精确的同步,否则会导致数据错误或FIFO的填充问题。

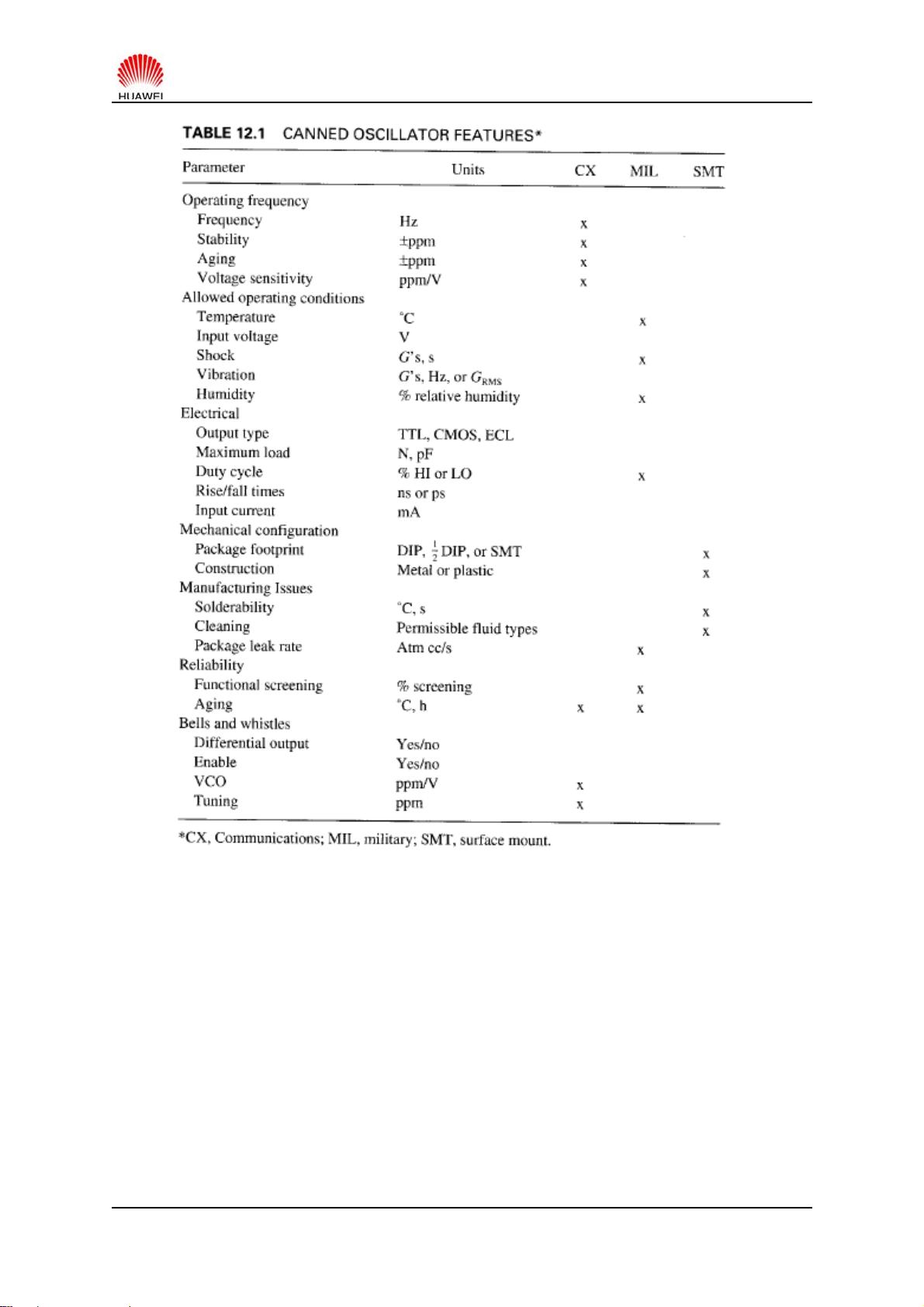

12.1.1 至12.1.7 晶振的参数和特性

教材还涵盖了壳式晶振的多个关键参数,如频率规范、正常工作条件、电气特性、机械封装、加工工艺、可靠性和振铃与偏移。这些参数决定了晶振的性能和适用场景。

12.2.1至12.2.4 时钟抖动的考虑

时钟抖动的测量包括何时需要考虑它以及如何通过滤波电路来降低抖动。时钟源的电源滤波是降低噪声和改善时钟质量的重要手段。

在高可靠性应用,如军事设备中,晶振可能需要经过特殊测试,以确保其能在振动、湿度、高温等恶劣条件下稳定工作。这些测试可能导致成本上升,但并非所有应用场景都需要如此高标准的晶振,商业级晶振通常能满足大部分非特殊需求,且价格更为亲民。

该教材详细解读了高速数字电路设计中时钟振荡器的关键概念和技术,对于设计者优化系统性能和选择合适的时钟组件具有极大的指导价值。

2009-11-08 上传

2011-07-03 上传

2011-07-03 上传

2011-07-03 上传

2011-07-03 上传

2011-07-03 上传

2011-07-03 上传

点击了解资源详情

点击了解资源详情

hanleiseu

- 粉丝: 16

- 资源: 26

最新资源

- BottleJS快速入门:演示JavaScript依赖注入优势

- vConsole插件使用教程:输出与复制日志文件

- Node.js v12.7.0版本发布 - 适合高性能Web服务器与网络应用

- Android中实现图片的双指和双击缩放功能

- Anum Pinki英语至乌尔都语开源词典:23000词汇会话

- 三菱电机SLIMDIP智能功率模块在变频洗衣机的应用分析

- 用JavaScript实现的剪刀石头布游戏指南

- Node.js v12.22.1版发布 - 跨平台JavaScript环境新选择

- Infix修复发布:探索新的中缀处理方式

- 罕见疾病酶替代疗法药物非临床研究指导原则报告

- Node.js v10.20.0 版本发布,性能卓越的服务器端JavaScript

- hap-java-client:Java实现的HAP客户端库解析

- Shreyas Satish的GitHub博客自动化静态站点技术解析

- vtomole个人博客网站建设与维护经验分享

- MEAN.JS全栈解决方案:打造MongoDB、Express、AngularJS和Node.js应用

- 东南大学网络空间安全学院复试代码解析