NXP Semiconductors

User Manual

for S32K1XX ADC Driver

for each pretrigger. This is why at least one of AdcGroupInBacktoBackMode and

AdcGroupUsesChannelDelays options needs to be configured for an Adc Group.

If both parameters are configured for the Adc Group, the user can configure a delay only

for the first channel conversion, and the rest will be converted in back to back mode.

If AdcGroupUsesChannelDelays is not configured for the group, the first channel will

have an associated delay of 0, and will convert immediately after the external trigger is

received.

2.6.5.2 AdcGroupUsesChannelDelays - Enable/Disable the usage of channel delays in

PDB pretriggers.

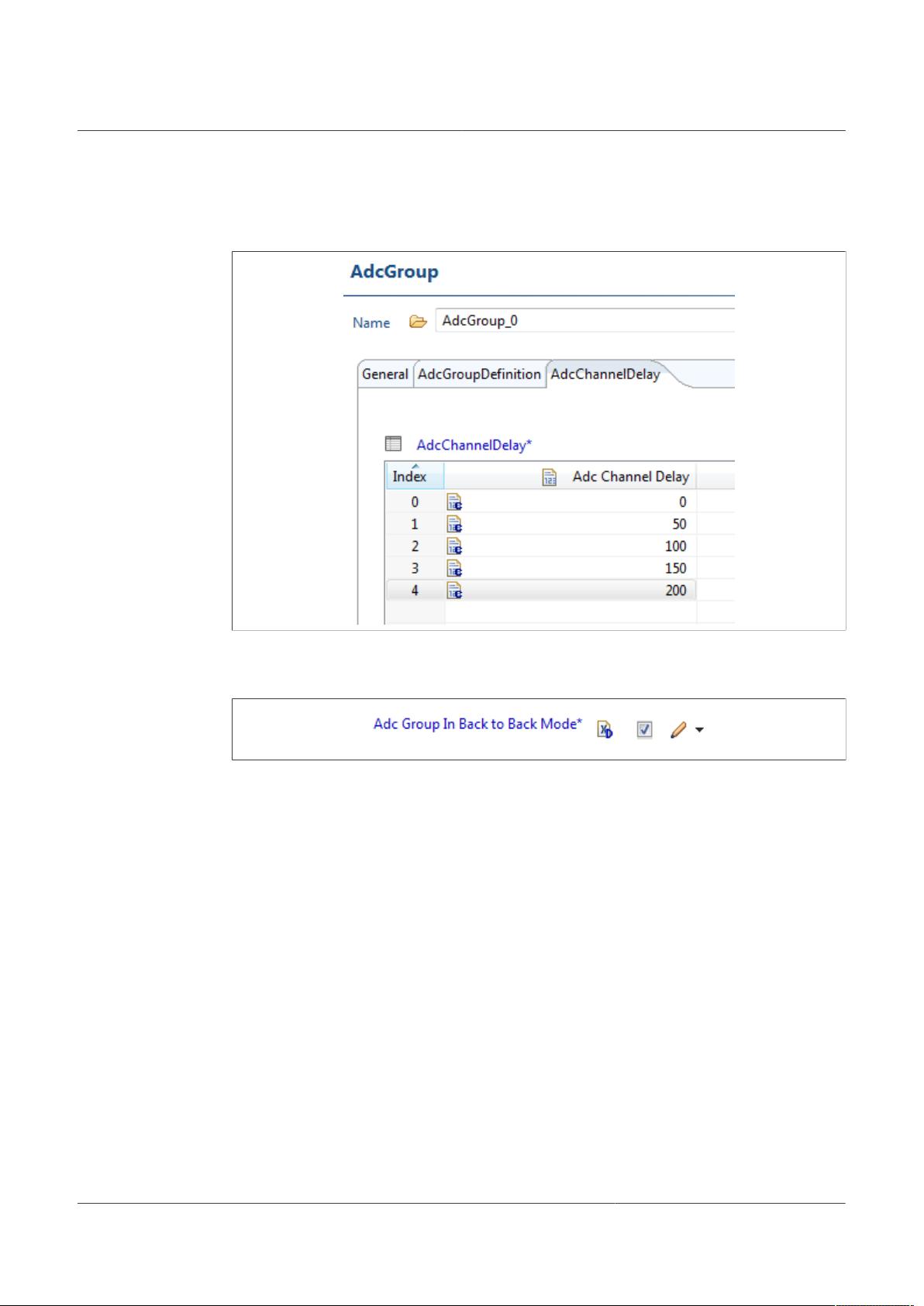

When this parameter is enabled, the PDB pretriggers will have individual delays

configured. PDB_CH1nDLYx will be set with the values configured in AdcChannelDelay

list for each channel. The values must not be equal or too close, otherwise PDB internal

errors will occur.

The Adc driver can convert only up to N channels at once, where N = number of PDB

Channels X 8 pretriggers each; for groups larger than that, Adc driver will split the group

in sub-groups of N and convert them with sub-group conversions. Interrupt processing is

needed between the sub-groups for register re-configuration. The timing of the channel

conversions will be accurate only for the first N channels; for the next ones, the on top of

the configured delay, the delay of previous conversions and interrupt processing will be

implicitly added. For this reason, it's safe co configure a delay of 0 for the N+1 channel.

But the delay values for each group of N need to be increasing, so that the channel

conversions occur in the order they were defined in the group.

If AdcGroupInBacktoBackMode is also configured for the Adc Group, the user can

configure a delay only for the first channel conversion, and the rest will be converted

in back to back mode (see description of AdcGroupInBacktoBackMode). The delay

value defined by the user in AdcDelayNextPdb parameter will be used for 2nd, 3rd PDB

channel to avoid PDB internal errors.

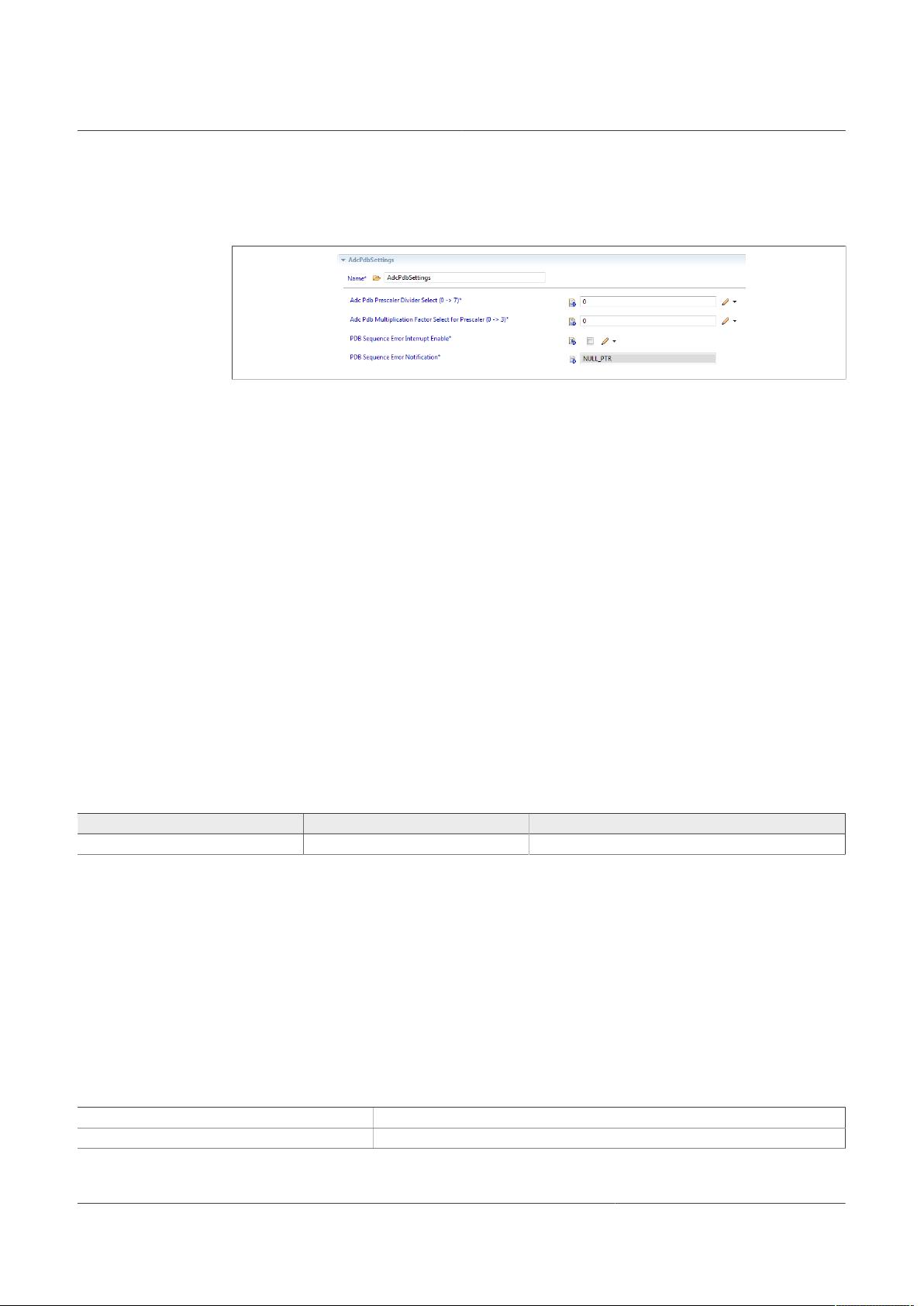

2.6.5.3 AdcDelayNextPdb – configuring the delay between PDB channel conversions

The PDB unit can have one or more PDB Channels of 8 pretriggers each that will be

used together for setting up conversions of large groups. The PDB Channels will be

started together when the PDB unit is triggered, thus risking to request conversions at the

same time and causing internal errors. For this reason, the value of AdcDelayNextPdb is

needed to be added as delay between PDB channels when Back to Back mode is used.

The AdcDelayNextPdb value should be greater than the timing to convert 8 channels.

The maximum total conversion time is determined by the clock source chosen and the

divide ratio selected. The clock source is selectable by CFG1[ADICLK], and the divide

ratio is specified by CFG1[ADIV]. To calculate total conversion time for one channel the

following formula is applied: ADC TOTAL CONVERSION TIME = Sample Phase Time

(set by SMPLTS+1) + Hold Phase (1 ADC Cycle) + Compare Phase Time (8-bit Mode=20

ADC Cycles, 10-bit Mode=24 ADC Cycles, 12-bit Mode=28 ADC Cycles) + Single or First

continuous time adder (5 ADC cycles + 5 bus clock cycles).

AUTOSAR_MCAL_ADC_UM All information provided in this document is subject to legal disclaimers. © NXP B.V. 2021. All rights reserved.

User manual Rev. 1 — 9 July 2021

UM2ADCASR4.0 Rev0003R1.0.5 16 / 91