Vivado设计流程指南:从安装到仿真实验

需积分: 50 60 浏览量

更新于2024-07-20

收藏 3.44MB PDF 举报

"Vivado设计流程指导手册包含Vivado工具的安装步骤以及如何进行设计流程,特别关注Project Mode的设计方法。这份手册通过一个简单的实验案例,详细讲解了从创建新工程到完成设计的每一个步骤,适用于初学者和Xilinx全球合作伙伴。"

在深入学习Vivado的设计流程之前,首先需要了解Vivado是什么。Vivado是Xilinx公司推出的一款综合型硬件描述语言(HDL)开发工具,主要用于FPGA(Field-Programmable Gate Array)的设计、仿真和实现。它集成了设计输入、综合、布局布线、仿真、调试等众多功能,极大地提高了FPGA开发的效率。

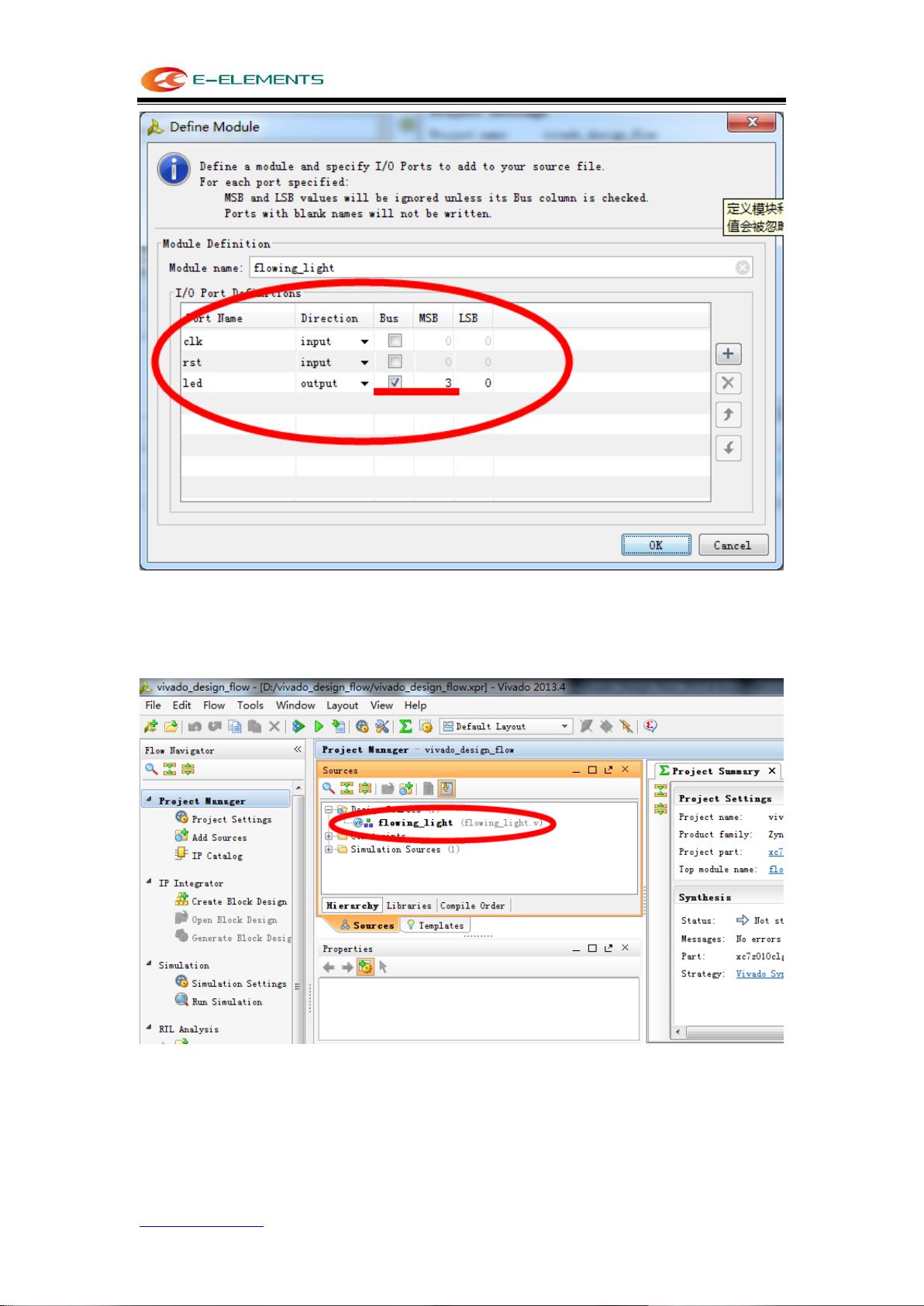

设计流程手册的第一步是新建工程。首先启动Vivado 2013.4版本的开发工具,可以通过桌面快捷方式或者在开始菜单的Xilinx Design Tools目录下找到。在打开的软件界面中,点击“Create New Project”图标,进入工程创建向导。

在工程创建过程中,需要填写工程名称和选择存储路径。确保名称和路径无中文字符和空格,建议使用字母、数字或下划线。同时,选择“Create project subdirectory”选项,这样会在指定的路径下自动生成一个独立的工程文件夹。

接下来,选择项目类型为“RTL Project”,表示我们要创建的是基于硬件描述语言(如Verilog或VHDL)的设计。然后,勾选“Donot specify sources at this time”,这会跳过在创建工程时立即添加设计源文件的步骤,使得工程创建更为简洁。

在选择目标器件阶段,需要根据实际使用的FPGA开发板来决定。例如,手册中提到的KC705开发板对应的是Artix-7系列的XC7A100TCSG324-2器件。这里需要正确设置Family(家族)、Subfamily(子家族)、封装形式(Package)和速度等级(Speed grade)等参数。

最后,确认所选的器件信息无误后,点击“Finish”完成工程创建,这时将展示一个空白的Vivado工程界面,意味着一个新的设计项目已经准备就绪。

这个流程只是Vivado设计流程的开端,后续还包括添加设计源文件、编译、仿真、实现和生成比特流等步骤。设计源文件可以是Verilog或VHDL代码,用于描述逻辑电路的功能。编译包括综合、布局和布线等过程,将高级语言代码转化为硬件配置。仿真则是验证设计功能是否符合预期,而实现则是在FPGA上布置和连接逻辑单元。生成比特流是将实现结果转化为可编程文件,最终下载到FPGA中运行。

Vivado设计流程手册提供了一个清晰的指南,对于初次接触Vivado的用户来说,它是一份非常实用的学习资料,可以帮助用户逐步掌握FPGA设计的基础知识和实践技能。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2021-09-30 上传

2019-01-12 上传

2018-09-07 上传

2020-05-19 上传

2023-04-23 上传

2022-09-23 上传

mackmao

- 粉丝: 0

- 资源: 5

最新资源

- JSP如何防范SQL注入攻击

- 就软件行业的测试标准规范

- Mercury LoadRunner教程8.1.pdf

- 卓有成效的程序员 专家解惑, 最佳实践

- MySQL GUI Tools Manual

- GB-T 14079-1993 软件维护指南

- widows 下的php扩展

- GB-T 16680-1996软件文档管理指南

- oracle listener监听8080.doc

- 计算机故障速查,一看就明白

- java入门学习书籍 Thinking.In.Java 3

- SCPI(Standard-Commands-for-Programmable-Instruments)命令全解

- Grails入门指南 主题 Web框架, 动态语言 标签 Groovy, Grails

- aix常用的一些简单命令

- Linux 网络实现代码导读

- 《疯狂java》jdk1.6 版 第四章