1132

Modelling and Analysis of Electromagnetic

Interferences for a 32-bit Digital Signal Controller

Zhou Changlin

#1

, Wang Jianmin

#2

, Pan Xiangfeng

#

, Gao Fei

#

, Yu Daojie

#

#

Zhengzhou Information Science and Technology Institue

P. O. Box 2201-180, Zhengzhou, Henan, 450001, China

1

zcl31233@tom.com

2

zzjimi@163.com

Abstract—This paper presents the modelling and analysis of

electromagnetic interferences (EMI) for a 32-bit digital signal

controller (DSC) that enables uncompromising performance and

real-time control applications for high electromagnetic

compatibility (EMC) requirement. The EMI behaviour model of

the DSC for conducted emission, built upon the package and chip

dies, is used to predict the EM emissions of the chip and printed

circuit board (PCB) levels. The characterization of EMI has been

analyzed by circuital simulations and conducted emission

measurements according to the EMC model. It is successfully

demonstrated that the simulated results are consistent with the

predictions generated by using the proposed model. And the

DSCs chip model, simulation and measurement of the EMI are

necessary for the analysis, prediction, and compatibility of the

PCB and systems design.

Keywords-electromagnetic compatibility (EMC), integrated

circuit (IC), digital signal controllers (DSCs), electromagnetic

interference (EMI), electromagnetic emission model, conducted

emission measurement.

I. INTRODUCTION

With the continuous trend towards integrated circuit (IC)

technology and increased integration of complex electronic

functions in critical applications, ensuring the electromagnetic

compatibility (EMC) of electronic systems is a great challenge

[1].The EMC of these systems has risen importantly as low

emissions and high immunity to electromagnetic interferences

(EMI) in overall electronic components or IC performance [2].

There are growing demands for low emission IC, applying for

low EMI design rules and requiring for efficient technological

with optimum value and placement for the decoupling

capacitance and bulk isolation for reducing emission [3],[4].

However, these issues require accurate EMI models, adequate

simulation analysis and EMI prediction methodology [5]-[7].

Most of the high EMC performance systems include some

microprocessors or microcontrollers, such as the digital signal

controllers (DSCs) combined the digital signal processors

(DSPs) and microcontrollers (MCUs), and request from

systems aiming at ensuring the EMC performance [8].

TMS320C28x 32-bit DSC devices currently have higher

central processing unit (CPU) performance and integration of

advanced high-speed peripherals, and have increased more

challenges in achieving EMC compliance [7],[9]. This paper

is focused on the EMI analysis, modelling and prediction for

the 32-bit DSC and two main sections. Section II describes the

DSC devices electromagnetic functional blocks and model

architecture. The DSC EMI model, emission simulation

analysis, decoupling capacitance optimization and reliable

EMC prediction are discussed in Section III.

II. E

LECTROMAGNETIC PERFORMANCES FOR DSC

The TMS320C28x 32-bit DSC includes high performance

CPU and multiple complex peripherals running at fairly high-

clock frequencies generating an amount of noise [8],[9]. The

EMI behaviors are caused by the high-speed switching circuits

through the power supply network, the ground network,

external interface and I/O pins.

A. Electromagnetic Functional Characterization

The DSC electromagnetic performances related to clock

generation, power supply, interfacing of peripherals with

special attention to analog-to-digital converter (ADC),

general-purpose input/output (GPIO) connections, and EMI

considerations. The parasitic emission on chip due to the CPU

clock and other digital circuit is continuously increased, and

may jeopardize the correct behavior. The basic noise sources,

coupling path and victim, receptor coexist in circuits or

devices. The DSC devices are highly integrated, high-

performance and its performance features, as shown in table ȱ.

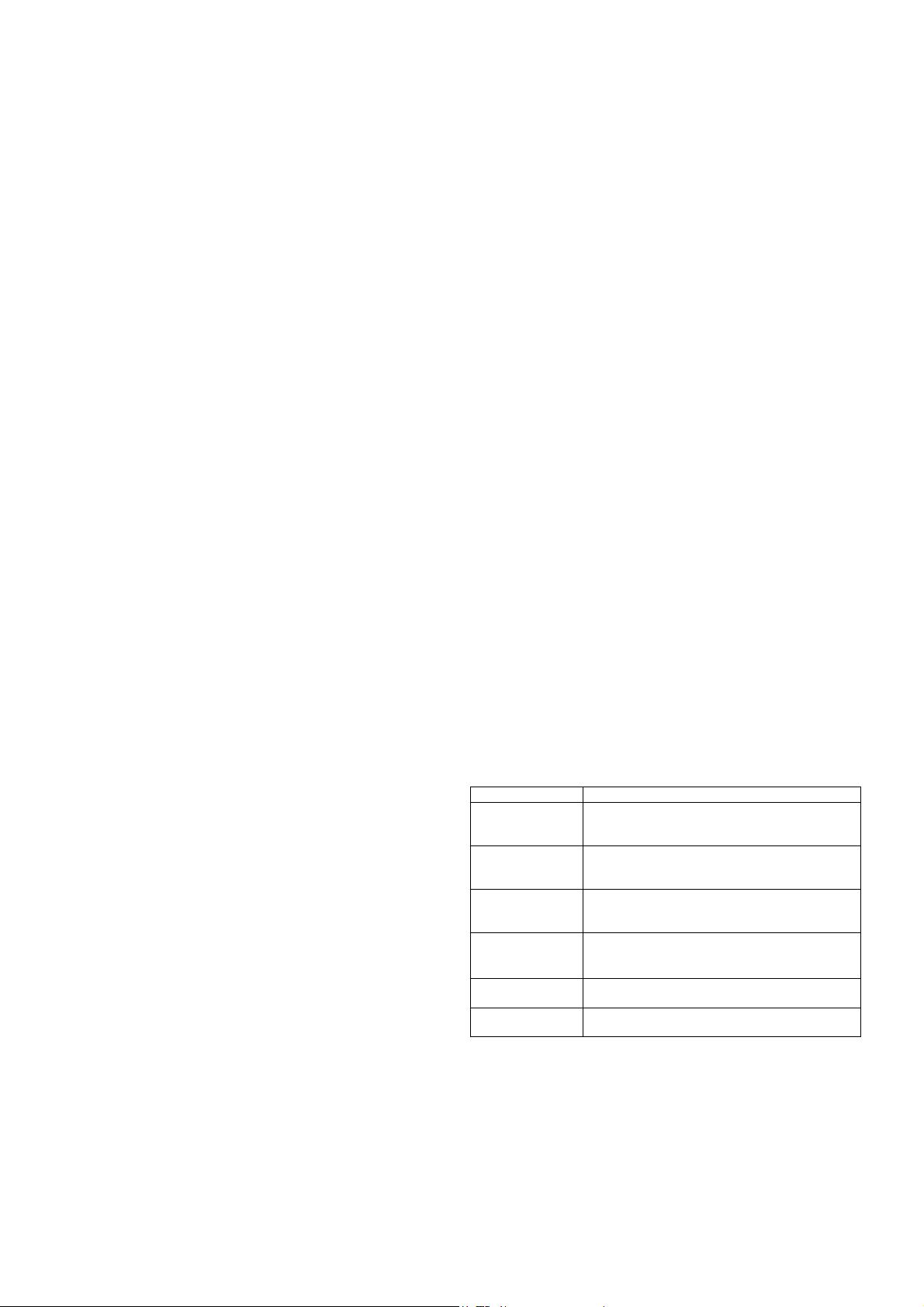

TABLE I.

T

HE PERFORMANCE OF DSC DEVICES

Features Description

High-Performance

Static CMOS

Technology

y 150 MHz (6.67ns Cycle Time)

y Low-Power (1.9V Core @150MHz, 3.3V I/O)

Design

High-Performance

32-Bit CPU (C28x)

y 16x 16 and 32 x 32 MAC Operations

y Harvard Bus Architecture

y Fast Interrupt Response and Processing

On-Chip Memory y Flash Devices: 128K x 16 Flash

y ROM Devices: 128K x 16 ROM

y Single-Access RAM:36Kx16 SARAM

Clock and System

Control

y Dynamic PLL-based Clock Module

y On-Chip Oscillator˖20-35MHz

y Watchdog Timer Module

On-Chip Analog-to-

Digital Converter

y 12-Bit ADC, 16 Channels

y Fast Conversion Rate: 80 ns at ADC clock 25MHz

External Interface and

Peripheral I/O

y 56 General Purpose I/O Pins, Speed Limit 20MHz

y Multiple Peripherals Port and Clock 20MHz

The DSC normal pin assignments are the 179-pin ball grid

array (BGA) package or the 176-pin low-profile quad flat-

______________________________________

978-1-4673-1800-6/12/$31.00 ©2012 IEEE