ModelSim寄存器组仿真实例教程:创建工程与流程详解

需积分: 0 62 浏览量

更新于2024-08-05

收藏 1.17MB PDF 举报

ModelSim是一种广泛使用的硬件描述语言(HDL)仿真器,主要用于验证和调试Verilog或VHDL设计。本文将详细介绍如何在ModelSim中进行寄存器组的创建、工程管理和仿真流程。

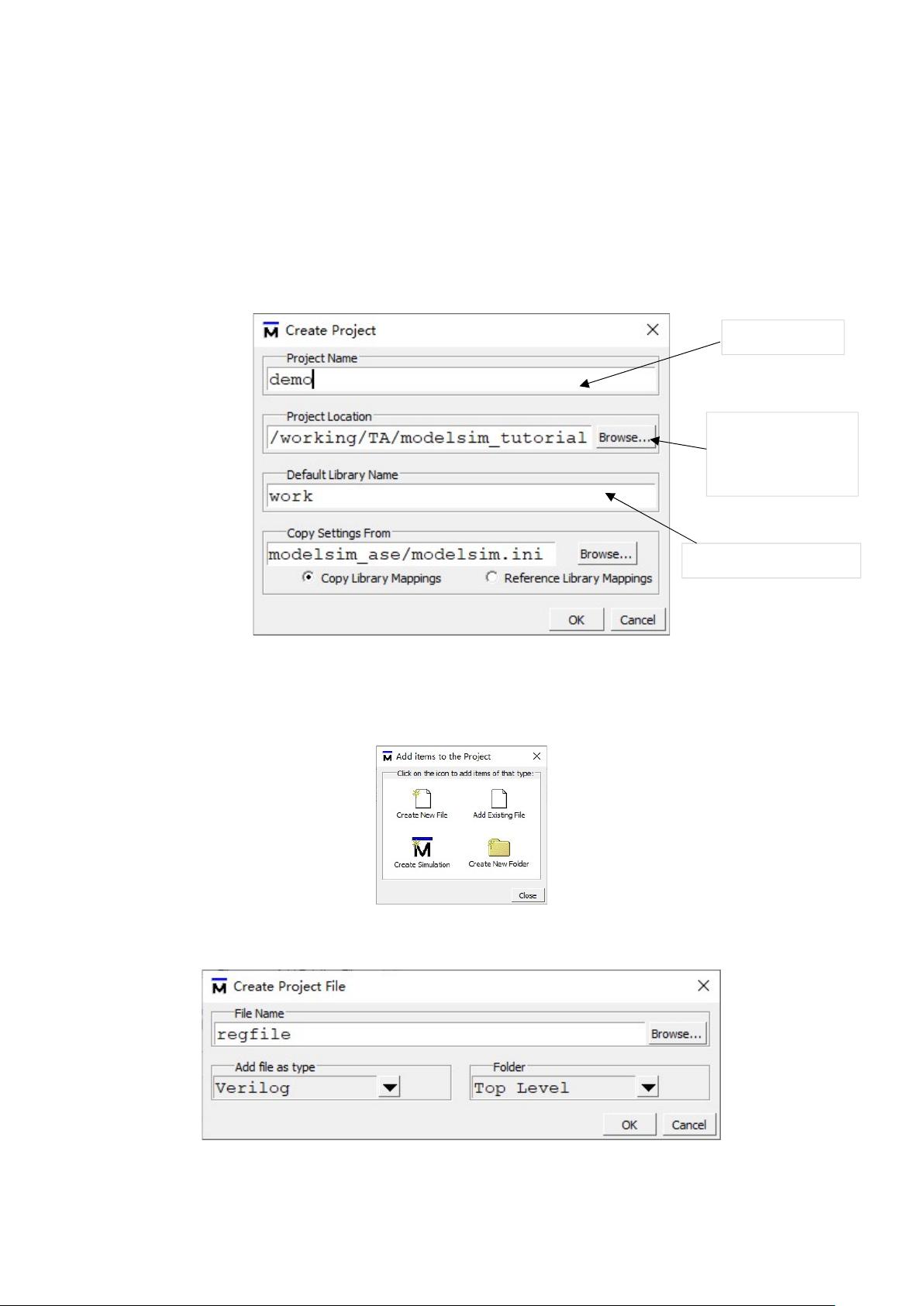

首先,启动ModelSim时,用户需要通过菜单栏选择"File" > "New" > "Project" 来创建一个新的项目。在这个步骤中,你需要为项目指定一个名称,并选择项目的保存位置。保持默认的工作库,或者根据需要自定义。

接着,通过"Create New File" 创建一个新的Verilog文件,命名为"regfile.v"。在编辑器中,粘贴预先准备好的寄存器组代码,如`moduleregfile`,它包含输入输出信号如时钟(clk)、写使能(we3)、地址(ra1, ra2, wa3)、数据(wd3)以及读取数据(rd1, rd2)等。这个模块使用`always @(posedge clk)`语句来实现数据的读写操作,以及`assign`语句来映射输入到寄存器数组`rf`。

在工程管理阶段,你可以通过右键点击文件列表项并选择"Compile" > "CompileSelected" 或者"CompileAll" 来确保所有的Verilog文件都被成功编译。如果需要添加测试模块,可以在项目栏中右键选择"Add to Project" > "NewFile",创建名为"test_regfile.v"的文件。在这个测试模块中,可以设置适当的输入信号,如`clk`、`we`、`ra1`等,并配置它们的初始值。

当所有文件都编译无误后,转到"Library"选项,找到刚刚编写的测试模块,右键点击并选择"simulate" 进行仿真。在模拟过程中,可能需要手动添加波形显示,通过菜单栏的"View" > "Wave" 来查看信号的行为。使用Shift+鼠标左键可以批量选择需要观察的信号,将其从"Object"窗口拖动到"Wave"窗口。

最后,运行测试可以通过"Simulate" > "Run" > "RunAll" 来执行。在测试完成时,你将在Wave窗口看到寄存器组的行为,这有助于验证设计的正确性。

附录中的`Regfile.v`和`test_regfile.v`文件分别展示了寄存器组的设计和测试用例,这对于理解实际的ModelSim仿真过程非常关键。通过这个例子,你可以了解到如何使用ModelSim对复杂的数字逻辑系统进行有效且细致的验证。

2010-12-07 上传

521 浏览量

2009-05-18 上传

2022-09-20 上传

2011-03-07 上传

2013-04-26 上传

2012-11-21 上传

2015-05-28 上传

2012-07-13 上传

一筐猪的头发丝

- 粉丝: 833

- 资源: 315

最新资源

- ratatoskr-simulator

- 行业文档-设计装置-无对接式套圈.zip

- netty-codec-http-4.1.16.Final.jar中文-英文对照文档.zip

- 基于PHP实现的wordpress便携通告插件_blog-quickly-shout_博客论坛(源代码+html).zip

- [重庆]现代风花园洋房+小高层住宅方案2020

- fd50to34:将34针软盘驱动器适配到50针控制器

- 【创新发文无忧】Matlab实现人工蜂鸟优化算法AHA-DELM的故障诊断算法研究.rar

- UART 24-12-15_uart_

- 行业分类-设备装置-大豆螺旋藻复合提取物的制备方法及其在水松纸上的应用[1].zip

- HL7ORUToFHIR:接收 HL7 ORU 消息并更新 HL7 FHIR 存储库的原型应用程序

- react-blr-sse-demo:此存储库包含与React Bangalore进行的“与服务器端事件进行实时”对话中显示的应用程序代码

- Buck变换器的建模与仿真_Simulink开关电源仿真模型_开关电源仿真_matlab simulink

- 基于arvr开发的管理系统

- 【对于一维信号的匹配】对一个一维(时间)信号y使用自定义基B执行匹配追踪(MP)研究Matlab代码实现.rar

- 行业分类-设备装置-多媒体数据传输方法和装置.zip

- C++入门教程视频-7