ADSP-TS101与FPGA结合扩展USB接口技术实现

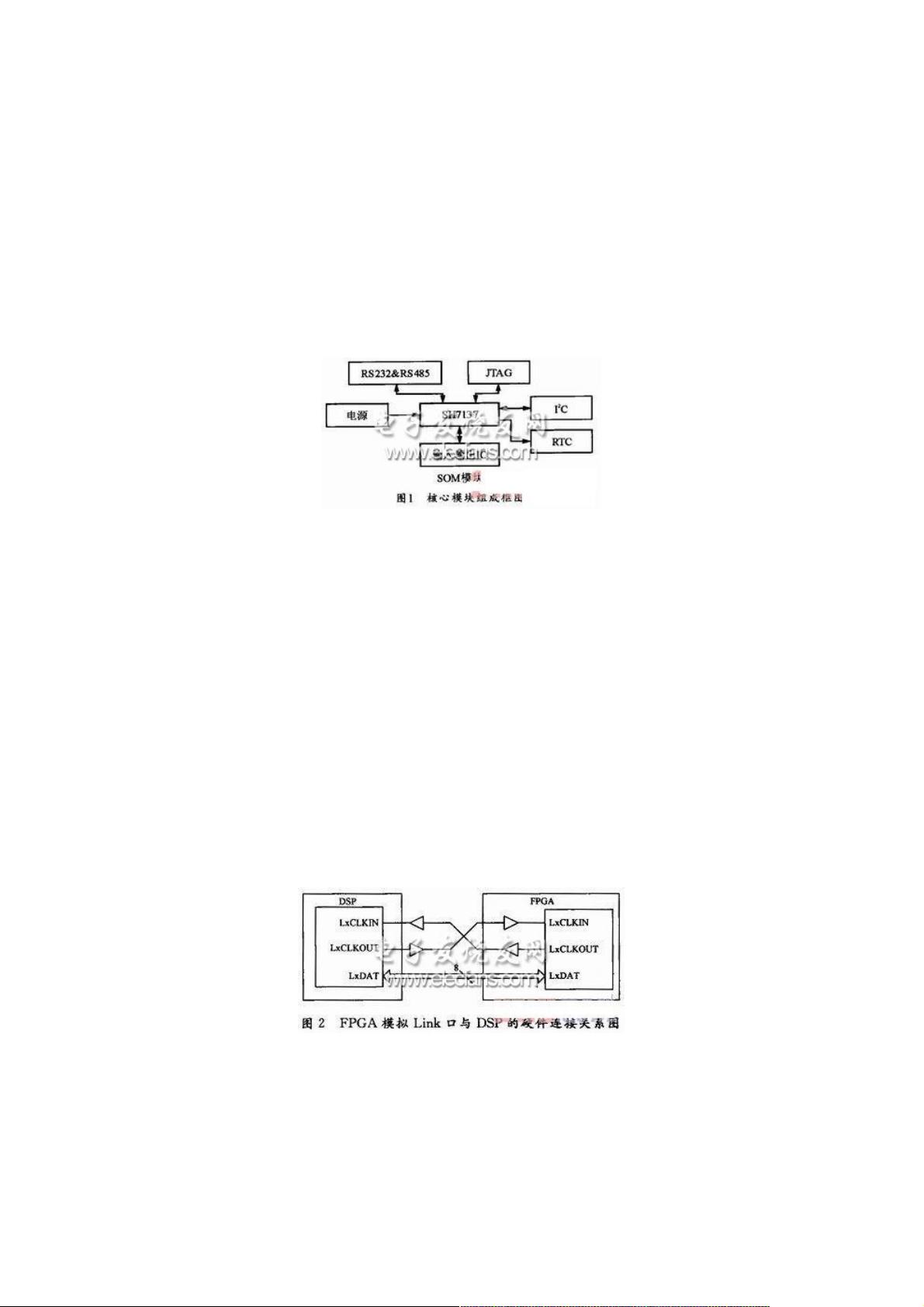

"这篇文档介绍了一种基于CY7C68013A USB控制器和FPGA实现的ADSP-TS101 DSP扩展接口设计,目的是为了在导弹系统试验中实现实时监控和记录大数据量的软件变量。" 本文档主要探讨了如何通过扩展接口来增强ADSP-TS101数字信号处理器的功能,使其能够与上位机进行高效的数据交换。ADSP-TS101是ADI公司的一款高性能浮点DSP,因其强大的实时处理能力和并行性,在弹载信号处理系统中广泛应用。在导弹系统试验中,需要监控和记录大量软件变量,而ADSP-TS101的原生外总线接口和Linkport接口并不适合这种需求,因为它们的速度快且连接复杂,不适合长距离传输。 设计中采用了 Cypress 的CY7C68013A USB控制器,通过FPGA(现场可编程门阵列)实现ADSP-TS101的Linkport接口与USB接口之间的数据缓冲和协议转换。FPGA内设置的上行和下行FIFO(先进先出存储器)用于数据缓冲,以适应两者之间不同的数据传输速率。DSP的链路口数据速率远高于USB的理论最大60MB/s速率,因此FIFO可以确保数据平稳传输,避免干扰DSP的并行执行程序。 系统的总体方案包括ADSP-TS101作为主处理器,通过FPGA与CY7C68013A建立连接。FPGA模拟Linkport口的接口时序,通过8位并行数据总线实现与DSP的数据交换。Linkport口的传输协议是每8个周期传输一个4字组,每个时钟沿传送一个字节,发送端需确认接收端准备好接收新的数据后才启动下一个传输。 文章进一步详细描述了Linkport口的传输协议,包括接收端在时钟的上升沿和下降沿接收数据,并只有在接收端的LxCLKOUT信号为高且有足够缓冲空间时,发送端才能开始新的传输。这部分内容展示了Linkport接口的同步机制和错误管理策略,对于理解整个设计的通信流程至关重要。 这个设计巧妙地解决了高速DSP与低速USB接口之间的数据传输问题,通过FPGA的智能缓冲和协议转换实现了高效的实时监控和记录功能,对于类似应用场合有着重要的参考价值。

下载后可阅读完整内容,剩余3页未读,立即下载

- 粉丝: 6

- 资源: 919

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- 李兴华Java基础教程:从入门到精通

- U盘与硬盘启动安装教程:从菜鸟到专家

- C++面试宝典:动态内存管理与继承解析

- C++ STL源码深度解析:专家级剖析与关键技术

- C/C++调用DOS命令实战指南

- 神经网络补偿的多传感器航迹融合技术

- GIS中的大地坐标系与椭球体解析

- 海思Hi3515 H.264编解码处理器用户手册

- Oracle基础练习题与解答

- 谷歌地球3D建筑筛选新流程详解

- CFO与CIO携手:数据管理与企业增值的战略

- Eclipse IDE基础教程:从入门到精通

- Shell脚本专家宝典:全面学习与资源指南

- Tomcat安装指南:附带JDK配置步骤

- NA3003A电子水准仪数据格式解析与转换研究

- 自动化专业英语词汇精华:必备术语集锦

信息提交成功

信息提交成功