大唐电信:FPGA-CPLD数字电路设计实践与高效策略

需积分: 9 81 浏览量

更新于2024-07-28

收藏 951KB PDF 举报

本文档分享了大唐电信在FPGA/CPLD数字电路设计方面的宝贵经验。FPGA/CPLD是现场可编程门阵列(Field-Programmable Gate Array)和复杂可编程逻辑器件(Complex Programmable Logic Device)的简称,它们被广泛应用于数字电路设计中,提供了高度灵活性和定制化能力。

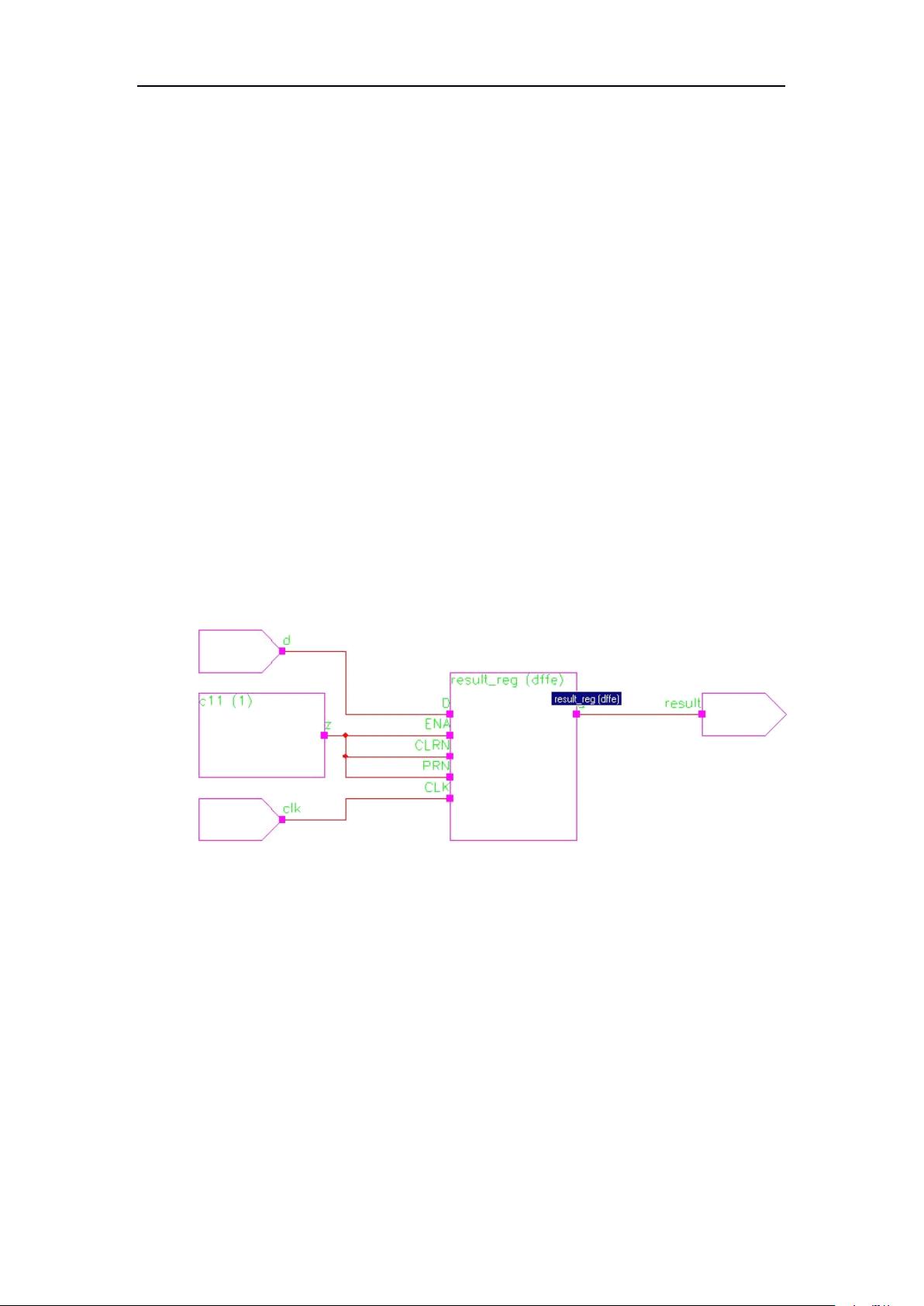

在数字电路设计过程中,时序设计至关重要,它是衡量系统性能的一个核心指标。高层次设计方法往往强调时序控制的抽象,这使得精确把握时序变得更具有挑战性。然而,通过理解RTL(Register-Transfer Level)电路的时序模型,并采用合理的策略,例如在设计复杂系统时采用后仿真的优化方法,可以显著提升电路的后仿真通过率,进而实现更高的系统工作频率。

设计中涉及的基本概念包括建立时间和保持时间。建立时间(setuptime)指的是数据稳定之前需要等待的时钟信号上升沿时间,而保持时间(holdtime)则是数据在时钟上升沿之后保持稳定的时间。这两个参数对于确保数据准确无误地传输至触发器至关重要。在实际设计中,需要考虑时钟树的偏斜效应,即在计算建立时间时要考虑时钟信号向前传播的影响,在检查保持时间时则要考虑时钟信号向后传播的影响。

在可编程器件如FPGA中,由于其内部时钟树的自适应性,保持时间的满足通常不成问题。然而,建立时间与时钟周期密切相关,当系统在高速时钟下无法工作时,可以通过降低时钟频率来解决问题。然而,保持时间与频率无关,设计不合理可能导致布局布线问题,即使调整时钟频率也可能无法满足要求,此时可能需要对设计进行重大修改,严重影响设计效率。

因此,合理设计系统的时序参数是提高设计质量和效率的关键。在FPGA/CPLD设计中,理解并掌握这些基本概念,结合实际案例和工具的运用,能够有效地优化电路设计,提升最终产品的性能和可靠性。

2010-03-11 上传

191 浏览量

120 浏览量

2009-05-13 上传

2009-10-15 上传

143 浏览量

2009-10-09 上传

124 浏览量

1292 浏览量

li987072220

- 粉丝: 3

- 资源: 51