MAX 10 FPGA信号完整性设计关键指南

需积分: 12 22 浏览量

更新于2024-07-16

收藏 981KB PDF 举报

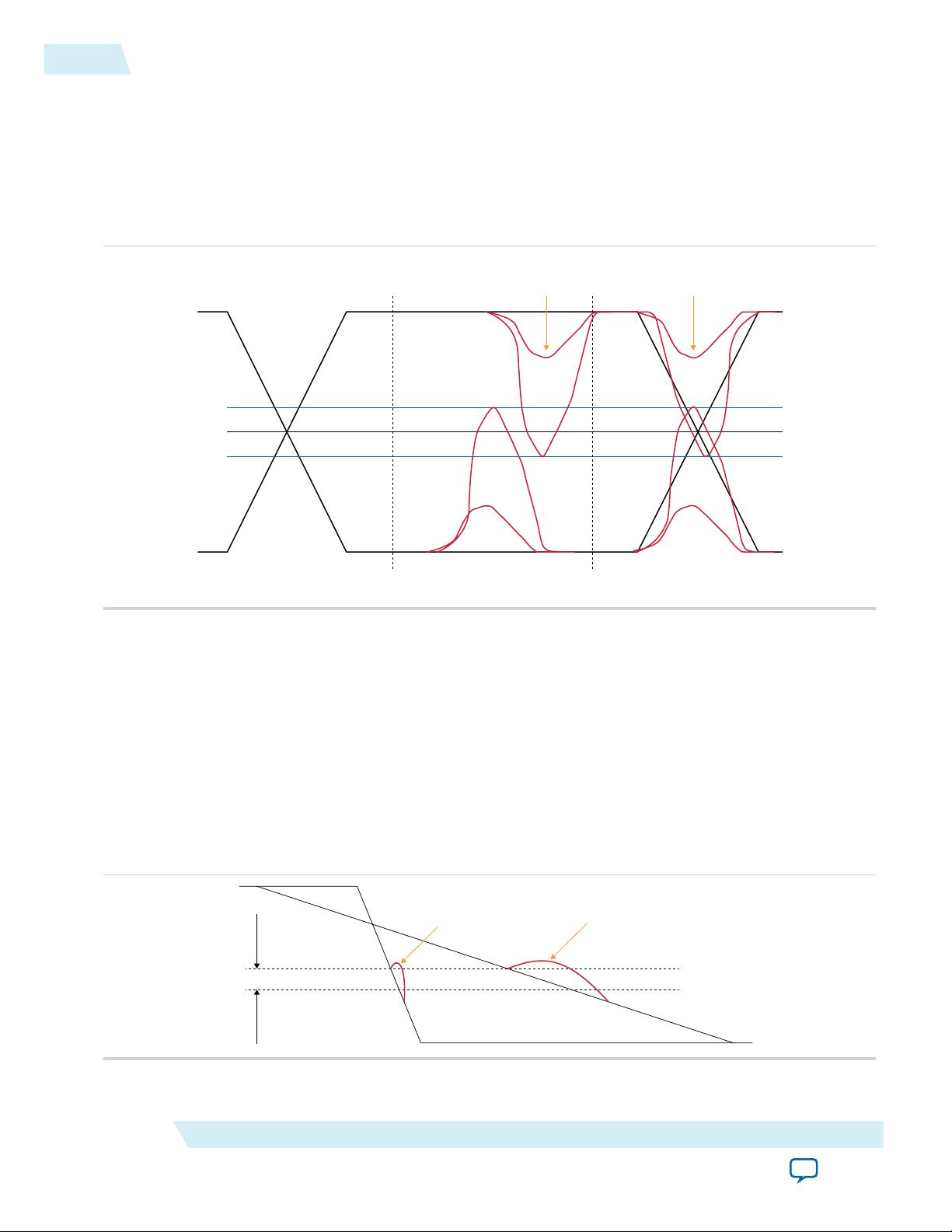

"MAX 10 FPGA 信号完整性设计指南提供了关于如何在使用MAX 10 FPGA时确保信号完整性的详细指导。这份全中文文档强调了同步开关噪声(SSN)对信号完整性的负面影响,以及如何通过遵循特定的设计考量、I/O布局规则和电路板设计实践来避免这些问题。指南涵盖了关键领域,如I/O布局、电压参考I/O标准、高速LVDS、PLL和时钟管理、外部存储器接口和模拟到数字转换器的集成。在实际的PCB布局之前,进行SSN分析是Altera推荐的一个重要步骤。此外,文档还定义了一系列与信号完整性相关的专业术语,帮助读者理解和解决SSN带来的电压噪声和时序噪声问题。"

在设计MAX 10 FPGA系统时,信号完整性是一个至关重要的考虑因素,因为SSN可能导致信号失真,进而降低系统的噪声容限。设计者需要遵循一系列规则来防止这些问题,如:

1. **I/O布局规则**:正确的I/O布局能减少信号间的干扰,避免噪声的传播。设计者应考虑将具有相似速度和驱动能力的I/O放置在一起,同时考虑信号的路径长度,以减少串扰。

2. **电压参考I/O标准**:选择合适的电压参考标准对于减小噪声至关重要。理解不同I/O标准的电气特性并根据应用需求进行选择是确保信号完整性的基础。

3. **高速LVDS,锁相环(PLL)和时钟**:高速LVDS接口可提供低噪声的高速数据传输,而PLL和时钟管理则用于同步和优化系统时序。设计者需关注这些组件的设置,以减少时钟抖动和相位噪声。

4. **外部存储器接口**:与外部存储器的接口设计需要考虑匹配和去耦,以减少反射和噪声。适当的端接策略和布局可以显著改善信号质量。

5. **模拟到数字转换器**:在混合信号系统中,ADC的接口设计需要特别注意,确保其工作在最佳性能条件下,同时隔离模拟和数字部分,减少相互影响。

此外,了解和分析SSN的机制是设计过程中的关键步骤。SSN是由于同一器件内其他输出或双向信号的开关活动导致的单个受害I/O上的噪声。它分为电压噪声(如QHN和QLN)和时序噪声两部分,这两类噪声都可能影响系统的稳定性和可靠性。

通过理解SSN的定义、分类及其影响,设计者能够更有效地预测和控制这些问题,确保MAX 10 FPGA系统达到预期的性能标准。遵循Altera提供的设计指南,结合SSN分析工具,可以帮助设计者实现一个高效且可靠的FPGA解决方案。

2020-04-09 上传

2020-12-13 上传

2022-11-29 上传

2015-08-21 上传

2022-11-29 上传

2022-11-29 上传

2019-05-21 上传

2022-11-29 上传

ADC林三

- 粉丝: 2

- 资源: 7

最新资源

- MATLAB新功能:Multi-frame ViewRGB制作彩色图阴影

- XKCD Substitutions 3-crx插件:创新的网页文字替换工具

- Python实现8位等离子效果开源项目plasma.py解读

- 维护商店移动应用:基于PhoneGap的移动API应用

- Laravel-Admin的Redis Manager扩展使用教程

- Jekyll代理主题使用指南及文件结构解析

- cPanel中PHP多版本插件的安装与配置指南

- 深入探讨React和Typescript在Alias kopio游戏中的应用

- node.js OSC服务器实现:Gibber消息转换技术解析

- 体验最新升级版的mdbootstrap pro 6.1.0组件库

- 超市盘点过机系统实现与delphi应用

- Boogle: 探索 Python 编程的 Boggle 仿制品

- C++实现的Physics2D简易2D物理模拟

- 傅里叶级数在分数阶微分积分计算中的应用与实现

- Windows Phone与PhoneGap应用隔离存储文件访问方法

- iso8601-interval-recurrence:掌握ISO8601日期范围与重复间隔检查