"Vivado时序约束:XDC格式与业界标准对比"

版权申诉

65 浏览量

更新于2024-02-20

收藏 9.77MB PDF 举报

Vivado集成开发环境是Xilinx公司提供的一款设计工具,相比于之前的ISE软件,Vivado引入了一项重大变革,即约束文件的更新。在ISE软件中,约束文件使用的是UCF(User Constraints File)格式,而在Vivado中则引入了XDC(Xilinx Design Constraints)格式。XDC格式主要基于业界标准SDC(Synopsys Design Constraints),同时还集成了Xilinx自己的一些约束标准,这样的转变可以看作是Xilinx向业界标准靠拢的一步。相对于之前的方式,这种更加标准化的约束文件格式对于工程师们来说是一个好消息,因为在不同平台之间的转换会更加容易。

在Vivado软件中,时序约束的设置非常重要。时序约束可以描述设计的时序要求,帮助综合工具、布局布线工具和时序分析工具理解设计者的意图,保证设计在时序上的正确性与可靠性。时序约束在FPGA设计中起着至关重要的作用,是确保设计能够满足时序要求的关键一步。

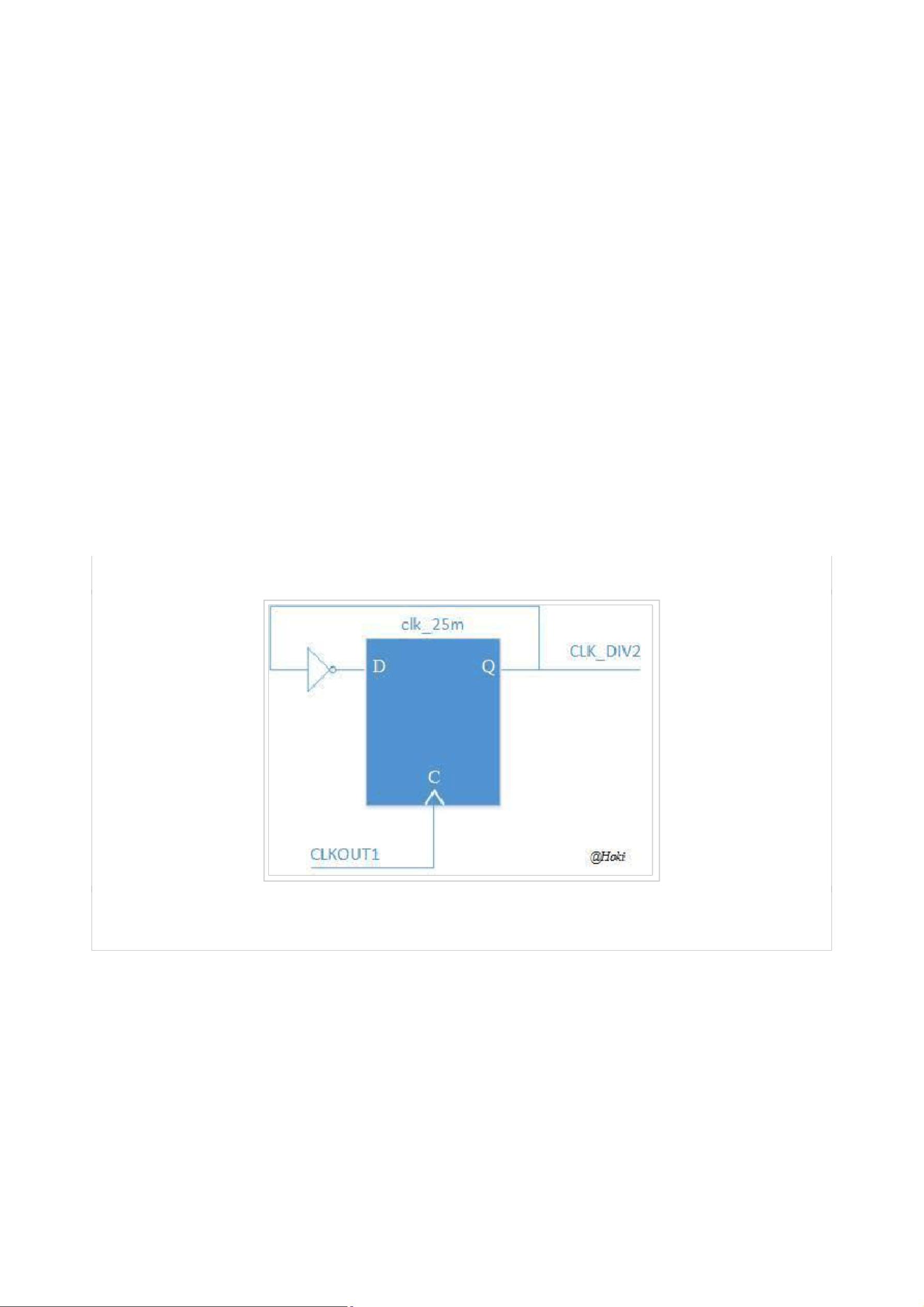

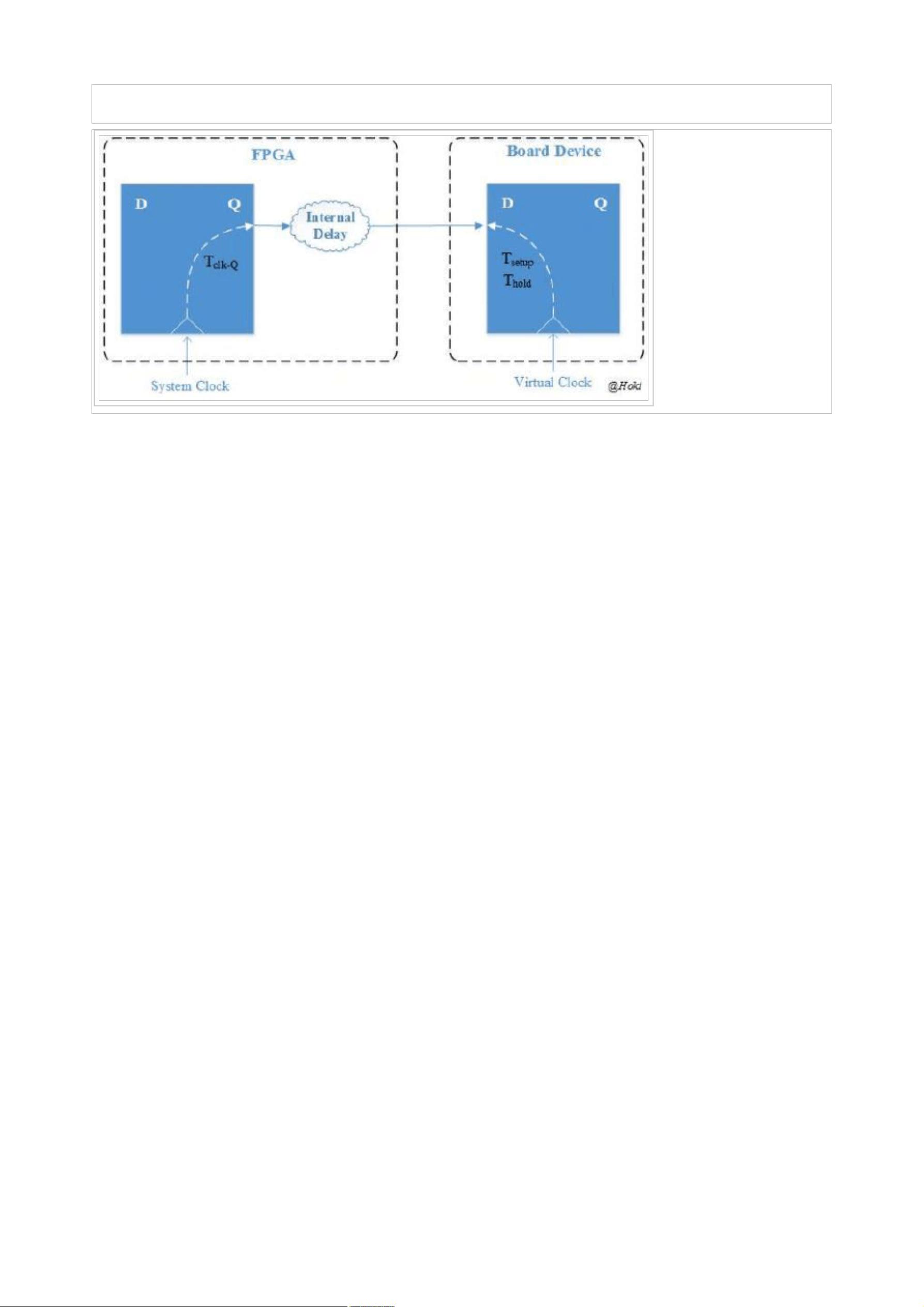

时序约束文件通常包括时钟约束、时序路径、时钟分配等内容。时钟约束用于描述时钟的频率、相位、时钟起始点等信息;时序路径用于描述数据路径的时序要求,包括数据到达时间和时序边界等;时钟分配用于描述时钟资源的分配和使用情况。

Vivado提供了丰富的时序约束设置功能,可以通过图形界面或者文本方式进行设置。通过正确地设置时序约束,设计者可以确保设计在综合、布局、布线和时序分析阶段能够按照预期的时序要求进行,并且可以及时发现和解决设计中的时序问题。

总的来说,时序约束在FPGA设计中起着至关重要的作用,Vivado作为一款先进的集成开发环墨,提供了强大的时序约束设置功能,帮助设计者更好地理解设计需求,保证设计的时序正确性与可靠性。希望通过本文的介绍,读者能够更加深入地了解Vivado中时序约束的设置方法,从而在FPGA设计中取得更好的效果。感谢您的支持与关注。

522 浏览量

253 浏览量

点击了解资源详情

503 浏览量

121 浏览量

373 浏览量

310 浏览量

358 浏览量

776 浏览量

想要offer

- 粉丝: 4081

最新资源

- Node.js项目mmRequest-demo的实践教程

- Matconvnet1.0-beta20:Matlab深度学习工具包深度解析

- GGTabBar:实现IOS多选项卡的简单案例源码

- 省市县镇村五级数据导入数据库操作指南

- MFC制作的洗牌系统:界面优化体验

- Android Studio 邮件发送功能实现演示

- 彻底清理旧.NET框架的免费工具下载

- MATLAB实现一元线性回归算法详解

- 掌握JavaScript的课堂简单练习

- SDN中的POX控制器负载均衡策略代码

- Swift实现的点击弹出动态菜单效果教程

- SSM框架与ORACLE数据库整合教程

- Windows系统下的Redis服务部署指南

- WinWebMail v3.8:邮件服务器的高效解决方案与聚类分析算法

- 免费获取虚拟版Visual C++ 6.0 Repack版下载

- 2022年美赛备资料精选集合