NiosII FPGA平台上的MPEG-4实时解码器设计

60 浏览量

更新于2024-09-02

收藏 293KB PDF 举报

"基于NiosII的MPEG-4视频播放器设计,通过在NiosII软核CPU和FPGA构建的SOPC(System-on-a Programmable Chip)系统上,利用用户自定义指令加速MPEG-4解码过程中的关键步骤,如反量化(IQ)、逆离散余弦变换(IDCT)和运动补偿(MC),提升解码效率。系统在XviDCodec开源代码基础上,实现了在SimpleProfile标准下,L1级别,177x144像素的QCIF分辨率,25帧每秒的MPEG-4视频实时解码,并利用DMA(Direct Memory Access)技术将解码后的视频流显示在LCD屏幕上。"

在多媒体技术中,视频压缩是一个至关重要的环节,而MPEG-4标准因其高效的数据压缩比和灵活的内容表示能力,广泛应用于移动设备和网络视频传输。然而,MPEG-4解码过程中的计算复杂度高,对处理能力和功耗有较高要求,特别是对于手持终端来说,实现实时解码是一个挑战。

本系统的设计巧妙地结合了软件和硬件的优势,使用NiosII嵌入式处理器作为核心,通过定制指令集来硬件化执行计算密集型任务,显著提升了解码速度。NiosII是 Altera 公司开发的一种可定制的32位RISC处理器,它允许用户添加特定的硬件加速器,以优化特定应用性能。

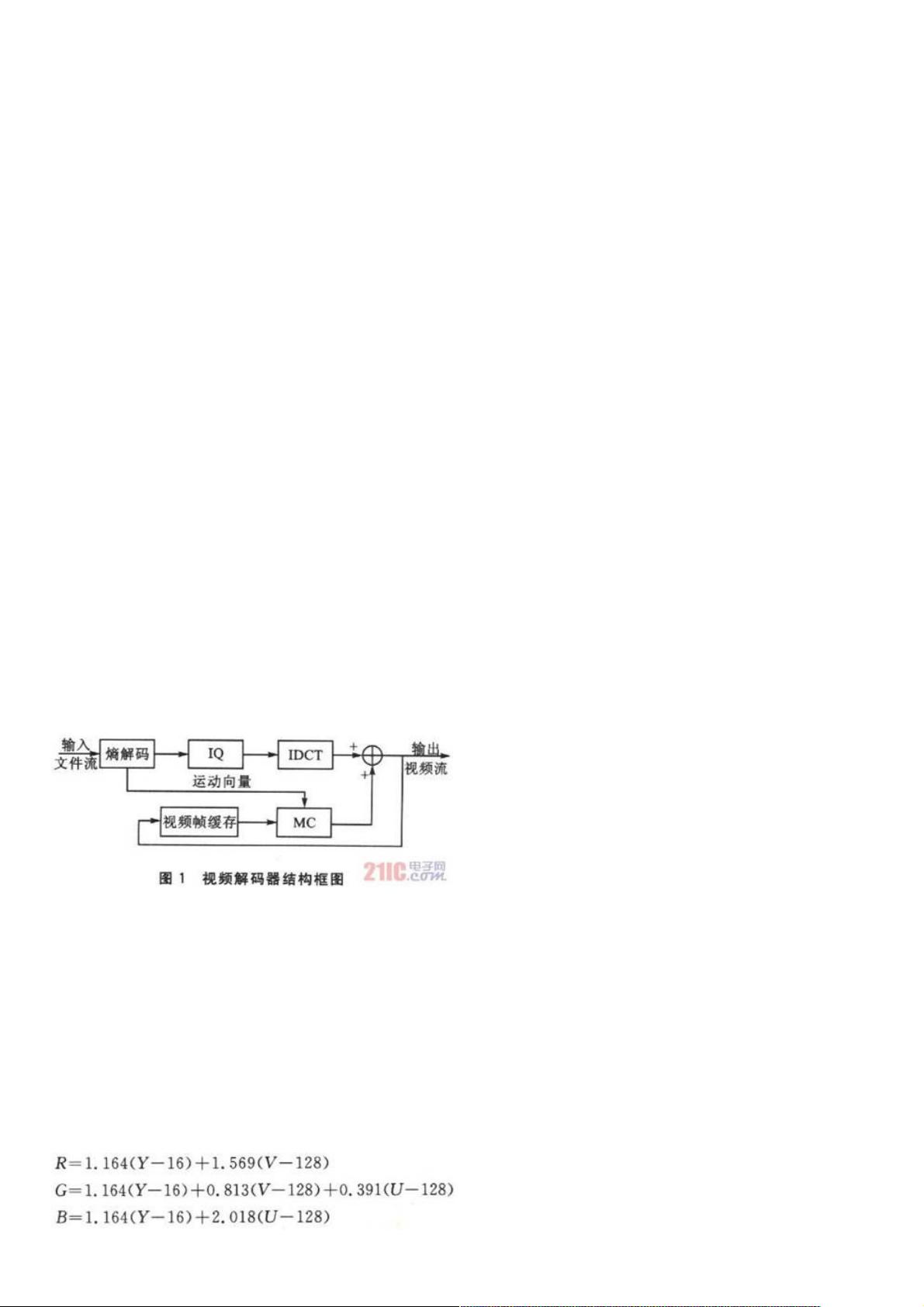

系统架构分为四个主要部分:视频文件存取、视频解码器、YUV-RGB转换器和LCD控制模块。视频文件存取部分负责MP4文件的读取和存储,使用Flash存储器进行数据存储,并通过JTAG接口进行文件传输。视频解码器包含熵解码、反量化、IDCT、运动补偿以及帧缓冲模块,形成一个完整的解码流程。熵解码处理压缩码流,反量化和IDCT将频域数据转换为空间域,运动补偿则根据先前帧的信息修正当前帧,提高图像质量。

YUV-RGB转换器是将解码后的YUV格式视频数据转换成RGB格式,以适应大多数显示设备的要求。最后,LCD控制模块通过DMA方式将处理后的视频数据传送到LCD屏幕上,实现流畅的视频播放。

这个设计充分体现了SOPC系统的灵活性和可定制性,将软件的易编程性和硬件的高速运算能力相结合,成功地解决了手持设备上的MPEG-4视频实时解码问题。此外,通过开源的XviDCodec,系统能够遵循GPL协议,保证了设计的开放性和可扩展性,为后续的优化和升级提供了可能。

2020-12-13 上传

2020-10-19 上传

2020-10-19 上传

点击了解资源详情

2012-09-18 上传

2022-09-19 上传

2018-01-20 上传

weixin_38654415

- 粉丝: 4

- 资源: 1015

最新资源

- sweet_smoke_lp

- SPWM.rar_单片机开发_Windows_Unix_

- GMSMapView-Additions:自定义GMSMapView“我的位置”按钮

- Django_Network:Django社交网络

- ImageLab-Initial:ImageLab是一个独立工具,可让用户使用其GUI玩OpenCV

- Teste-oo1:用StackBlitz创建:high_voltage:

- Web应用程序和服务的集中式和分布式日志记录,扩展了System.Diagnostics和Essential.Diagnostics,提供了结构化的跟踪和日志记录,无需更改应用程序代码的1行-JavaScript开发

- torch_sparse-0.6.9-cp36-cp36m-macosx_10_9_x86_64whl.zip

- yukimryh.zip_matlab例程_matlab_

- TeTsuYa IRC Bot-开源

- qa_guru_4_10_owner_xt4k:草稿

- Assembla Mentions-crx插件

- 点击:简单的React useState钩子示例

- 参考资料-中国的书法艺术和技巧.蓝铁.zip

- 一个无主题的Web组件,用于根据表单字段值过滤可见的子元素。-JavaScript开发

- arduino-volume2:Arduino tone()-仅使用扬声器即可实现多种波形和8位音量控制!