Design Compiler: 综合与集成电路设计的关键工具

需积分: 9 68 浏览量

更新于2024-07-19

收藏 767KB PDF 举报

"综合与Design Compiler是集成电路设计的关键步骤,主要涉及将高级描述转换为门级网表。Design Compiler是Synopsys公司的旗舰工具,用于完成这一任务。本章介绍了综合的基本概念,其在设计流程中的重要性,以及综合过程的三个主要阶段:转换、优化和映射。综合是连接设计的高层次描述与物理实现的关键环节,其结果直接影响后续的布局布线和电路的可测试性。此外,电路综合的特点包括限制条件驱动,即设计者设定的约束指导优化过程。"

集成电路设计中的综合是一个至关重要的环节,它涉及到将行为描述或RTL级的电路转化为具体的门级实现。Design Compiler作为Synopsys公司的核心工具,能够高效地处理这一转换过程。通过HDL(硬件描述语言)如VHDL或Verilog描述的电路,Design Compiler能够生成基于特定工艺库的门级网表,为后续的物理设计提供基础。

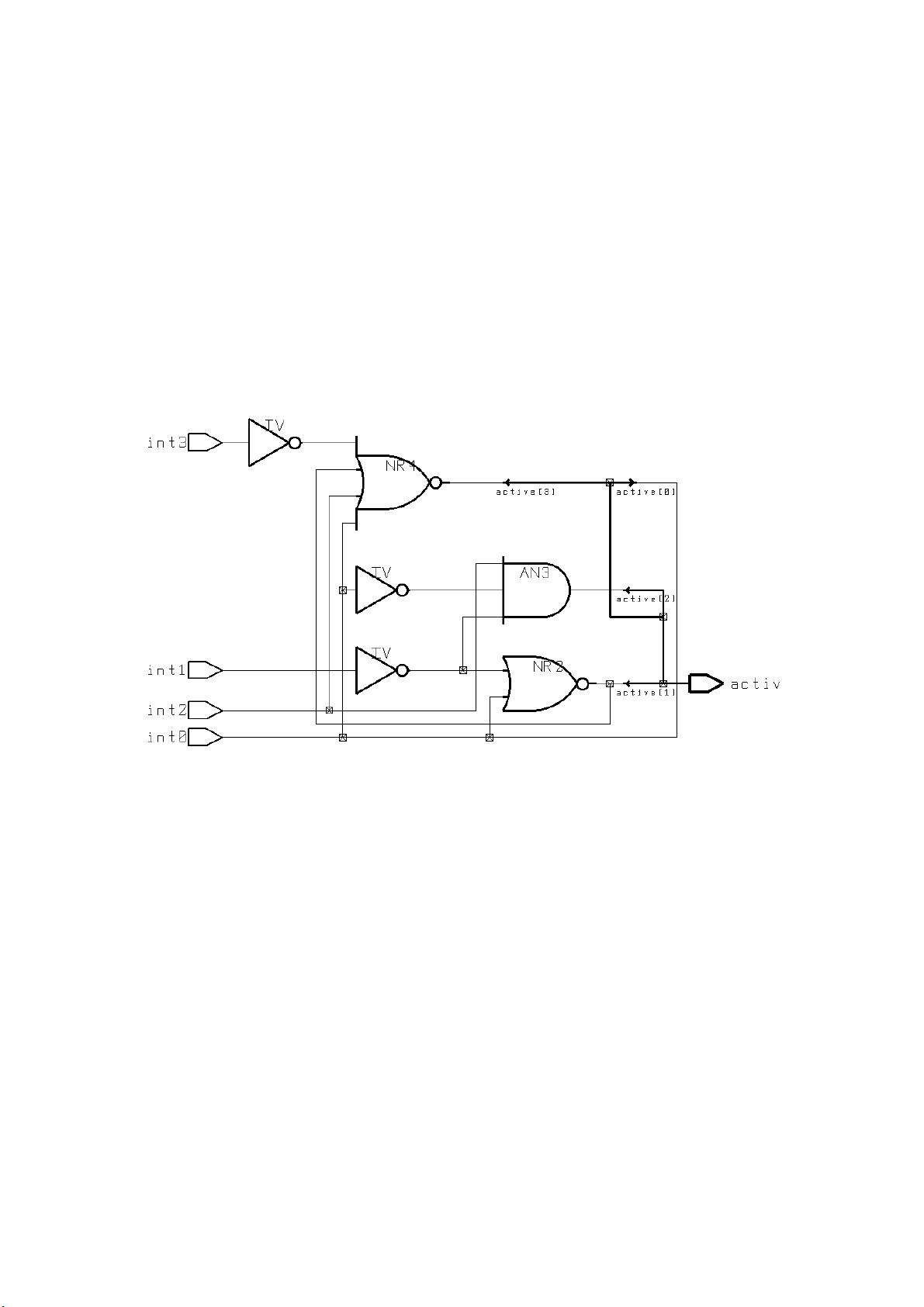

在集成电路设计流程中,综合位于前端设计的末端,是连接设计的高层次抽象和实际物理实现的桥梁(见图4-2)。这个阶段的结果,即门级网表,将直接影响到电路的性能、面积和功耗,并且会传递给后端的布局布线工具。因此,综合的质量至关重要,设计者必须在HDL描述和综合过程中考虑可测试性,并设置适当的约束条件,比如时序要求、功耗限制等。

综合过程通常分为三个阶段:转换、优化和映射。转换阶段,Design Compiler将HDL描述的电路转换为门级逻辑表示,使用工艺库中的基本逻辑单元。接着,优化阶段去除冗余,优化逻辑路径,以满足设计要求。最后,映射阶段将优化后的电路布局到特定工艺库的物理单元上,确保电路的物理实现符合设计规范。

电路综合的特点是限制条件驱动。这意味着设计者的输入条件,如时钟周期、功耗预算等,会直接影响综合工具生成的门级实现。这些限制条件在系统设计初期就应被考虑,以便生成满足性能需求的电路。

为了确保电路的可测试性,综合不仅要考虑电路的功能正确性,还要考虑故障检测和诊断的便利性。这通常意味着在设计和综合阶段就需要引入可测性设计(DFT)的概念,例如边界扫描测试(BIST)和多模式测试,以提高生产过程中的测试效率和产品质量。

综合阶段的选择和参数设置对最终电路的性能有着深远的影响。设计者需要深入理解Design Compiler的特性和操作,才能有效地利用这个工具,生成最优的门级实现,以满足设计目标并优化整体系统的性能。

2018-05-02 上传

2020-02-26 上传

2017-01-06 上传

2023-10-23 上传

2016-04-27 上传

2021-02-23 上传

137 浏览量

2024-03-04 上传

archimedes1988

- 粉丝: 0

- 资源: 5

最新资源

- STRUCTDLG:该函数将结构作为输入,然后自动构建图形用户界面。-matlab开发

- Wipadika-Innovations-Auth

- Skystone-10355

- trmilli:利西亚语中的墓志文字

- 博客网站

- WeeWX driver for Wario ME11/1x stations:Wario ME11 / 12/13/15站的WeeWX驱动程序-开源

- goit-react-hw-01-components

- Android应用源码之小米便签源代码分享.zip项目安卓应用源码下载

- test2,c语言编写简单图形界面源码,c语言程序

- 单板11-26A.zip

- background-gen

- 提取均值信号特征的matlab代码-matlab_classifier_2021:matlab_classifier_2021

- SelectPopupWindow.7z

- china-code.net.zhy.20,c语言程序设计现代方法源码,c语言程序

- cyclemap.github.io:循环图静态内容

- 萨拉介绍