Virtex-6 FPGA实现四倍实时并行上采样技术

87 浏览量

更新于2024-09-01

收藏 927KB PDF 举报

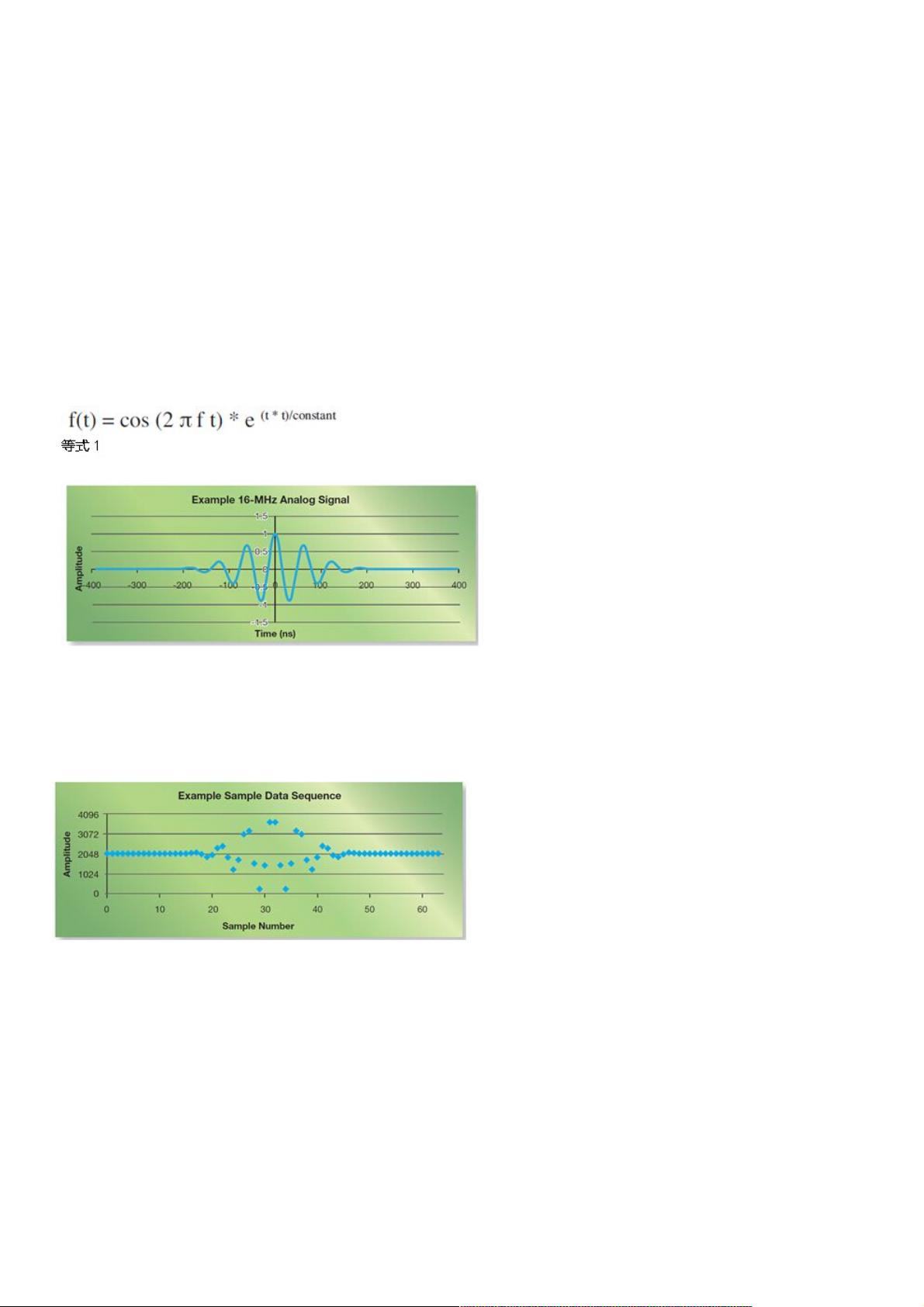

"本文主要探讨了如何利用FPGA(Field-Programmable Gate Array,现场可编程门阵列)技术,特别是Virtex-6器件,以及免费的WebPACK工具来实现实时的四倍上采样。上采样是数字信号处理中的一种重要技术,与下采样相反,它通过在原有信号样本之间插入零来增加采样率。文中提出的高效并行实时上采样电路能够在每个ADC(Analog-to-Digital Converter,模数转换器)时钟周期内生成四个上采样值,适用于多种信号处理应用。该方法基于‘窗口SINC插值’理念,能有效减少计算量,适合在FPGA内部实现。"

在数字信号处理领域,上采样是一种用于提高数字信号采样率的技术。通常,上采样是通过在原始样本之间插入零来实现的,这会增加数据长度,随后通过低通滤波器消除高频复制的频谱,以保持信号的原始信息。对于实时系统来说,高效的上采样方法至关重要,因为它直接影响到系统的处理速度和资源利用率。

Virtex-6 FPGA是一款高性能的可编程逻辑器件,具有丰富的逻辑资源和高速I/O能力,非常适合实现这种复杂的并行处理任务。文中提到的WebPACK工具是Xilinx公司提供的免费开发平台,包含了设计、仿真和实现FPGA设计所需的一系列软件工具,使得设计者无需高昂成本即可开发高级的数字系统。

在本文的示例中,一个16MHz的模拟信号被12位ADC以80MHz的采样率进行采样,得到的数据序列经过四倍上采样后,采样率提升至320MHz,每个信号周期提供20个样本。这种方法展示了如何在不牺牲性能的前提下,通过FPGA实现高效并行的上采样操作。

FIR(Finite Impulse Response,有限冲激响应)滤波器在上采样过程中扮演关键角色,因为上采样后的数据需要经过滤波以去除插入的零所引起的高频复制。FIR滤波器设计是这一过程的关键环节,可以根据所需频率响应特性定制滤波器系数,以确保有效地去除不需要的频谱成分。

使用FPGA实现高效并行实时上采样是一种优化信号处理性能的有效策略,尤其适用于需要高采样率和实时处理的系统。通过Virtex-6 FPGA和WebPACK工具,设计者可以构建出满足特定需求的定制化解决方案,而无需过于复杂的计算资源。这种技术的应用广泛,涵盖了通信、图像处理、音频处理等多个领域。

2019-08-01 上传

2024-01-31 上传

2023-09-08 上传

2023-07-18 上传

2023-08-25 上传

2023-05-09 上传

2023-07-14 上传

weixin_38612527

- 粉丝: 5

- 资源: 954

最新资源

- Java集合ArrayList实现字符串管理及效果展示

- 实现2D3D相机拾取射线的关键技术

- LiveLy-公寓管理门户:创新体验与技术实现

- 易语言打造的快捷禁止程序运行小工具

- Microgateway核心:实现配置和插件的主端口转发

- 掌握Java基本操作:增删查改入门代码详解

- Apache Tomcat 7.0.109 Windows版下载指南

- Qt实现文件系统浏览器界面设计与功能开发

- ReactJS新手实验:搭建与运行教程

- 探索生成艺术:几个月创意Processing实验

- Django框架下Cisco IOx平台实战开发案例源码解析

- 在Linux环境下配置Java版VTK开发环境

- 29街网上城市公司网站系统v1.0:企业建站全面解决方案

- WordPress CMB2插件的Suggest字段类型使用教程

- TCP协议实现的Java桌面聊天客户端应用

- ANR-WatchDog: 检测Android应用无响应并报告异常