FPGA灵魂:CLB详解与DSP48资源解析

需积分: 17 158 浏览量

更新于2024-08-04

1

收藏 492KB DOC 举报

"本文主要介绍了FPGA的基本结构,特别是其核心的可配置逻辑块(CLB)和DSP48单元,以及如何计算和利用这些硬件资源。"

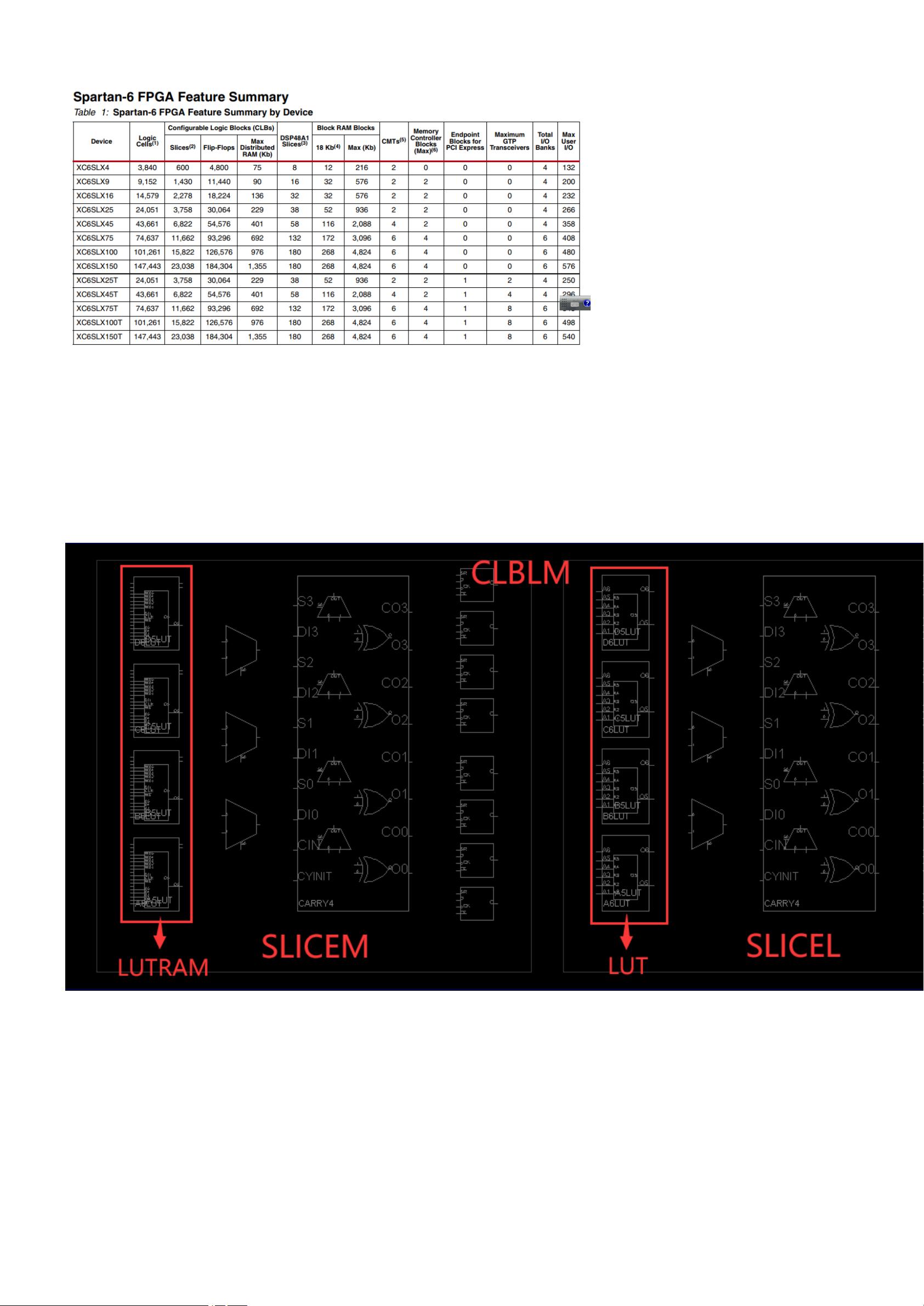

在FPGA(Field-Programmable Gate Array)设计中,了解其内部硬件资源至关重要。CLB,即Configurable Logic Block,是FPGA的基础构建模块,它由逻辑类和存储类的切片(Slice)组成,通常分为CLBLM和CLBLL两种类型。CLB内部的切片包括SLICEL和SLICEM,前者主要用于逻辑功能,后者则额外支持分布式RAM和移位寄存器。每个CLB由两个切片构成,它们并不直接相连,而是以列的形式排列。

每个Slice包含4个6输入的查找表(LUT)和8个触发器,以及多路复用器和算术进位逻辑。查找表是实现逻辑功能的核心,SLICEM通过LUT还能构建出分布式存储资源。在7系列FPGA中,SLICEL占约2/3,SLICEM占剩余的1/3。SLICE的位置通过X和Y编号进行定位,X编号表示切片在CLB内的位置,Y编号标识切片所在的行。

资源利用率是设计的关键考虑因素,例如,如果一个设计使用了18个Slice中的24个LUT单元,那么Slice利用率是18%,而LUT利用率是12%。这提示我们需要优化设计以提高资源使用效率。

此外,FPGA还包含了专门的乘法器资源——DSP48,它能提供比逻辑实现更快的乘法操作。尽管DSP48的数量有限,但它们对于需要高效运算的应用,如数字信号处理,是至关重要的。在资源紧张的情况下,若DSP48不足,设计者可能需要将乘法操作转换为逻辑实现,但这会牺牲速度和性能。

理解和有效地利用FPGA的CLB和DSP48资源对于实现高效的硬件设计至关重要。设计师需要根据具体需求,灵活分配和优化这些硬件资源,以达到最佳的设计性能和效率。在设计过程中,应持续监控资源利用率,并进行必要的优化,确保设计既能满足功能需求,又能充分利用FPGA的硬件潜力。

131 浏览量

2013-09-02 上传

2008-12-25 上传

点击了解资源详情

点击了解资源详情

2021-10-01 上传

2008-12-02 上传

2011-03-05 上传

点击了解资源详情

weixin_41925897

- 粉丝: 66

- 资源: 72

最新资源

- mathematicalPendulum

- JavaScript-modules-in-browser:在JavaScript中使用ECMAScript模块

- NodaChat:基于 Node.js、Express 4、Jade、Bootstrap 和 Socket.IO 的简单聊天

- 毕业设计&课设--毕业设计之SpringCloud-B2C电子商务平台App端.zip

- jwt-rsa:在一个简单的界面中结合了jsonwetokens和node-rsa的包装器

- Vali-it-projektid:我的训练营文件

- Excel模板财务收支报表5.zip

- angular-contacts:管理系统联系人列表

- Autour_de_DAG:G. Vezzosi在2013年Spring在巴黎7举行的研讨会周期的注释。

- Excel模板项目测试用例表.zip

- esp32_php:Ejercicios de prueba de PHP

- ui5-middleware-code-coverage:用于UIt工具的代码覆盖率检测器

- protolog:为所有变量添加全局日志方法

- 【地产资料】XX地产 培训专员考勤表.zip

- teachPro:问题管理系统

- uuidtools:一个简单的通用唯一ID生成库