上海大学数字电路应用实验指南:FPGA开发与Verilog设计

版权申诉

183 浏览量

更新于2024-06-29

收藏 2.86MB PDF 举报

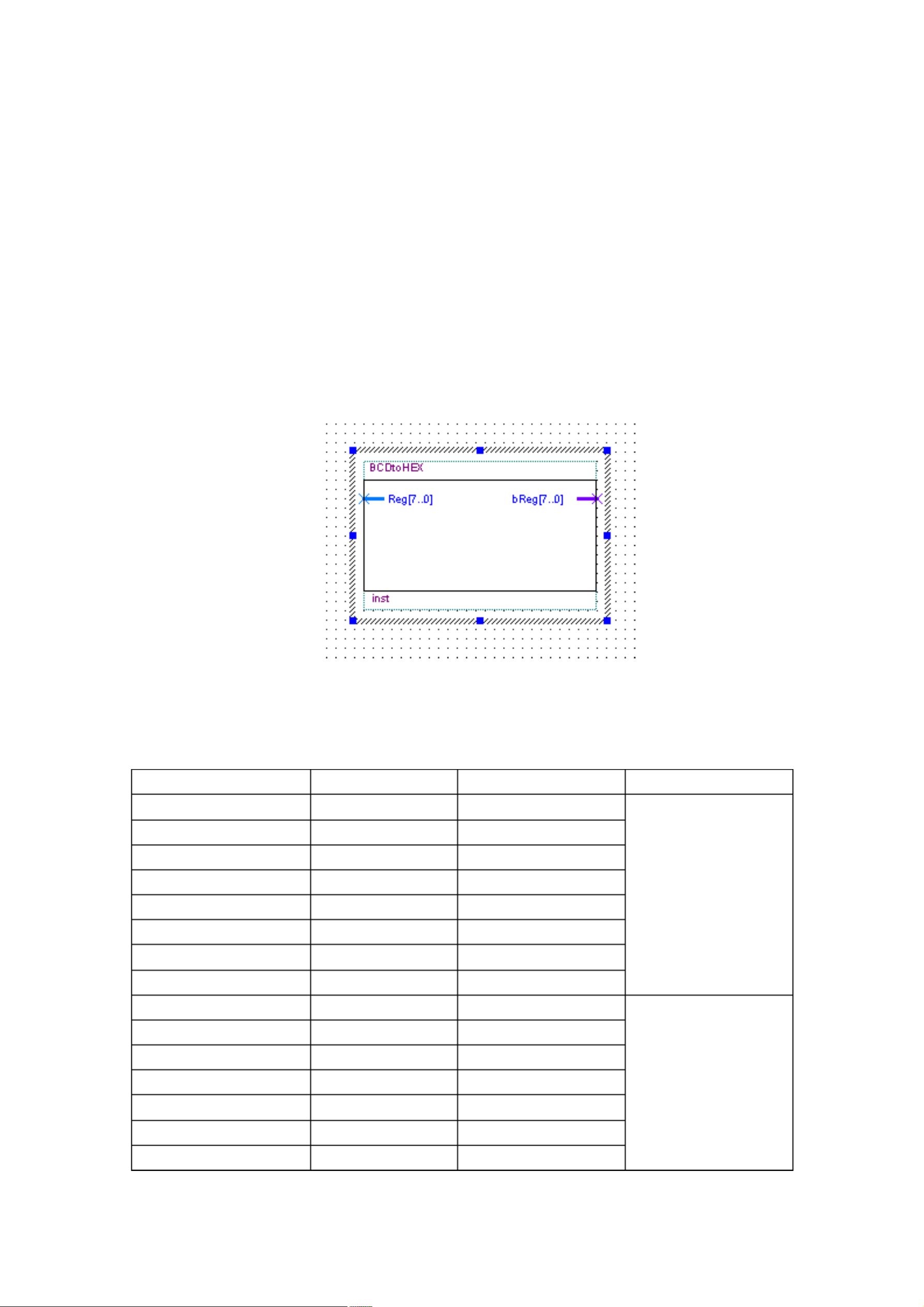

《数字电路应用实验指导书-开发板版本-20151219.pdf》是一份针对上海大学机电一体化工程中心学生的实验教材,用于辅助《数字电路A》课程的学习。这份文档详细介绍了在数字电路设计领域的实验内容,特别是针对集成电路和Verilog语言的应用。实验内容包括比较器、码制转换器、加法器、优先编码器、七段译码器、计数器、移位寄存器等基础逻辑功能模块的设计,旨在让学生掌握硬件设计语言Verilog的运用,以及FPGA/CPLD(现场可编程门阵列/复杂可编程逻辑器件)的开发过程。

该书强调了实验平台,即“易上手”系列FPGA开发套件和微型计算机组成的数字电路实验系统,通过这个平台,学生可以实践Verilog语言的编程和QuartusII开发环境的操作。实验设计旨在培养学生的实际操作能力和解决工程问题的能力,如设计数字逻辑电路,理解并处理不同码制之间的转换。

整个实验系统构建了一个模拟的颗粒灌装系统,通过拨码开关设置灌装目标,编码器将设定值转化为BCD码,存储在寄存器中,并通过译码器显示在数码管上。当颗粒落下时,光电传感器触发计数器,与预设的灌装数量进行比较,若码制不一致,则需先进行码制转换。比较成功后,系统会控制漏斗关闭,传送带换瓶,等待下一轮灌装。加法器在此过程中用于累加灌装总数。

此外,附录部分提供了开发套件ETL-005的核心板介绍,管脚位置约束以及QuartusII软件的使用指南,帮助学生更好地理解和操作实验设备。通过这些实验,学生不仅能深入理解数字电路的工作原理,还能提升他们的硬件编程和逻辑设计能力,为未来从事电子工程或相关领域的工作打下坚实的基础。

2019-05-11 上传

2021-03-12 上传

2009-07-02 上传

2023-11-11 上传

2024-01-19 上传

2023-12-15 上传

2023-11-05 上传

2023-11-08 上传

2023-06-26 上传

G11176593

- 粉丝: 6777

- 资源: 3万+

最新资源

- 最优条件下三次B样条小波边缘检测算子研究

- 深入解析:wav文件格式结构

- JIRA系统配置指南:代理与SSL设置

- 入门必备:电阻电容识别全解析

- U盘制作启动盘:详细教程解决无光驱装系统难题

- Eclipse快捷键大全:提升开发效率的必备秘籍

- C++ Primer Plus中文版:深入学习C++编程必备

- Eclipse常用快捷键汇总与操作指南

- JavaScript作用域解析与面向对象基础

- 软通动力Java笔试题解析

- 自定义标签配置与使用指南

- Android Intent深度解析:组件通信与广播机制

- 增强MyEclipse代码提示功能设置教程

- x86下VMware环境中Openwrt编译与LuCI集成指南

- S3C2440A嵌入式终端电源管理系统设计探讨

- Intel DTCP-IP技术在数字家庭中的内容保护