三段式状态机:思维陷阱与优化策略

需积分: 9 161 浏览量

更新于2024-09-09

收藏 124KB DOCX 举报

在设计状态机时,三段式结构被广泛认为具有诸多优点,尤其是在将组合逻辑和时序逻辑分离、提高综合器效率以及代码清晰度方面。然而,尽管如此,它并非适合所有开发者,特别是在思维方式上存在一些潜在陷阱。本文将深入探讨这些陷阱,特别是针对那些习惯于一段式状态机开发的工程师。

首先,三段式(通常包含三个基本阶段:输入处理、状态更新和输出计算)的优势在于它明确划分了逻辑过程,使得分析和维护变得更加直观。这有助于硬件设计师在系统Verilog或类似工具中进行逻辑优化,因为综合器能更好地理解和处理这种结构。此外,它也符合设计者通常遵循的分层逻辑思维模式,使得复杂逻辑更容易管理和理解。

然而,有些人可能会倾向于使用一段式(即在一个always块中处理所有状态变化),他们认为这种方式更直接,便于快速搭建功能模块。他们可能会先用一段式实现功能,然后在验证无误后转换成三段式,以期待性能提升。然而,这种做法可能隐藏了一个思维陷阱:从一段式到三段式的转变需要不同的逻辑思维方式,尤其是对于习惯了直接控制每个状态转移的开发者来说,这可能是个挑战。

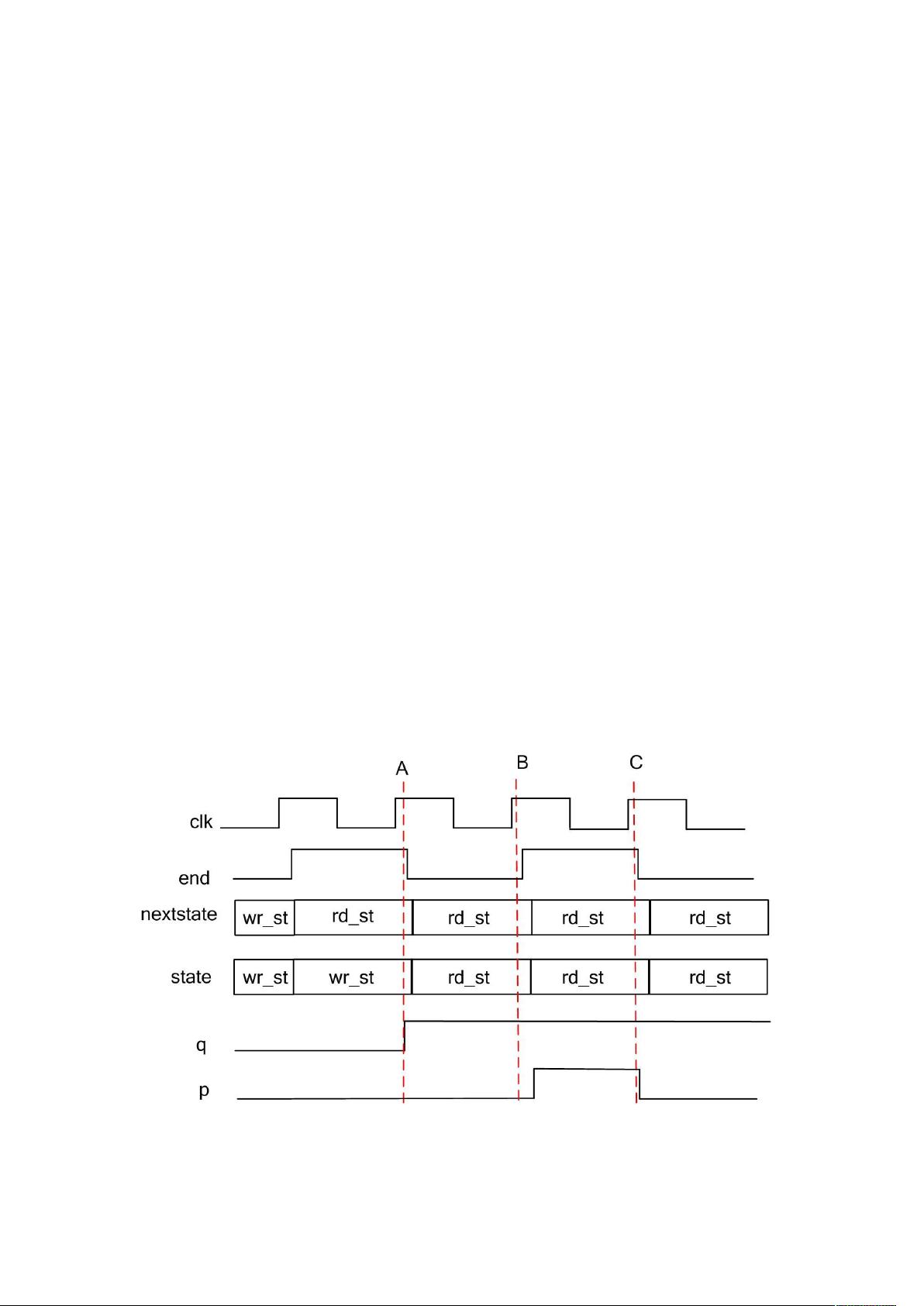

举例说明,假设有一个简单的状态机,初始状态wr_st,q和p的输出都是0。当计数器count达到10,输出end信号,状态机在接收到end有效后进入rd_st,并将q置为1。在rd_st状态,如果jump有效,则转至erase_st,否则根据end的有效性调整p的输出。一段式实现如下:

```verilog

assign end = (count == 10);

always @(posedge clk) begin

case(state)

wr_st: if (end) begin

q <= 1;

state <= rd_st;

end

else begin

q <= 0;

state <= wr_st;

end

rd_st: if (jump) begin

p <= 1;

state <= erase_st;

end

| (end) begin

p <= 0;

state <= rd_st;

end

default: begin

p <= 1;

state <= rd_st;

end

endcase

end

```

这段代码展示了如何在一段式中通过case语句处理状态间的转换。如果直接尝试将其转换为三段式,就需要将类似的逻辑拆分成三个独立的部分,分别处理输入处理、状态更新和输出计算,而这可能在初学者或不熟悉三段式思维方式的人中引起混淆或错误。

因此,当采用三段式设计时,应确保充分理解其逻辑结构和潜在的思维转变,并且根据个人的编程习惯和项目需求来选择最适合的方式。对于已经在一段式思维中得心应手的开发者,可能需要额外的时间和练习来适应三段式的状态机设计,以避免陷入思维陷阱并确保设计的正确性和效率。

1313 浏览量

1313 浏览量

738 浏览量

569 浏览量

点击了解资源详情

点击了解资源详情

点击了解资源详情

2025-03-12 上传

wangzepeng2009

- 粉丝: 0

最新资源

- NesEmulator: 开发中的Java NES模拟器

- 利用MATLAB探索植物生长新方法

- C#实现条形码自定义尺寸生成的简易方法

- 《精通ASP.NET 4.5》第五版代码完整分享

- JavaScript封装类实现动态曲线图绘制教程

- 批量优化图片为CWEPB并生成HTML5图片标签工具

- Jad反编译工具:Jadeclipse的下载与安装指南

- 基于MFC的图结构实验演示

- Java中的邮件推送与实时通知解决方案

- TriMED方言技术的最新进展分析

- 谭浩强C语言全书word版:深入浅出学习指南

- STM32F4xx开发板以太网例程源码解析

- C++实现的人力资源管理系统,附完整开发文档

- kbsp_schedule:实时监控俄技大IKBiSP项目日程变更

- Seqspert: 提升Clojure序列操作性能的高效工具

- 掌握Android反编译:jdgui、dex2jar、apktool工具应用