Xilinx ML555 DDR2调试与MT47H128M16XX控制详解

DDR2调试记录是一份详细记录了在MIG控制器下对DDR2内存进行调试的过程文档,主要针对Xilinx公司的VIRTEX5-xc5vlx50t-ff1136 FPGA平台进行设计。该硬件环境基于ML555官方开发板简化版,配备两组DDR2模块,每组由4片MT47H128M8HQ-3IT组成,形成32位宽的数据传输。然而,为了节省资源,FPGA内部通过一片MT47H128M16XX-37E芯片实现32位宽的控制,同时共享一组控制线。

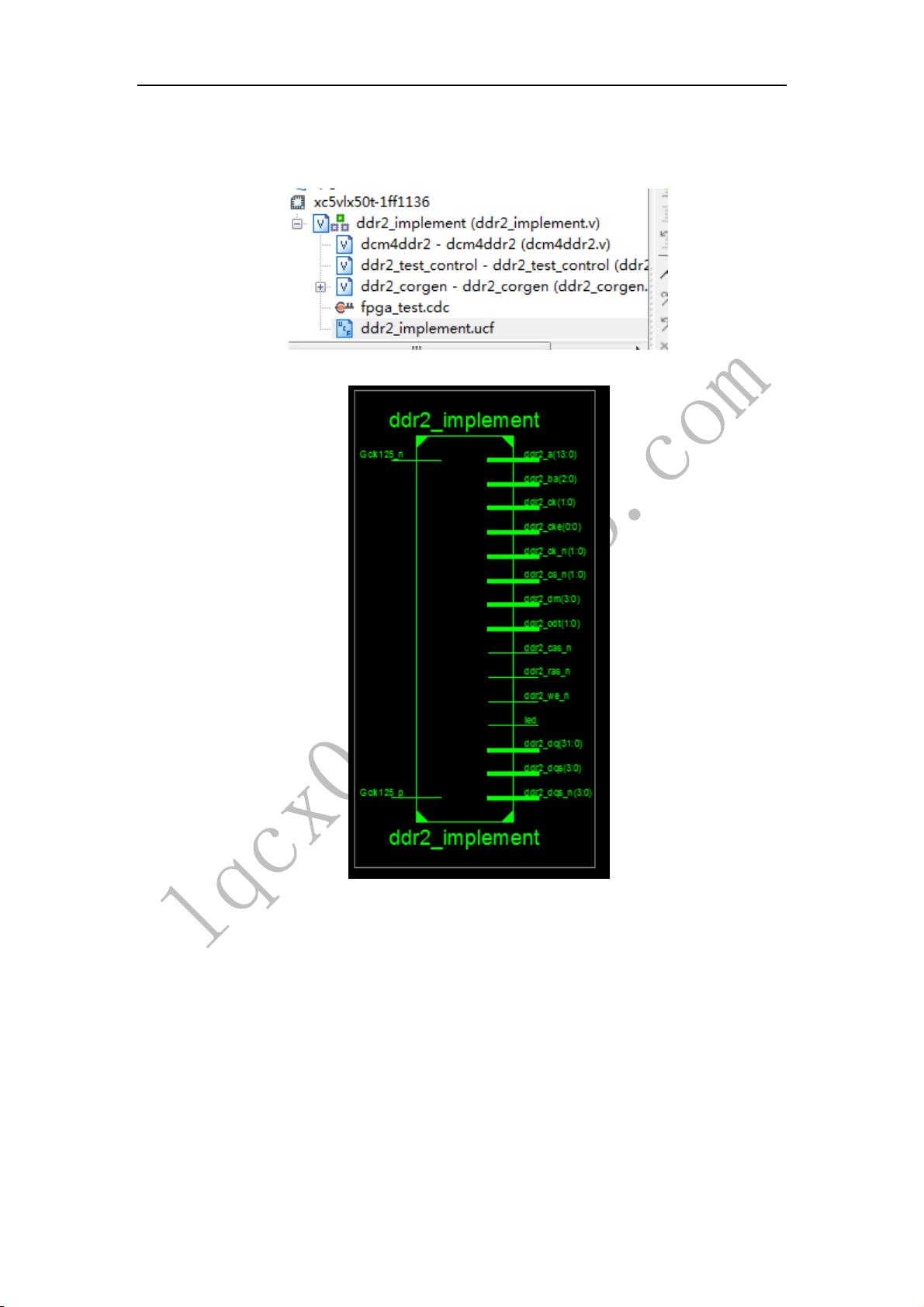

软件配置部分,开发者采用了无TESTBENCH和PLL的简洁设计。系统架构包括dcm4ddr2模块用于生成必要的时钟信号,ddr2_test_control模块负责控制IP核的操作,以及对DDR2的读写测试,通过状态机实现信号的发送和接收。该模块的测试原理是先执行burst写操作,随后读取相同地址的数据,验证写入和读出的数据一致性。

ddr2_corgen模块是系统内核的实例化IP,而核心步骤是使用coregen工具创建新工程,并利用MIG模块来生成DDR2控制器IP。在实际使用中,如果用户时钟不是200M,可能需要在读写端添加FIFO以适应不同工作频率。

这份记录对于学习DDR2在FPGA上的调试和接口控制具有很高的参考价值,可以帮助读者理解如何在实际硬件环境中设计和测试此类内存控制器,以及软件层面的控制策略和注意事项。

点击了解资源详情

2014-02-17 上传

2012-12-11 上传

112 浏览量

116 浏览量

157 浏览量

wujingan870316

- 粉丝: 1

- 资源: 2

最新资源

- another-round:另一轮琐事游戏

- RabbitMQ-Demo.zip

- Story-app-2:故事应用

- c-simple-libs:简单,干净,仅标头,C库

- SoftEngG1B:软件工程项目

- 水晶动物图标下载

- 可执行剑:关于剑的游戏

- monke-lang:德蒙克的威

- 虎皮鹦鹉图标下载

- Django_Personal_Portfolio:使用Django制作的投资组合网站

- hassant5577.github.io

- shaarlo:统一Shaarlis Rss

- 4boostpag

- Công Cụ Đặt Hàng Của Express-crx插件

- 米老鼠图标下载

- AdaptableApp:CITRIS 应用程序竞赛