电源完整性设计:噪声分析与去耦策略

需积分: 3 78 浏览量

更新于2024-07-21

收藏 285KB PDF 举报

"电源完整性设计详解,电源设计基础,电源噪声问题,电容退耦,去耦设计,电源系统的角度,目标阻抗,电容组合选择"

电源完整性设计是电子设备设计中的关键环节,它涉及到电源系统如何有效地为集成电路提供稳定、低噪声的电源,以确保系统的正常运行和高性能。电源噪声问题是电源完整性设计必须关注的重点,因为现代集成电路内部的晶体管数量庞大,共同共享电源引脚,导致噪声易于传播并影响芯片内部的逻辑状态。

电源噪声主要来源于两方面:一是内部晶体管状态转换不同时造成的瞬态电流波动;二是外部环境因素如开关电源的纹波、电磁干扰等。这些噪声如果未得到妥善处理,可能导致电路逻辑错误、时序问题以及性能下降。

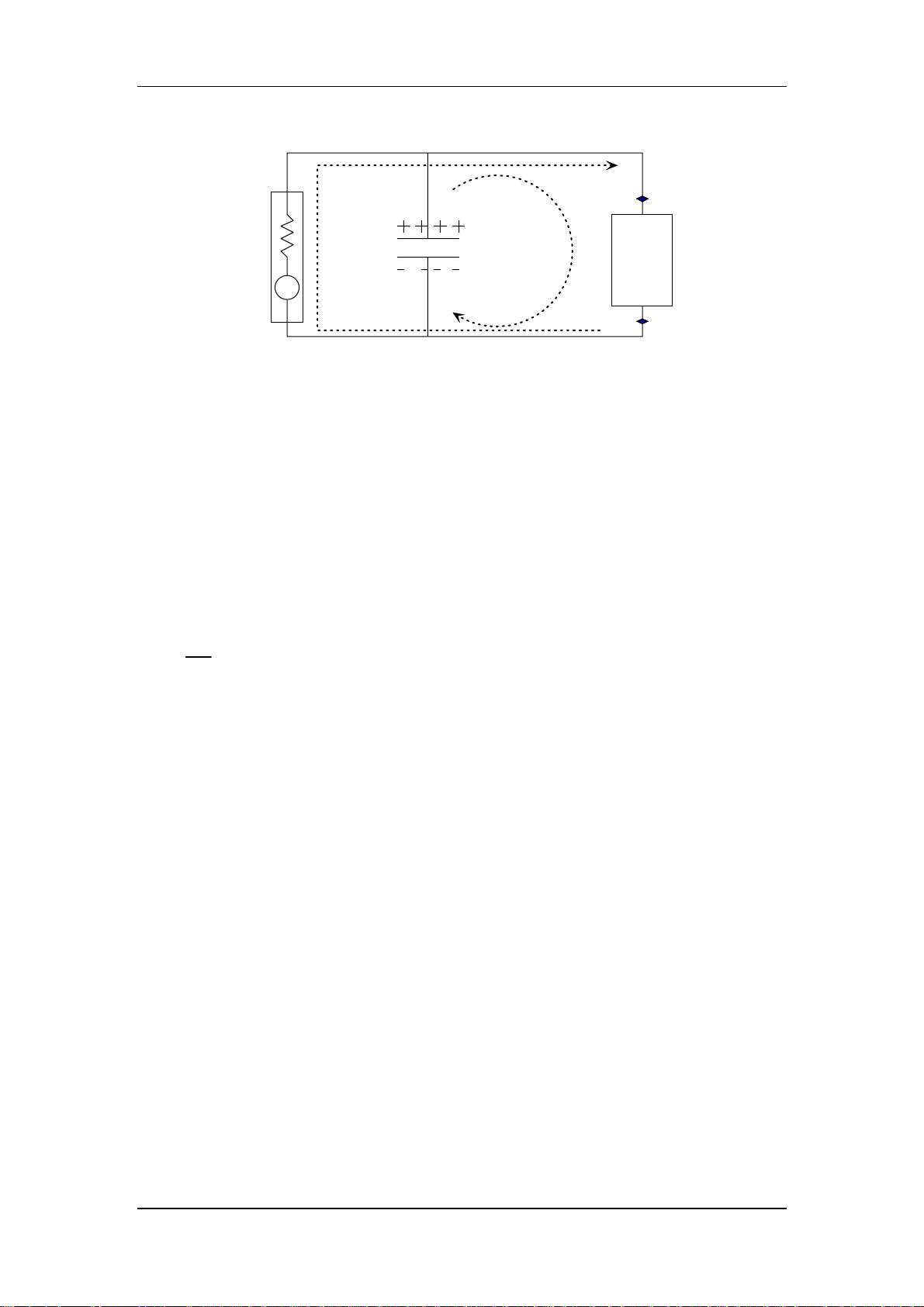

电容退耦是解决电源噪声的有效手段,可以从储能和阻抗两个角度理解。储能角度看,电容可以存储能量并在需要时释放,以补偿电源电压的波动;从阻抗角度看,电容可以降低电源路径的阻抗,减少噪声对负载的影响。实际电容具有频率响应特性,其效果受到安装位置、谐振频率等因素影响。

电容的安装谐振频率是指电容与引线电感组成的LC谐振电路的工作频率,这个频率决定了电容在多大频率范围内能有效退耦。局部去耦设计方法强调了在靠近负载的位置放置电容,以缩短电源路径,减小噪声传播。

去耦设计通常基于目标阻抗,即希望电源网络在工作频率范围内的阻抗保持恒定,避免产生噪声放大。选择电容的大小和数量时,需要考虑负载的电流需求和预期的噪声水平。相同容值电容并联可以增加总电容值,而不同容值电容的并联则可以扩展有效频率范围,但需注意可能出现的反谐振现象,ESR(等效串联电阻)会影响反谐振点。

电容的去耦半径是指电容对周围负载的覆盖范围,它影响了电容提供瞬态电流的能力。电容的安装方法也至关重要,正确的安装可以减少引线电感的影响,提高退耦效果。

电源完整性设计是一个涉及多方面因素的综合工程,包括电容的选择、布局、并联策略等,设计师需要深入理解这些原理,以实现高效且低噪声的电源系统。

2016-06-05 上传

2024-10-27 上传

2024-10-27 上传

2024-10-27 上传

bink2013

- 粉丝: 0

- 资源: 2

最新资源

- C++ Qt影院票务系统源码发布,代码稳定,高分毕业设计首选

- 纯CSS3实现逼真火焰手提灯动画效果

- Java编程基础课后练习答案解析

- typescript-atomizer: Atom 插件实现 TypeScript 语言与工具支持

- 51单片机项目源码分享:课程设计与毕设实践

- Qt画图程序实战:多文档与单文档示例解析

- 全屏H5圆圈缩放矩阵动画背景特效实现

- C#实现的手机触摸板服务端应用

- 数据结构与算法学习资源压缩包介绍

- stream-notifier: 简化Node.js流错误与成功通知方案

- 网页表格选择导出Excel的jQuery实例教程

- Prj19购物车系统项目压缩包解析

- 数据结构与算法学习实践指南

- Qt5实现A*寻路算法:结合C++和GUI

- terser-brunch:现代JavaScript文件压缩工具

- 掌握Power BI导出明细数据的操作指南