使用ModelSim进行VHDL仿真的详细指南

需积分: 10 47 浏览量

更新于2024-07-18

收藏 362KB PPT 举报

"这份资料详细介绍了如何使用VHDL进行仿真,特别强调了使用ModelSim这一混合仿真器来配合QuartusII进行VHDL设计的验证。它适合初学者入门,同时也帮助深入理解VHDL仿真的系统流程。资料内容涵盖了从启动ModelSim、建立仿真工程、编译设计文件、装载模块到执行仿真和查看波形的全过程,并通过模16计数器的实例进行了演示。"

在电子设计自动化(EDA)领域,VHDL是一种广泛使用的硬件描述语言,用于描述数字系统的逻辑功能。它不仅可用于设计,还可用于对这些设计进行仿真验证。VHDL仿真允许设计者在实际硬件实现之前检查和调试他们的设计,确保其正确性和性能。

描述中的“VHDL仿真比较全比较细”意味着这份资料提供了详尽的步骤和指导,覆盖了从基础到进阶的多个方面。通过学习,读者能够掌握如何在ModelSim环境中设置和运行VHDL仿真,这对于理解和优化FPGA(Field Programmable Gate Array)设计至关重要。

ModelSim是一个强大的VHDL和Verilog仿真工具,由Mentor Graphics公司开发。它可以处理复杂的仿真任务,包括功能仿真和时序仿真。在QuartusII中,虽然也可以进行仿真,但其基于综合后的网表,可能无法展现所有设计细节。相比之下,ModelSim的独立仿真能力使得设计者能更细致地检查设计行为。

资料中的实例——模16计数器,展示了如何定义一个实体和结构体,以及如何在过程中处理时钟边沿触发的计数操作。通过ModelSim,设计者可以观察信号变化,如rst和clk输入,以及q输出的波形,从而验证计数器是否按预期工作。

仿真过程包括以下几个步骤:

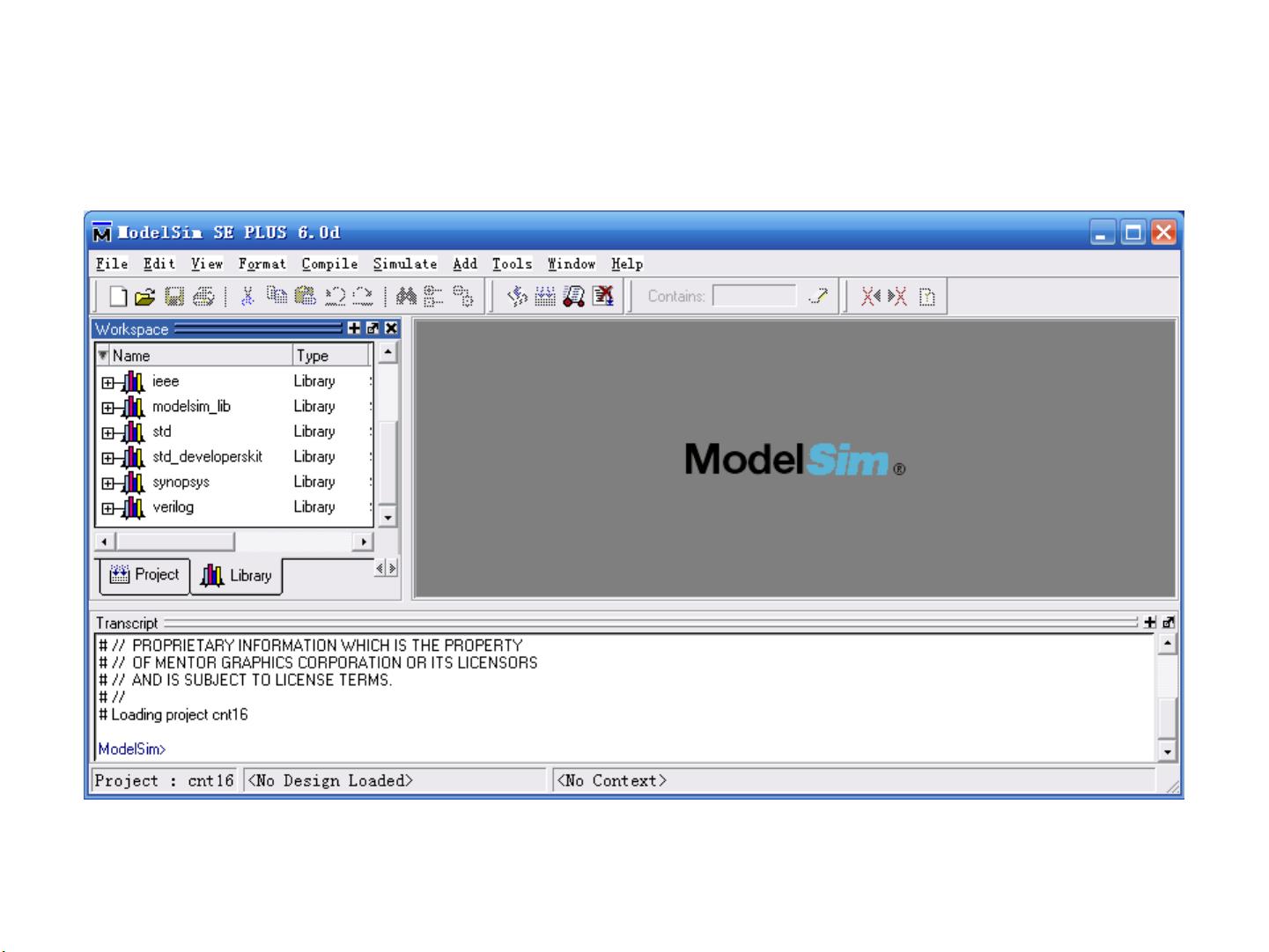

1. **启动ModelSim**:打开软件并创建一个新的工作空间。

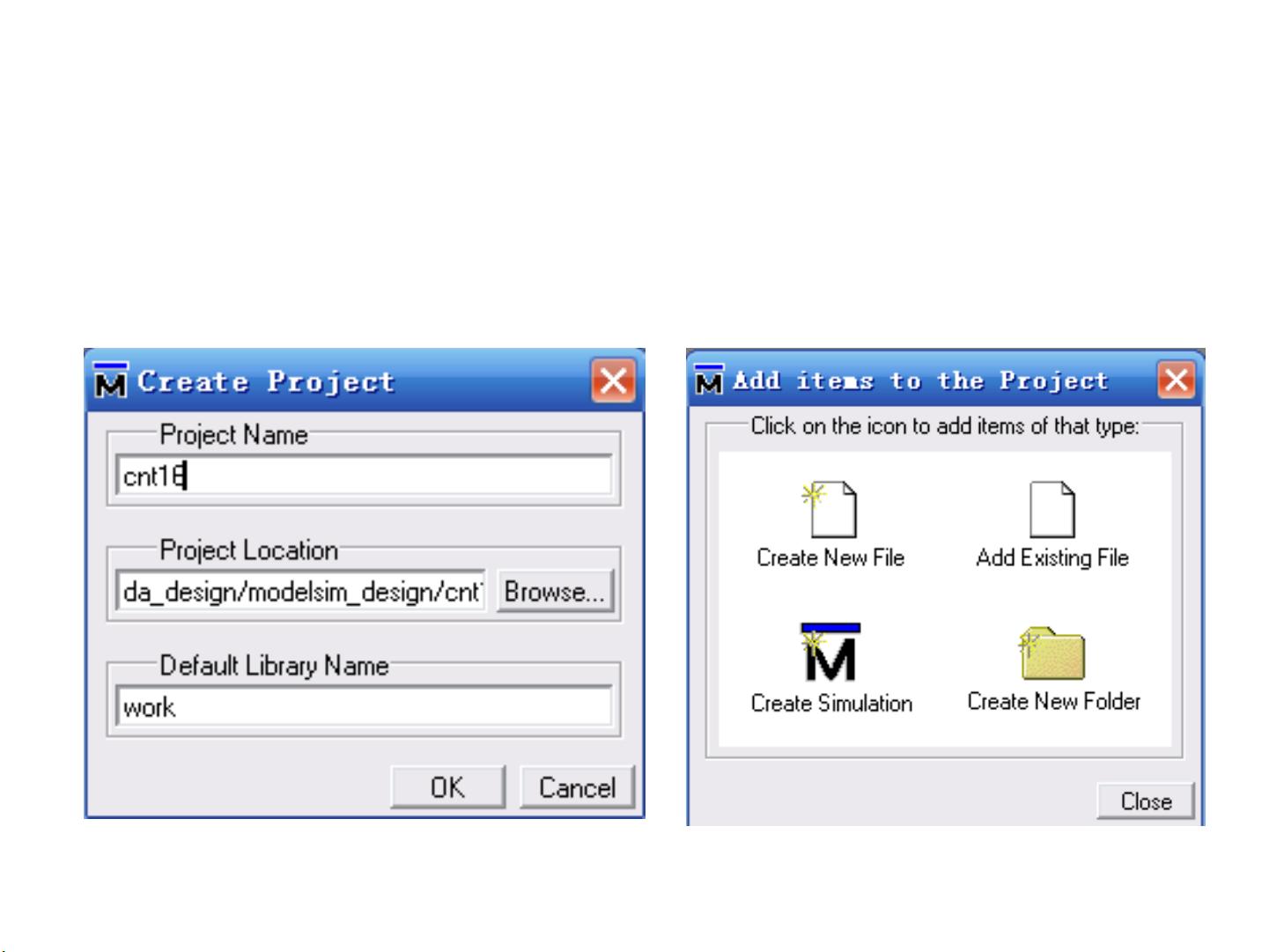

2. **建立仿真工程**:在ModelSim中创建一个新的项目,将VHDL设计文件添加到工程中。

3. **编译仿真文件**:编译设计文件以生成仿真模型,确保没有语法或逻辑错误。

4. **装载仿真模块和仿真库**:导入必要的库和设计模块,以便在仿真环境中使用。

5. **执行仿真**:设置输入波形,例如手动编辑或通过测试向量(testbench)来模拟设计的输入条件,然后运行仿真。

6. **查看波形**:在ModelSim的波形观察窗口中分析仿真结果,验证设计的行为。

通过这份资料,学习者可以系统地了解和实践VHDL仿真的完整流程,这对于FPGA开发者来说是一项必不可少的技能,有助于提升设计质量和效率。

2015-04-17 上传

2011-12-20 上传

2022-09-23 上传

2007-07-12 上传

2019-07-23 上传

2022-09-14 上传

2022-09-24 上传

2021-02-14 上传

syzhptpeter

- 粉丝: 5

- 资源: 8

最新资源

- BottleJS快速入门:演示JavaScript依赖注入优势

- vConsole插件使用教程:输出与复制日志文件

- Node.js v12.7.0版本发布 - 适合高性能Web服务器与网络应用

- Android中实现图片的双指和双击缩放功能

- Anum Pinki英语至乌尔都语开源词典:23000词汇会话

- 三菱电机SLIMDIP智能功率模块在变频洗衣机的应用分析

- 用JavaScript实现的剪刀石头布游戏指南

- Node.js v12.22.1版发布 - 跨平台JavaScript环境新选择

- Infix修复发布:探索新的中缀处理方式

- 罕见疾病酶替代疗法药物非临床研究指导原则报告

- Node.js v10.20.0 版本发布,性能卓越的服务器端JavaScript

- hap-java-client:Java实现的HAP客户端库解析

- Shreyas Satish的GitHub博客自动化静态站点技术解析

- vtomole个人博客网站建设与维护经验分享

- MEAN.JS全栈解决方案:打造MongoDB、Express、AngularJS和Node.js应用

- 东南大学网络空间安全学院复试代码解析