Verilog设计基础:新建文件与综合实战

需积分: 9 78 浏览量

更新于2024-07-21

收藏 2.54MB PDF 举报

本篇教程详细介绍了如何在Xilinx ISE软件环境下使用Verilog硬件描述语言进行FPGA设计的基本步骤,主要针对的是数字电路设计和Verilog语言的应用。作者尹仕包文博在2014年5月29日分享了Xilinx FPGA开发设计流程,包括建立工程、创建和添加设计源文件、综合、仿真、添加约束文件以及实现和下载。

首先,建立工程是整个过程的起点,用户需要在软件中创建一个新的项目。在这个阶段,理解Verilog HDL(Hardware Description Language)的重要性,它是描述数字电路行为的语言,能够将抽象的逻辑描述转化为实际的硬件实现。

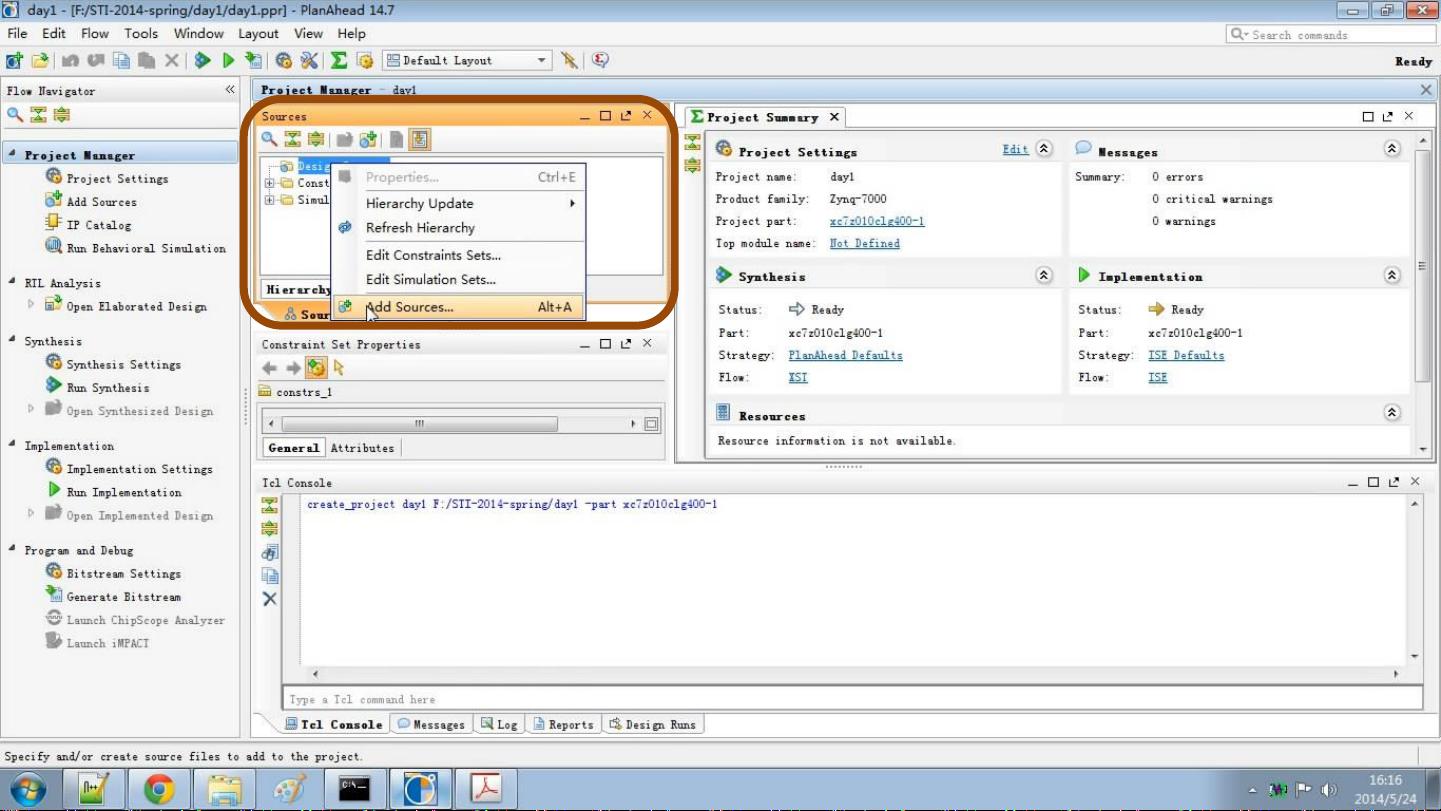

创建设计源文件是核心步骤之一,这里使用的是Verilog语言编写。以逻辑门电路(如与、或、非门)为例,用户需要通过右键菜单选择"AddSources",并创建一个新的文件,命名为day1_gatelevel.v。在这个文件中,定义了一个模块(module)day1_gatelevel,它接受两个输入(sw)和控制三个输出(led),通过实例化不同的门电路实现了功能:一个拨码开关控制LED 0的与操作,另一个控制LED 1的或操作,第三个LED 2由一个拨码开关的非操作决定。

综合(synthesis)是将Verilog代码转换为逻辑门级的电路结构,这是确保代码符合硬件实现的关键步骤。用户需确保代码语法正确,保存文件后,软件会自动生成逻辑实现。在综合过程中,可以观察到实际的电路实现,以便于理解和优化设计。

接下来是建立和添加仿真源文件(RTL simulation),用于验证设计在逻辑层面上是否符合预期。这有助于早期发现潜在的问题,并且在实际硬件实现之前进行测试。

约束文件(Constraints)对于精确的布局和布线至关重要,它们定义了FPGA的物理位置和引脚分配。在设计过程中,这些文件需要根据具体情况进行创建和管理。

最后,设计实现(implementation)是将综合后的逻辑映射到目标芯片,生成比特流文件,准备下载到开发板上进行测试。这一阶段可能会涉及到时序分析和优化,以确保性能满足设计要求。

这篇教程不仅介绍了如何在Xilinx ISE中创建和管理Verilog设计,还涵盖了基本的硬件描述和设计流程,对初学者来说是一份实用的指南。

1071 浏览量

154 浏览量

2022-09-23 上传

131 浏览量

2022-06-17 上传

2128 浏览量

2022-09-21 上传

qq_24473971

- 粉丝: 0

- 资源: 1

最新资源

- ImageAnnotation:有关如何使用Photoshop提取视频帧和注释图像的教程。 提供了两个脚本来计算每个类别的覆盖率和图像大小(R和Matlab)

- mixchar:R包“ mixchar”的存储库

- MFCApplication1.rar

- 在安卓上使用的app例程

- test01:这只是一个git测试库。 测试Git及其功能

- MFC自定义按钮实现

- part_2a_decoding_with_loops.zip

- 行业文档-设计装置-一种具有储水功能的花盆.zip

- EVERSON

- 个人偏好:这些是我使用的所有东西,可能会忘记的事情。 所以我把它们都收集在这里。 这可能对您有用:)

- 验证码训练、识别数据集,共1070个验证码图片

- 华科网络内容管理系统 v5.3 手机+PC

- SSM整合jar包

- matlab确定眼睛的代码-BME3053C-final-project:实验大鼠鬼脸秤的机器识别

- Naga-Phaneendra.Ghantasala_152681_phase2

- 行业文档-设计装置-一种平台升降装置.zip