深入解析UVM验证方法学与Testbench构建

"UVM验证方法学深入讲解,包含多种实例,教授如何利用UVM构建Testbench模块,由MENTOR GRAPHICS提供的一份详细的在线烹饪书,涵盖了从Testbench架构到组件、代理、阶段管理、工厂机制、系统Verilog包、与DUT接口的连接、参数化测试以及配置等多个方面。"

在UVM(Universal Verification Methodology)验证方法学中,它提供了一套标准化的框架和库,用于构建和复用可扩展的验证环境。UVM的核心理念是基于组件的验证,它将验证环境划分为多个可重用的部分,如Testbench、组件、代理、驱动、监控器等,从而提高验证效率和代码质量。

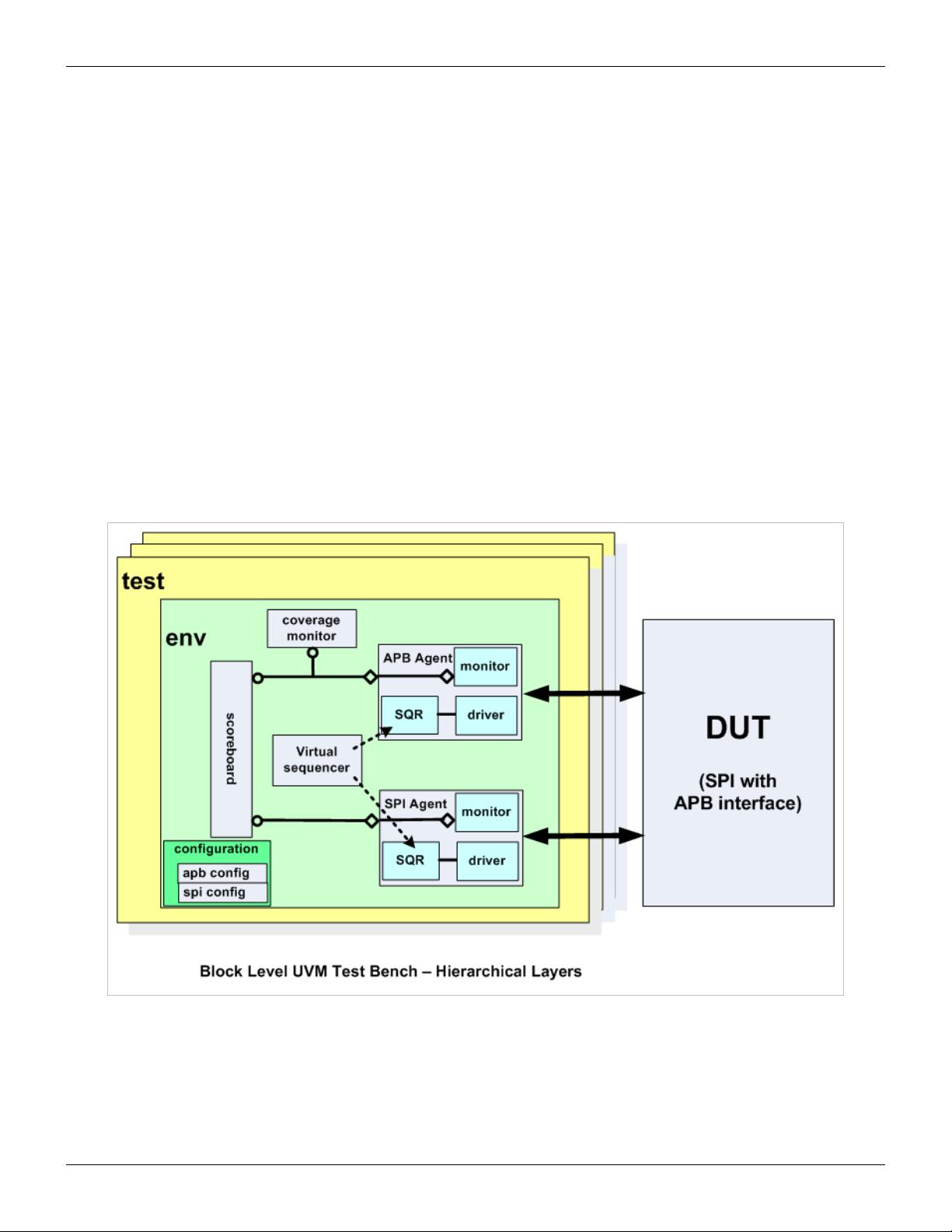

1. **Testbench架构**:Testbench是验证环境的基石,它模拟了被验证设计(DUT,Design Under Test)运行的环境。Testbench通常包括激励生成器、响应分析器、 scoreboard和其他辅助组件。`Testbench/Overview`介绍了Testbench的基本结构,`Testbench/Build`则讲解了如何构建Testbench,而`Testbench/Blocklevel`和`Testbench/IntegrationLevel`分别针对模块级和系统级集成的Testbench设计进行了探讨。

2. **组件(Component)**:UVM组件是构建验证环境的基本单元,它们可以是简单的数据处理模块,也可以是复杂的测试序列生成器。`Component`章节详细阐述了组件的创建、配置和连接。

3. **代理(Agent)**:代理是连接DUT接口和Testbench的桥梁,它包括驱动(Driver)、监控器(Monitor)和收发机(Sequencer)。`Agent`部分解释了如何定义和使用这些组件来实现有效的通信。

4. **阶段管理(Phasing)**:UVM的时序模型允许在不同验证阶段执行不同的任务,如初始化、运行测试、报告结果等。`Phasing/Overview`和`Using Factory Overrides`讲述了如何管理和定制这些验证阶段。

5. **工厂(Factory)**:工厂机制允许动态地创建和配置UVM对象,提供了灵活的类实例化和类型映射。`Factory`和`Using Factory Overrides`部分深入讲解了这一关键特性。

6. **系统Verilog包(SystemVerilog Packages)**:UVM基于SystemVerilog语言,系统Verilog包定义了UVM的基础类和接口。`SystemVerilogPackages`章节解释了如何使用和扩展这些包。

7. **与DUT接口的连接(Connecting to DUT Interfaces)**:这部分涵盖了如何将Testbench组件与DUT接口进行连接,包括`Connect/DutInterface`、`SVCreationOrder`和`Connect/SystemVerilogTechniques`等,讨论了接口的虚拟化和连接策略。

8. **参数化测试(Parameterized Tests)**:`ParameterizedTests`章节介绍如何创建能够适应不同输入参数的测试用例。

9. **虚拟接口(Virtual Interface)**:`VirtualInterface`相关章节讲解了如何使用虚拟接口来传递和处理协议数据,以及如何配置和管理这些接口。

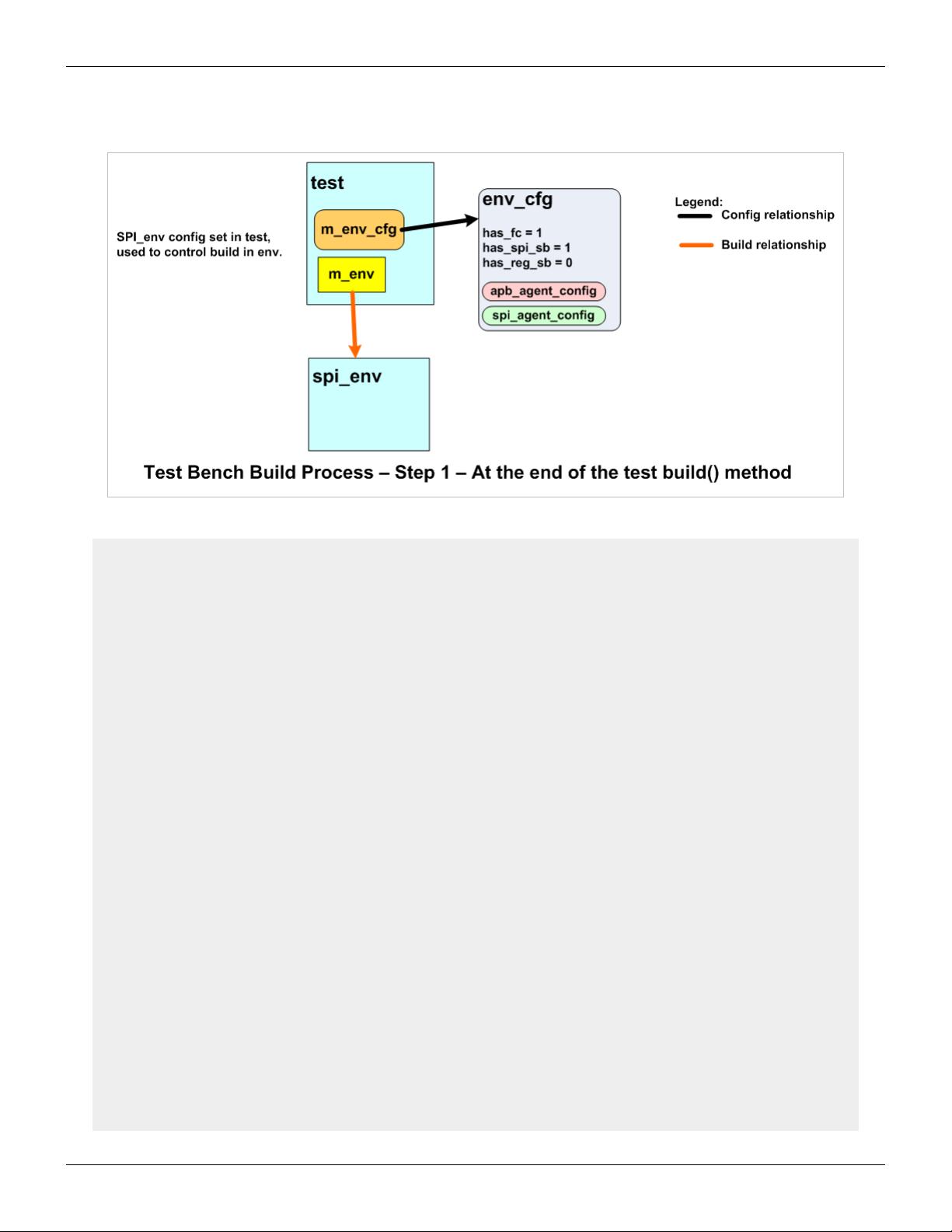

10. **配置(Configure)**:配置管理是UVM的重要特性,它允许在运行时对组件进行定制。`Configuring a Test Environment`章节详细介绍了配置数据库(Config DB)和配置过程。

这份文档通过实例和详细说明,帮助读者理解并掌握UVM验证方法学的各个方面,是学习和应用UVM进行SoC验证的宝贵参考资料。无论是初学者还是经验丰富的验证工程师,都能从中受益。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2022-09-04 上传

2021-07-26 上传

2022-07-05 上传

2021-09-06 上传

2021-09-06 上传

奋进的蜗牛

- 粉丝: 1

- 资源: 1

最新资源

- BootcampX

- snappy-cli:snappy-cli,用于通过snappy压缩文件的cli实用程序

- Analizador-Lexico:程序读取输入字符串,并根据用户加载的规则逐个字符地解释指令。

- Calculadora de Sueldos y Salarios:奖金,资历,薪酬,加班费,预算等-开源

- scipher:学术信息编码器

- xiejia1995.github.io:测试

- 三角函数运算指令.zip西门子PLC编程实例程序源码下载

- squirrel

- Pinescript实验室:Pinescript存储库

- OSRS-DropSimulator:osrs的一种工具,它可以从古老学校的runescape中掉落的东西中掠夺的东西得到大概的掠夺

- 行业分类-设备装置-可重写盘状介质上的多暂停记录.zip

- servantBot:不和谐仆人机器人

- vaguCinemaPlayer

- 背包:用于整数和有理数的精确算法:无边界的1-0 M维背包,N向总和分区,T组N总和分区和MKS问题

- littletrees:小树

- bestplugstore