10

CDCE6214-Q1

ZHCSK34A –AUGUST 2019–REVISED DECEMBER 2019

www.ti.com.cn

Copyright © 2019, Texas Instruments Incorporated

(1) Output Common Mode voltage and Differential output swing is dependent upon register settings DIFFBUF_IBIAS_TRIM,

LVDS_CMTRIM_DEC and LVDS_CMTRIM_INC. Parameters defined for DIFFBUF_IBIAS_TRIM=6h, LVDS_CMTRIM_DEC=0h and

LVDS_CMTRIM_INC=0h. Output Common Mode tested at DC.

(2) OUT1/OUT4 and OUT2/OUT3 are matched pair-wise. OUT1/OUT4 has LVCMOS buffer while OUT2/OUT3 do not have LVCMOS

buffer. OUT1/OUT4 is matched within T

OUT-SKEW

. OUT2/OUT3 is matched within T

OUT-SKEW

. There is an additional skew 150 ps- 250 ps

between OUT1/OUT4 and OUT2/OUT3.

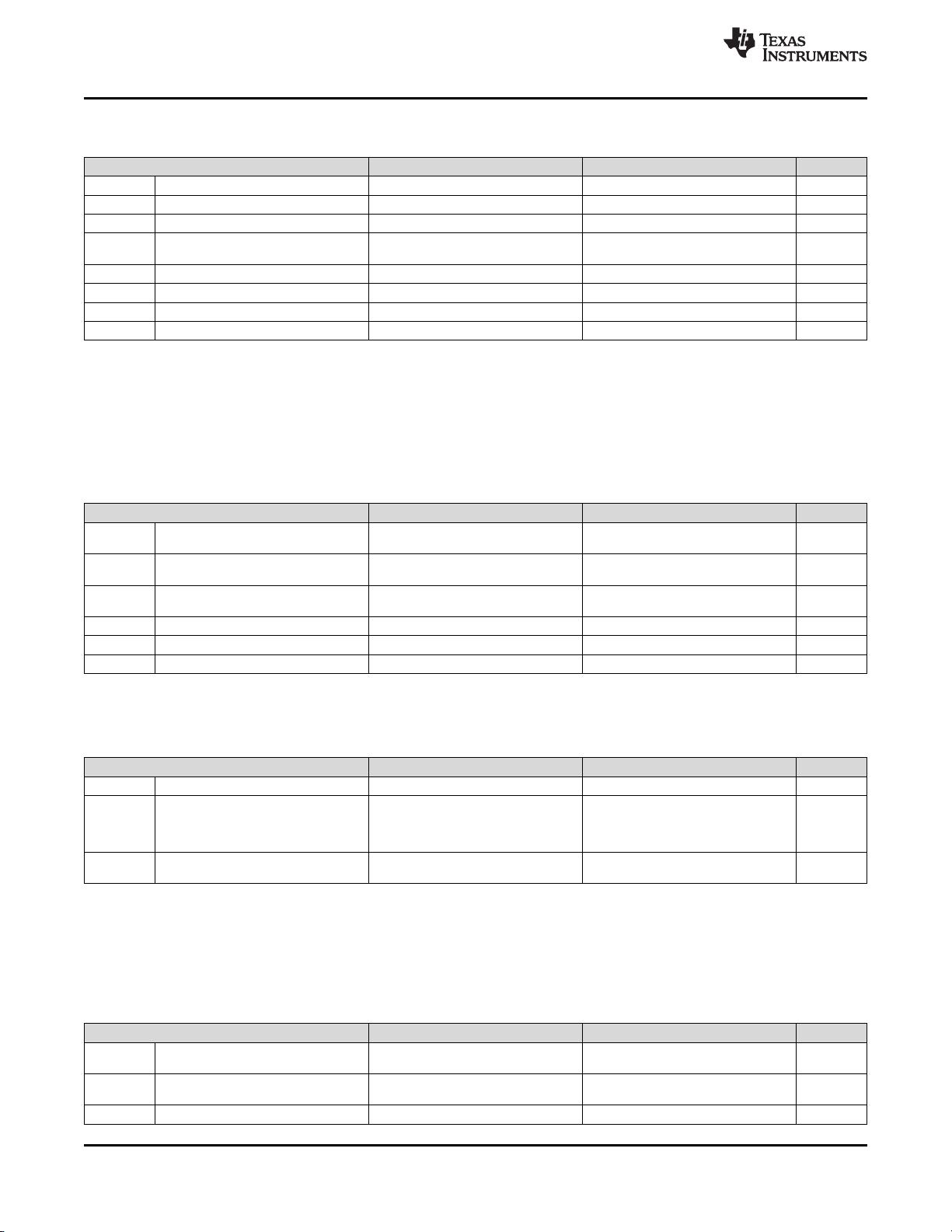

7.19 LVDS Output Characteristics

VDD_VCO, VDDO_12, VDDO_34, VDD_REF = 1.8 V ± 5%, 2.5 V ± 5%, 3.3 V ± 5% and T

A

= -40°C to 105°C

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

f

O_PRG_AC

Output frequency 0.024 350 MHz

V

CM

Output common mode

(1)

VDDO_X = 2.5 V, 3.3 V 1.025 1.2 1.375 V

V

CM

Output common mode

(1)

VDDO_X = 1.8 V 0.85 0.95 1.05 V

V

OD

Differential output voltage

(1)

VDDO_X = 1.8 V (F

out

< 200 MHz), 2.5 V,

3.3 V.

0.25 0.30 0.45 V

V

OD

Differential output voltage

(1)

VDDO_X = 1.8 V & F

out

> 200 MHz 0.22 0.30 0.45 V

t

RF

Output rise/fall times LVDS (20% to 80%) 450 650 900 ps

ODC Output duty cycle Not in PLL bypass mode 45 55 %

T

OUT-SKEW

Output skew

(2)

Same divide value, LVDS to LVDS output 100 ps

(1) Output clock cycles of respective output channel. Global output enable handled by digital logic, additional propagation will be added.

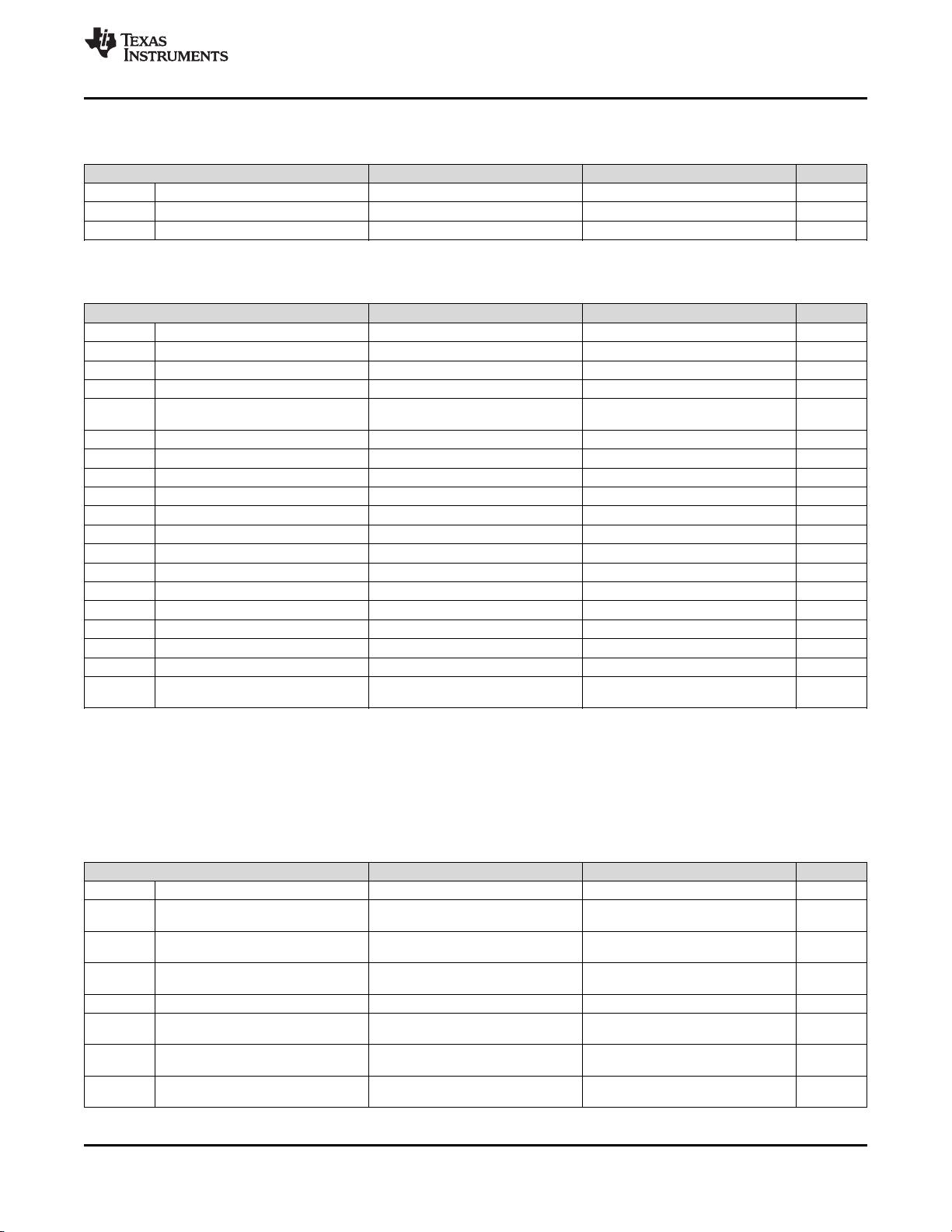

7.20 Output Synchronization Characteristics

VDD_VCO, VDDO_12, VDDO_34, VDD_REF = 1.8 V ±5%, 2.5 V ±5%, 3.3 V ±5% and T

A

= -40°C to 105°C

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

t

SU_SYNC

Setup time SYNC pulse

with respect to PLL reference rising edge

at 100 MHz with R=1

3 ns

t

H_SYNC

Hold time SYNC pulse

with respect to PLL reference rising edge

at 100 MHz with R=1

3 ns

t

PWH_SYNC

High pulse width for SYNC

With R = 1, at least 2 PFD periods + 24

feedback pre-scaler periods

60 ns

t

PWL_SYNC

Low pulse width for SYNC With R = 1, at least 1 PFD period 6 ns

t

EN

Individual output enable time

(1)

tri-state to first valid rising edge 4 nCK

t

DIS

Individual output disable time

(1)

last valid falling edge to tri-state 4 nCK

(1) POR threshold voltage is the power supply voltage at which the internal reset is deasserted. It is qualified internally with PDN.

(2) VDD pin should monotonically reach 95% of its final value within supply ramp time. Parameters specified by characterization. All VDD

pins were tied together for this evaluation. For non-monotonic or slower power supply ramp, it is recommended to pull-down PDN pin

until VDD pins have reached 95% of its final value. PDN pin has a 50 kΩ pullup resistor. When PDN pin cannot be actively controlled, TI

recommends to add a capacitor to GND on PDN pin to delay the release of reset.

7.21 Power-On Reset Characteristics

VDD_VCO, VDDO_12, VDDO_34, VDD_REF = 1.8 V ± 5%, 2.5 V ± 5%, 3.3 V ± 5% and T

A

= -40°C to 105°C

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

V

THRESHOLD

POR threshold voltage

(1)

0.875 1.275 V

t

STARTUP

Start-up time

Start-up time after VDD reaches 95% to

the time outputs are toggling with correct

frequency (input = crystal or external

clock)

9 ms

t

VDD

Power supply ramp time

(2)

timing requirement for any VDD pin while

PDN=LOW

0.1 30 ms

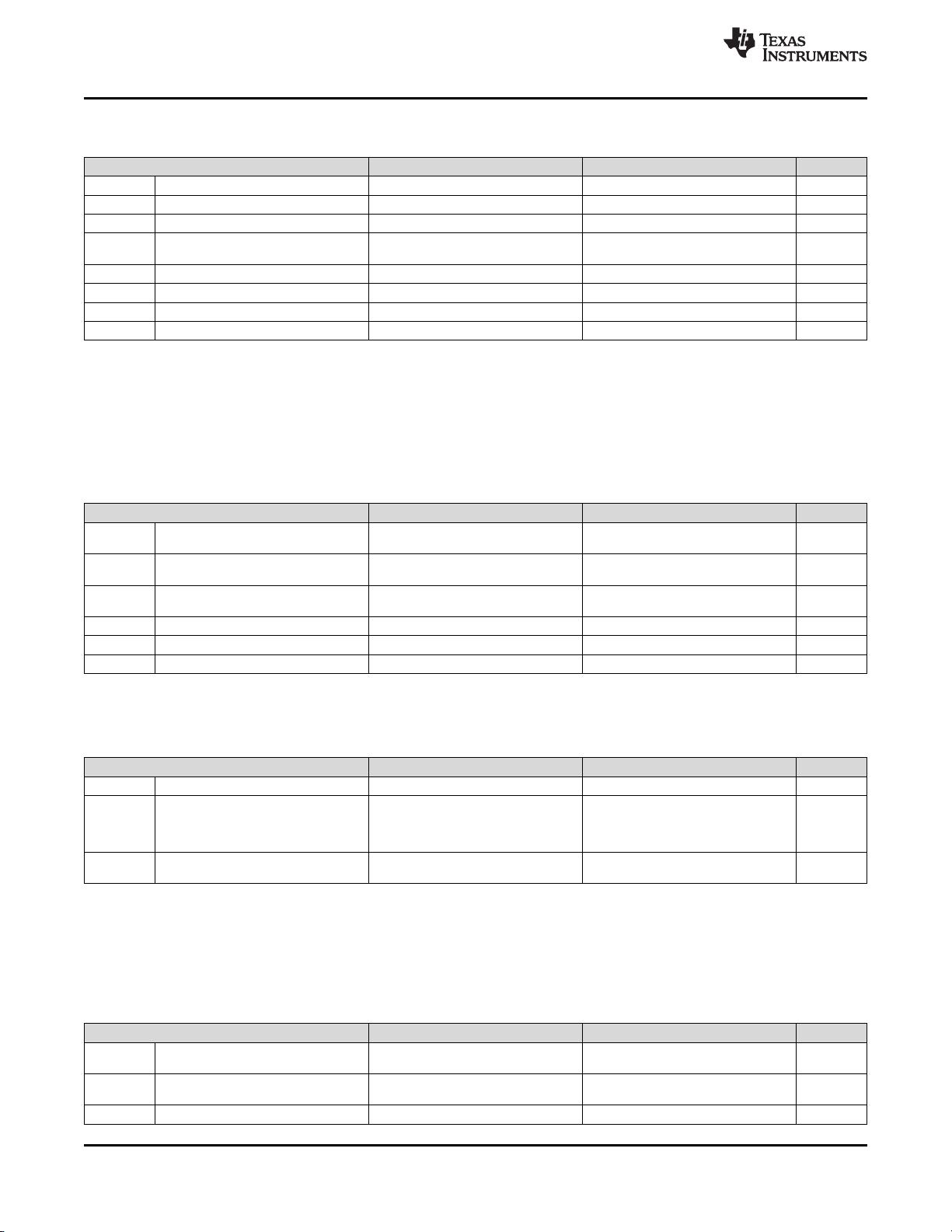

7.22 I

2

C-Compatible Serial Interface Characteristics

VDD_VCO, VDDO_12, VDDO_34, VDD_REF = 1.8 V ± 5%, 2.5 V ± 5%, 3.3 V ± 5% and T

A

= -40°C to 105°C

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

V

IH

Input Voltage, Logic High

0.7 ×

VDD_REF

V

V

IL

Input Voltage, Logic Low

0.3 ×

VDD_REF

V

I

IH

Input Leakage Current VDD_REF ± 10% -5 5 µA