TSMC 0.09um工艺揭秘:Nexsys 90纳米技术与mixed-signal/RF设计布局

需积分: 10 49 浏览量

更新于2024-07-26

收藏 22.82MB PDF 举报

本资源是一份关于CMOS工艺流程和TSMC不同节点技术布局的详细指导文档,由作者Hong-Yi Huang(黃弘一)提供。主要内容分为六个章节:

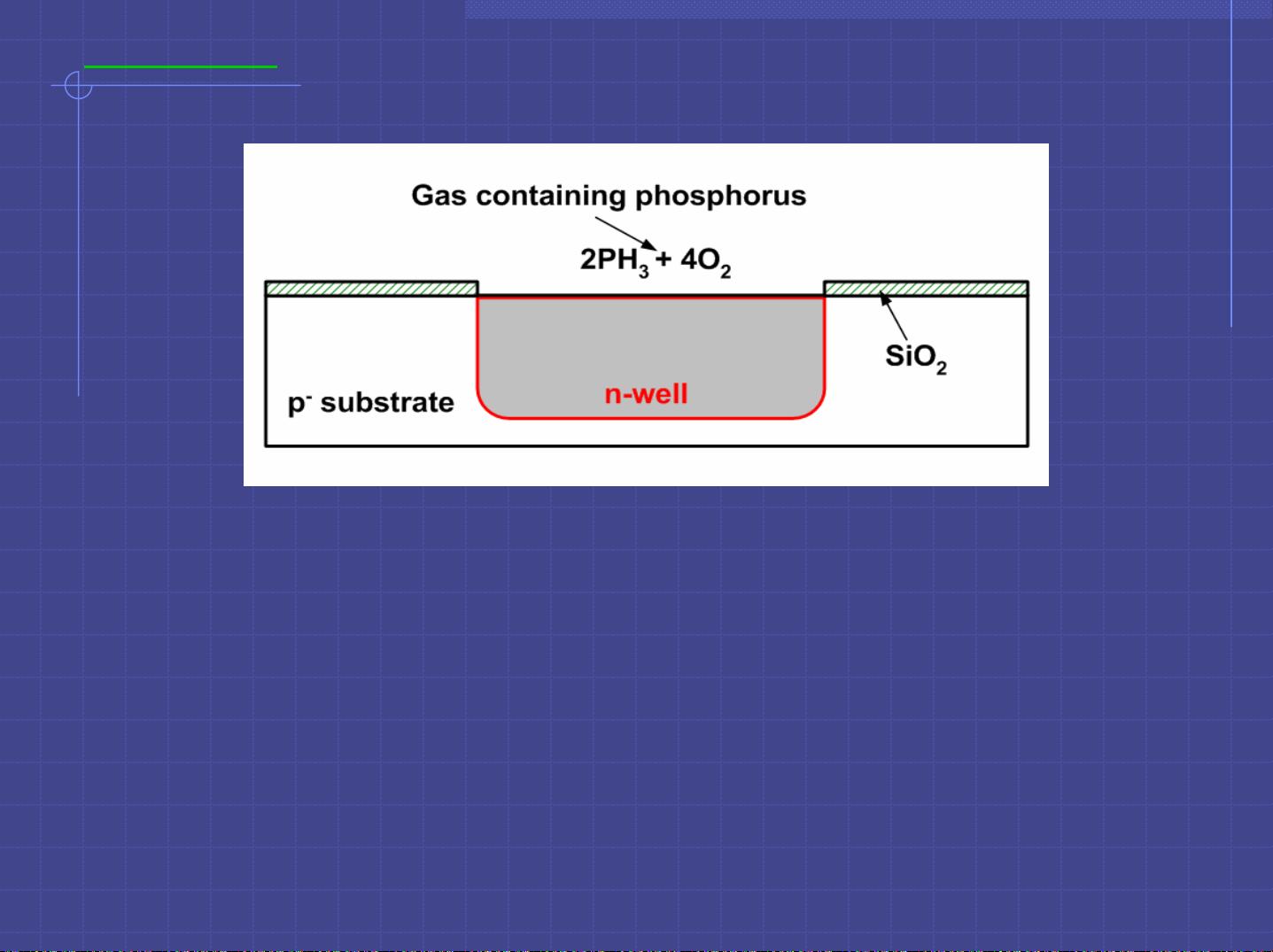

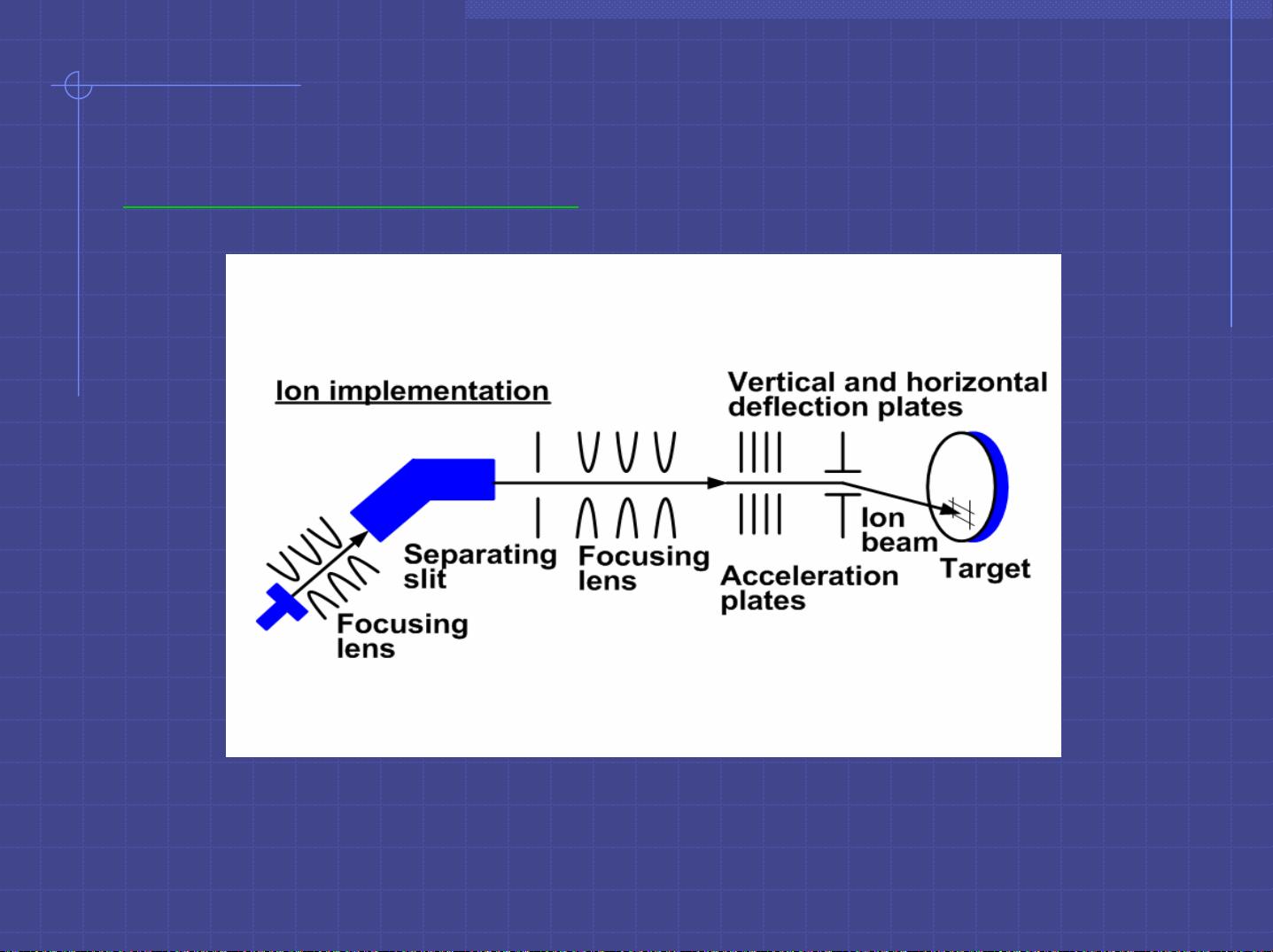

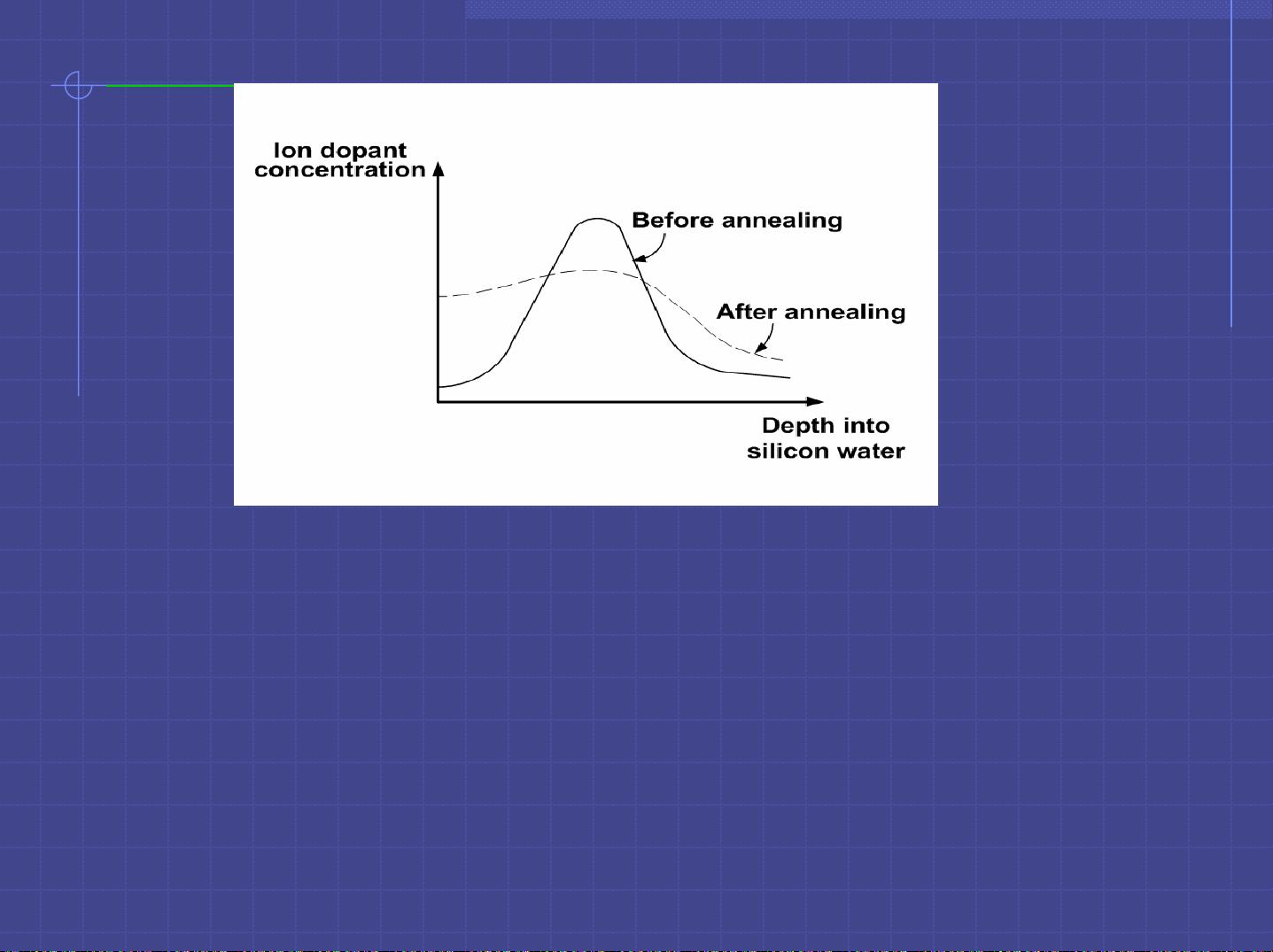

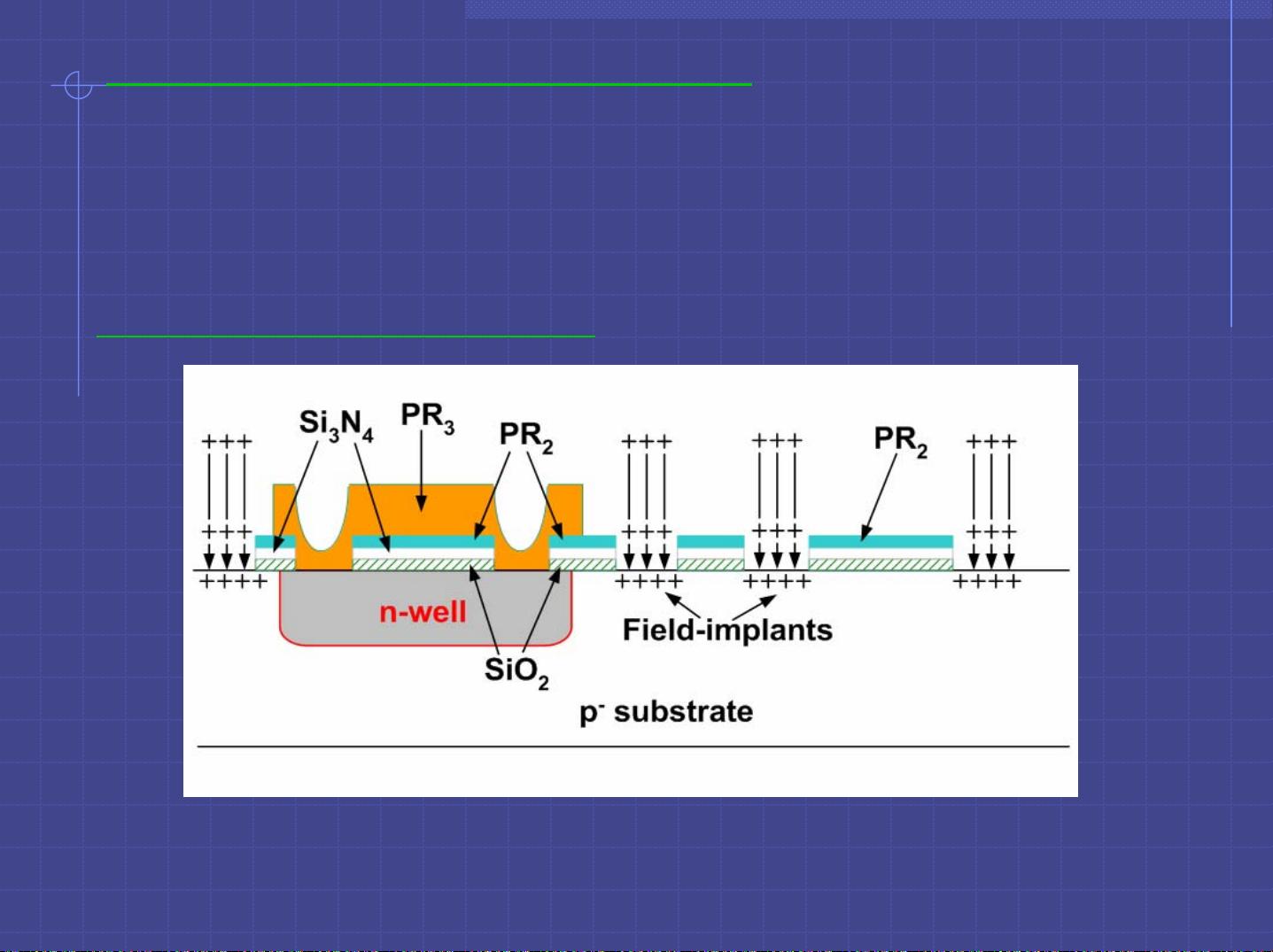

1. **CMOS Processing Flow**: 该章节介绍了从0.25um到0.09um的各种工艺节点,包括-0.25um 1P5M、-0.18um 1P6M、-0.15um 1P7M、-0.13um 1P8M等,这些都是CMOS工艺的代表性节点,强调了随着技术的进步,性能和集成度的提升。这些节点适用于多种应用,如高性能、低功耗、混合信号/RF以及嵌入式内存。

2. **TSMC 0.25um 1P5M**: 详细讲述了TSMC的0.25微米工艺,这是早期的1P5M技术,对于当时的技术水平具有里程碑意义。

3. **TSMC 0.18um 1P6M**: 接下来的章节深入到0.18微米工艺,这标志着更先进的技术,提供了更高的性能和更低的功耗。

4. **TSMC 0.15um 1P7M**: 随着技术进一步细化,0.15um 1P7M工艺在芯片密度和效率上有了显著提升。

5. **TSMC 0.13um 1P8M**: 进入到了0.13微米节点,这是一个重要的里程碑,通常用于制作更复杂、功能更强大的集成电路。

6. **0.09um Node and Nexsys 90-nm Technology**: 最后,文档提到TSMC在2002年推出了0.09微米技术,并且通过Nexsys品牌展示了其90纳米技术,这是TSMC首次采用该品牌。这一技术平台旨在满足广泛应用的需求,包括高性能、低功耗和混合信号/射频设计,还特别提到了其独特的三氧化物选项,允许在同一芯片上实现三种不同的氧化层厚度,提高了设计灵活性和集成度。

这份文档对电子工程师、半导体制造商以及从事集成电路设计的专业人士来说,具有极高的参考价值,因为它涵盖了从传统到前沿的工艺技术变迁,以及如何适应不断变化的市场和技术需求。

2019-04-04 上传

2021-06-18 上传

144 浏览量

2023-11-30 上传

2023-05-10 上传

2023-06-22 上传

2023-07-28 上传

2023-12-02 上传

2024-10-15 上传

小马哥过河

- 粉丝: 3

- 资源: 11

最新资源

- 新型智能电加热器:触摸感应与自动温控技术

- 社区物流信息管理系统的毕业设计实现

- VB门诊管理系统设计与实现(附论文与源代码)

- 剪叉式高空作业平台稳定性研究与创新设计

- DAMA CDGA考试必备:真题模拟及章节重点解析

- TaskExplorer:全新升级的系统监控与任务管理工具

- 新型碎纸机进纸间隙调整技术解析

- 有腿移动机器人动作教学与技术存储介质的研究

- 基于遗传算法优化的RBF神经网络分析工具

- Visual Basic入门教程完整版PDF下载

- 海洋岸滩保洁与垃圾清运服务招标文件公示

- 触摸屏测量仪器与粘度测定方法

- PSO多目标优化问题求解代码详解

- 有机硅组合物及差异剥离纸或膜技术分析

- Win10快速关机技巧:去除关机阻止功能

- 创新打印机设计:速释打印头与压纸辊安装拆卸便捷性