Verilog编程:组合逻辑与时序逻辑解析

需积分: 35 153 浏览量

更新于2024-07-21

收藏 440KB DOC 举报

"本文详细介绍了Verilog编程中组合逻辑和时序逻辑的概念、区别以及应用,适合初学者理解和学习。"

在数字电路设计中,Verilog HDL是常用的硬件描述语言,用于描述和实现两种主要类型的逻辑电路:组合逻辑和时序逻辑。组合逻辑电路和时序逻辑电路有着显著的差异,理解这些差异对于高效地使用Verilog进行设计至关重要。

8.1.1 组合逻辑设计

组合逻辑是数字系统的基础部分,它的特点是输出信号完全取决于当前时刻的输入信号,与之前的输入状态无关。由于没有存储元件或反馈,组合逻辑电路不关心信号变化的时间顺序,仅关注输入信号的电平。设计组合逻辑电路时,通常先根据给定的功能描述,推导出输入和输出之间的逻辑关系,形成真值表,然后利用布尔代数简化逻辑表达式,构建出最简洁的电路。在Verilog HDL中,组合逻辑可以通过两种主要方式描述:

1. 使用`always`模块,其敏感列表包含电平敏感信号。在这种方法中,`always`模块的触发事件是输入信号的变化,但注意要确保敏感列表完整,避免遗漏任何输入。在模块内部,可以使用条件语句(如`if`、`case`)进行逻辑操作。通常推荐使用阻塞赋值(`=`, non-blocking assignment)来保证逻辑正确性。

```verilog

module comparator_2bit(input wire [1:0] a, b, output wire less_than);

always @(*) begin // 电平敏感列表

if (a < b) less_than = 1'b1;

else less_than = 1'b0;

end

endmodule

```

这个例子展示了如何使用Verilog HDL实现一个2输入的比较器,判断输入`a`是否小于`b`。

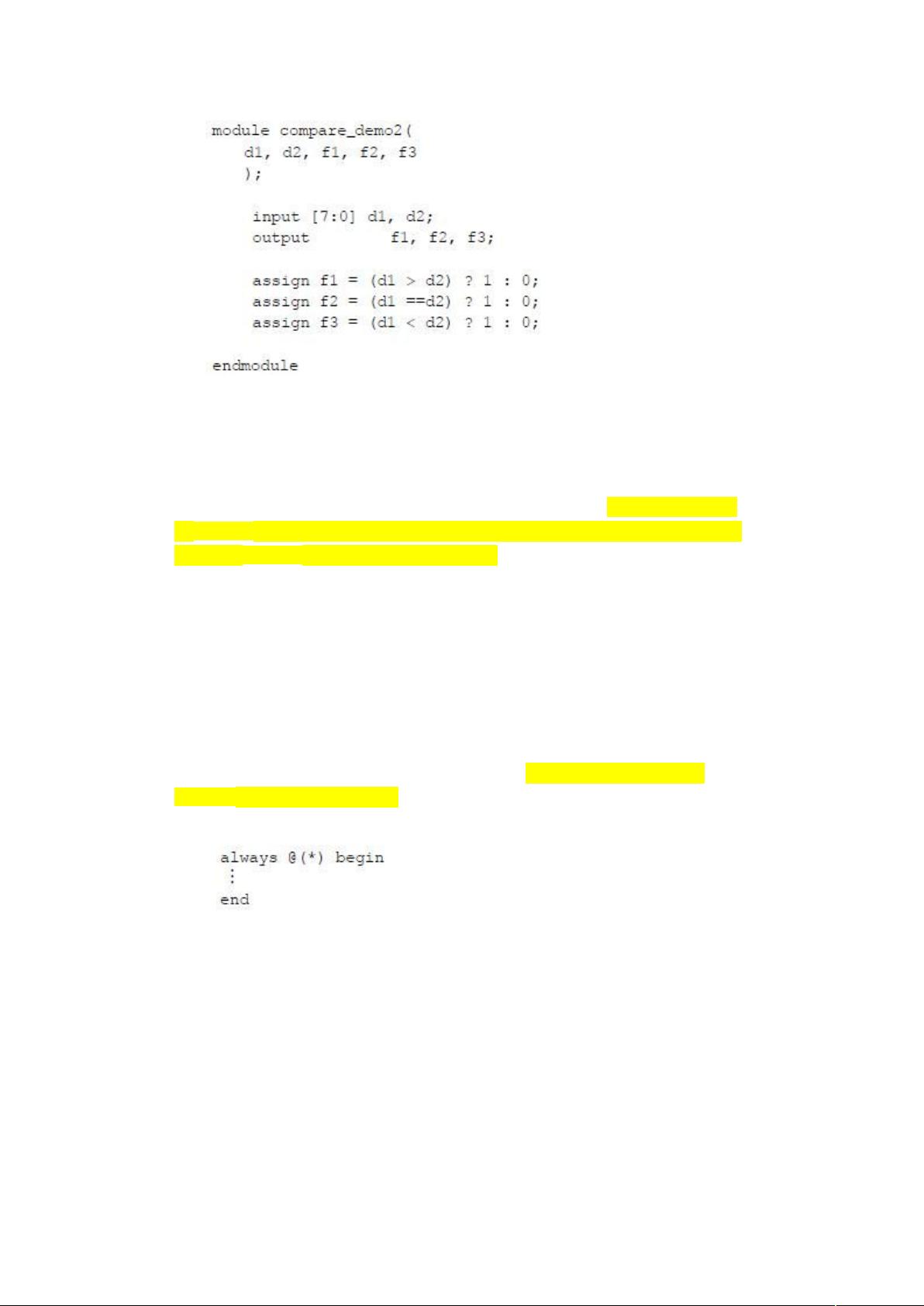

另一方面,组合逻辑也可以用`assign`关键字描述,它适用于数据流赋值,适合表示简单的逻辑关系,例如:

```verilog

module simple_and_gate(input wire a, b, output wire out);

assign out = a & b; // 数据流赋值,即非阻塞赋值

endmodule

```

这种描述方式更直观,适用于不涉及复杂控制逻辑的情况。

8.1.2 时序逻辑设计

与组合逻辑不同,时序逻辑电路含有存储元件(如寄存器、触发器等),其输出不仅取决于当前输入,还依赖于电路的前一状态。时序逻辑电路包括计数器、移位寄存器、存储器等,它们能够处理时间序列数据并维持状态。在Verilog中,时序逻辑通常用`always`模块配合边沿触发(如`@posedge clk`)来描述,因为这类电路的更新发生在特定时钟边沿。

时序逻辑设计的关键在于明确状态机模型、时钟、复位和置位信号,以及状态转换规则。一个简单的时序逻辑电路例子是D触发器:

```verilog

module dff(input wire clk, d, output reg q);

always @(posedge clk) begin // 边沿触发

q <= d; // 非阻塞赋值,确保同步更新

end

endmodule

```

这个D触发器在时钟上升沿将数据`d`的值加载到输出`q`上。

总结来说,Verilog HDL为设计者提供了强大的工具来描述和实现组合逻辑和时序逻辑电路。组合逻辑专注于当前输入的即时响应,而时序逻辑则引入了时间维度,能够记忆和处理过去的输入状态。理解这两种逻辑类型的基本原理和Verilog描述方式,对于数字电路设计是至关重要的。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2010-05-04 上传

点击了解资源详情

2024-10-31 上传

2024-10-31 上传

2021-03-03 上传

2022-09-14 上传

hujiaobeiji

- 粉丝: 0

- 资源: 3

最新资源

- JavaScript实现的高效pomodoro时钟教程

- CMake 3.25.3版本发布:程序员必备构建工具

- 直流无刷电机控制技术项目源码集合

- Ak Kamal电子安全客户端加载器-CRX插件介绍

- 揭露流氓软件:月息背后的秘密

- 京东自动抢购茅台脚本指南:如何设置eid与fp参数

- 动态格式化Matlab轴刻度标签 - ticklabelformat实用教程

- DSTUHack2021后端接口与Go语言实现解析

- CMake 3.25.2版本Linux软件包发布

- Node.js网络数据抓取技术深入解析

- QRSorteios-crx扩展:优化税务文件扫描流程

- 掌握JavaScript中的算法技巧

- Rails+React打造MF员工租房解决方案

- Utsanjan:自学成才的UI/UX设计师与技术博客作者

- CMake 3.25.2版本发布,支持Windows x86_64架构

- AR_RENTAL平台:HTML技术在增强现实领域的应用