FPGA实验:基于状态机的序列信号'1101'检测

需积分: 11 157 浏览量

更新于2024-08-07

收藏 471KB PDF 举报

"实验五 状态机实验-序列信号检测.pdf"

在本次实验中,我们将深入理解和应用状态机的概念,特别是Moore状态机和Mealy状态机,以实现一个能够检测特定序列“1101”的电路。这个实验旨在增强对状态机设计方法的掌握,并通过实践来熟悉FPGA开发环境。

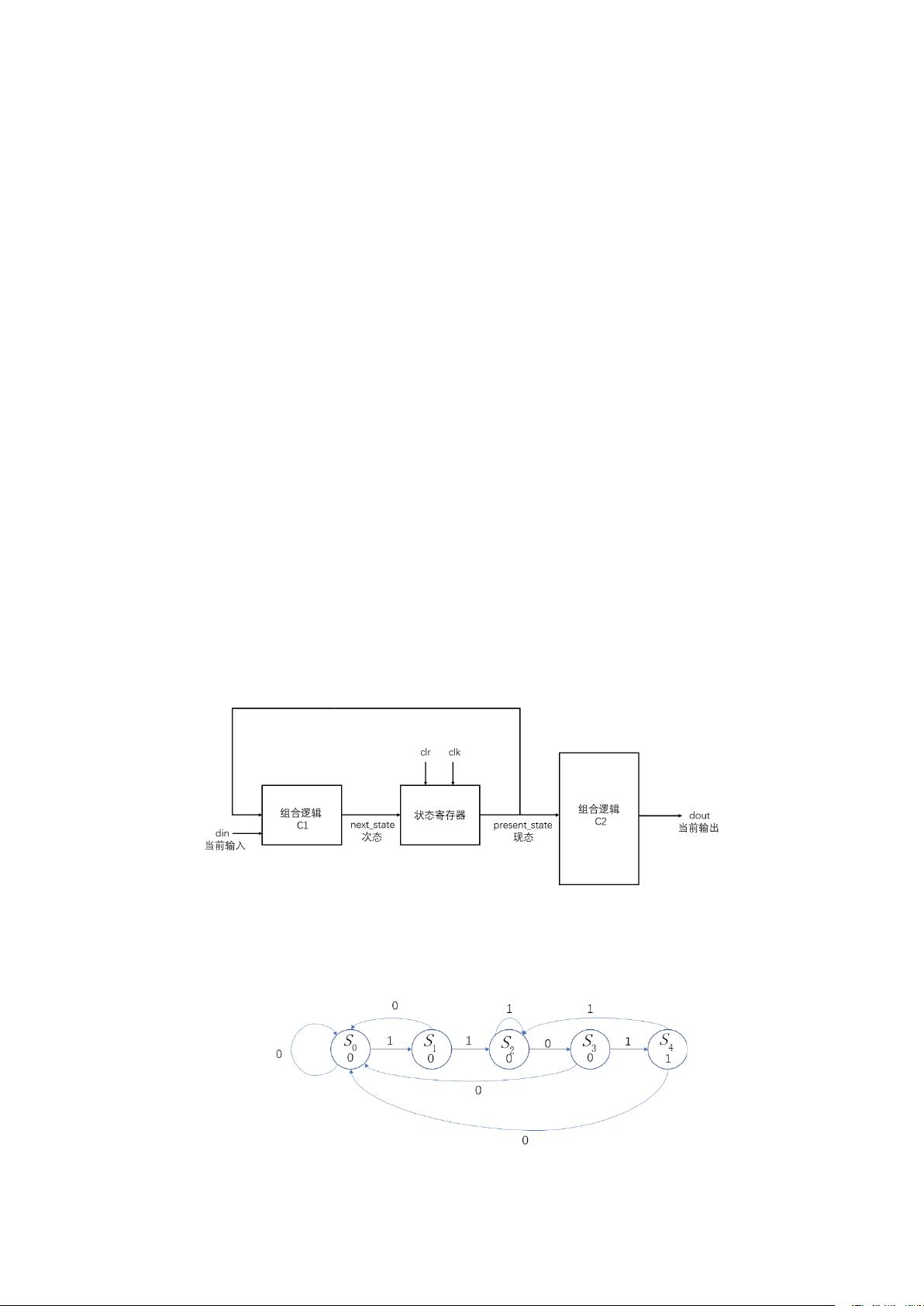

Moore状态机是一种常见类型的状态机,其输出仅仅取决于当前状态,而不受当前输入的影响。这种特性使得Moore状态机在设计时,输出行为与输入信号的时序无关。图5-1展示了Moore状态机的基本结构,它由一系列状态和状态之间的转移构成。在Moore状态机的设计中,我们关注的是如何根据输入序列来改变状态,以及如何根据当前状态产生相应的输出。

以序列检测器为例,当检测到输入序列“1101”时,输出信号dout应置为1,其他情况输出为0。图5-2描绘了Moore状态机检测“1101”序列的状态转换图。这里,状态S0作为初始状态,若在S4状态下接收到输入1,将回到S2;若输入为0,则回到S0,重新开始检测。

Verilog是一种硬件描述语言,常用于FPGA设计。在给定的Verilog程序中,我们定义了5个状态(S0到S4)以及一个状态寄存器present_state和next_state来存储当前状态和下一次要转换到的状态。程序中的两个always块分别处理状态寄存器的更新(同步于时钟上升沿或清除信号clr)和状态转移逻辑。在状态转移模块中,根据present_state的值和输入din,计算出next_state的值。

实验需要用到的设备包括美国Digilent公司的Basys3 FPGA开发板、装有Vivado 2017.4的计算机以及USB连接线。Vivado是一款强大的集成开发环境,可用于设计、仿真、综合和编程FPGA项目。

通过本实验,学生不仅能够理解状态机的基本原理,还能实际操作FPGA硬件,将理论知识转化为实际工程应用。此外,实验过程中的设计、仿真和验证环节也能锻炼学生的逻辑思维能力和问题解决能力。

总结起来,这个实验涵盖了以下关键知识点:

1. Moore状态机和Mealy状态机的区别和应用。

2. Verilog语言在状态机设计中的应用。

3. FPGA开发环境的使用,包括Vivado软件和Basys3开发板。

4. 序列检测器的实现,特别是在状态转换图上的逻辑设计。

5. 数字电路中的状态寄存器和组合逻辑模块的设计。

通过这个实验,学生将能够深入理解状态机在数字系统设计中的重要性,并具备独立设计和实现状态机的能力。

414 浏览量

3961 浏览量

533 浏览量

2023-07-16 上传

2023-06-09 上传

2024-09-12 上传

262 浏览量

114 浏览量

192 浏览量

qq_58960835

- 粉丝: 0

- 资源: 4

最新资源

- 20210805-西南证券-思瑞浦-688536-业绩持续增长,电源管理芯片表现亮眼.rar

- nodejs-restapi:使用Node.js和MongoDB Atlas设计REST API

- 易语言动画播放器

- spring-cloud-api-gateway

- 福州大学汇编语言程序设计实践作业(堆排序八皇后等).zip

- 作品答辩极简建筑系风格大学生设计答辩模板.rar

- MyBaD - MySQLish MP3 frontend-开源

- backbone.helpers:一组用于扩展 Backbone.js 的辅助类

- 易语言JnToo播放器源码 易语言MP3播放器

- Encode Utility.-crx插件

- antd-pro-hapijs-user:基于antd pro + hapi-api的带权限用户管理

- SHC-公共商店

- My-Portfolio:这是我的个人网站的仓库。这反映了我是谁!

- 20210805-中信期货-饲料养殖专题报告:生猪调研,疫情干扰出栏节奏,现货价格阶段存反弹预期.rar

- kmihiel.github.io

- ASP+ACCESS新闻发布系统(源代码+LW).zip