FPGA驱动的线阵CCD时序与模拟信号优化设计

6 浏览量

更新于2024-08-28

收藏 366KB PDF 举报

本文档探讨了基于FPGA的线阵CCD驱动时序及模拟信号处理的设计,着重介绍了电荷耦合器CCD(Charge-Coupled Device, CCD)的优势及其在图像传感和非接触测量领域的广泛应用。CCD的光电特性,如转换效率和信噪比,对于确保其性能和稳定性至关重要,这就突出了驱动时序设计的重要性。通用CCD驱动设计有四种方法:EPROM驱动、IC驱动、单片机驱动和PLD驱动,其中FPGA驱动因其灵活性和可重构性成为一种理想选择。

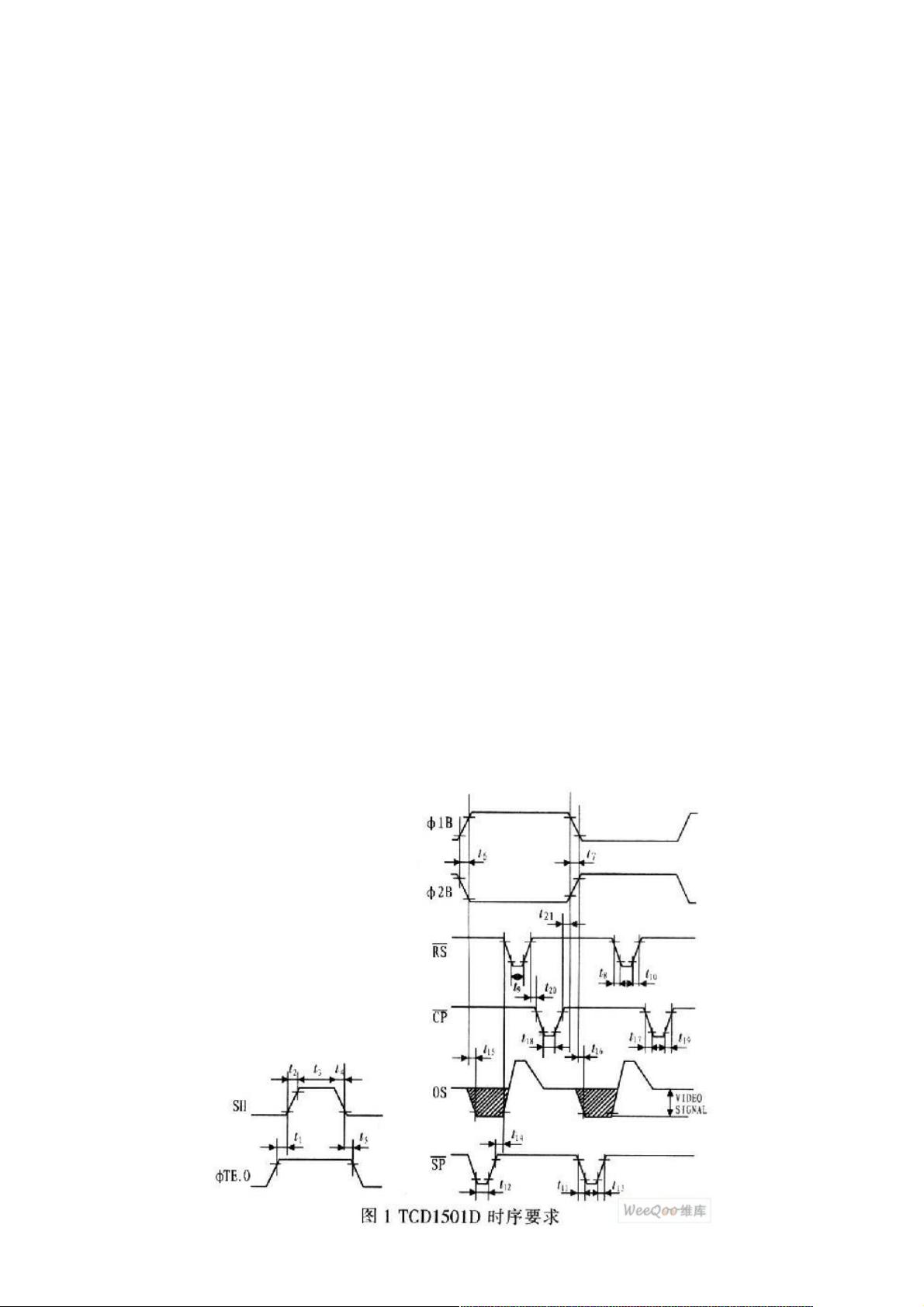

FPGA(Field-Programmable Gate Array)驱动电路的主要优点在于高度集成、高速度和高可靠性。通过FPGA,设计师可以轻松地调整驱动时序,添加或修改功能,只需通过重新编程即可,无需物理改动硬件。以TCD1501D这款日本东芝公司生产的高灵敏度线阵CCD为例,其工作参数包括5000个像元、7μm×7μm×7μm的尺寸、300~1000nm的光谱响应范围和12MHz的驱动时钟频率。驱动脉冲包括复位时钟RS、移位脉冲φ1和φ2以及转移脉冲SH,为了完整传输一帧图像,需要至少2538个φ1或φ2时钟脉冲。

文章详细解析了驱动电路的工作原理和设计要点,强调了在FPGA平台上的时序控制对于优化CCD性能和实现灵活定制的重要性。这种设计方法不仅提升了驱动电路的性能,还降低了成本和维护复杂性,是现代CCD系统设计中的重要技术手段。

493 浏览量

181 浏览量

1138 浏览量

243 浏览量

点击了解资源详情

218 浏览量

2021-04-24 上传

314 浏览量

2021-02-03 上传

weixin_38722184

- 粉丝: 5

最新资源

- C#实现程序A的监控启动机制

- Delphi与C#交互加密解密技术实现与源码分析

- 高效财务发票管理软件

- VC6.0编程实现删除磁盘空白文件夹工具

- w5x00-master.zip压缩包解析:W5200/W5500系列Linux驱动程序

- 数字通信经典教材第五版及其答案分享

- Extjs多表头设计与实现技巧

- VBA压缩包子技术未来展望

- 精选多类型导航菜单,总有您钟爱的一款

- 局域网聊天新途径:Android平台UDP技术实现

- 深入浅出神经网络模式识别与实践教程

- Junit测试实例分享:纯Java与SSH框架案例

- jquery xslider插件实现图片的流畅自动及按钮控制滚动

- MVC架构下的图书馆管理系统开发指南

- 里昂理工学院RecruteSup项目:第5年实践与Java技术整合

- iOS 13.2真机调试包使用指南及安装