"Verilog HDL基本语法入门与发展历程:数字电子技术基础第9章详解"

版权申诉

25 浏览量

更新于2024-03-28

收藏 830KB PPT 举报

数字电子技术基础的第9章主要介绍了Verilog HDL的基本语法。Verilog HDL是一种硬件描述语言,最早由GDA公司的Phil Moorby于1983年首创。后来,Cadence公司收购了GDA公司,使Verilog HDL成为Cadence公司的私有财产。然而,1990年,Cadence决定公开Verilog HDL语言,并成立了OVI组织来负责其发展。由于Verilog HDL的优越性,IEEE于1995年制定了Verilog HDL的IEEE标准,即Verilog HDL1364-1995。

Verilog HDL的抽象级别包括系统级和算法级。系统级是用高级语言结构实现设计模块的外部性能模型,而算法级则是更加具体和详细的实现。通过Verilog HDL,工程师们可以利用这种硬件描述语言来描述数字逻辑电路和系统。Verilog HDL在数字电子技术中扮演着至关重要的角色,可以帮助工程师们更好地设计、分析和验证数字系统。

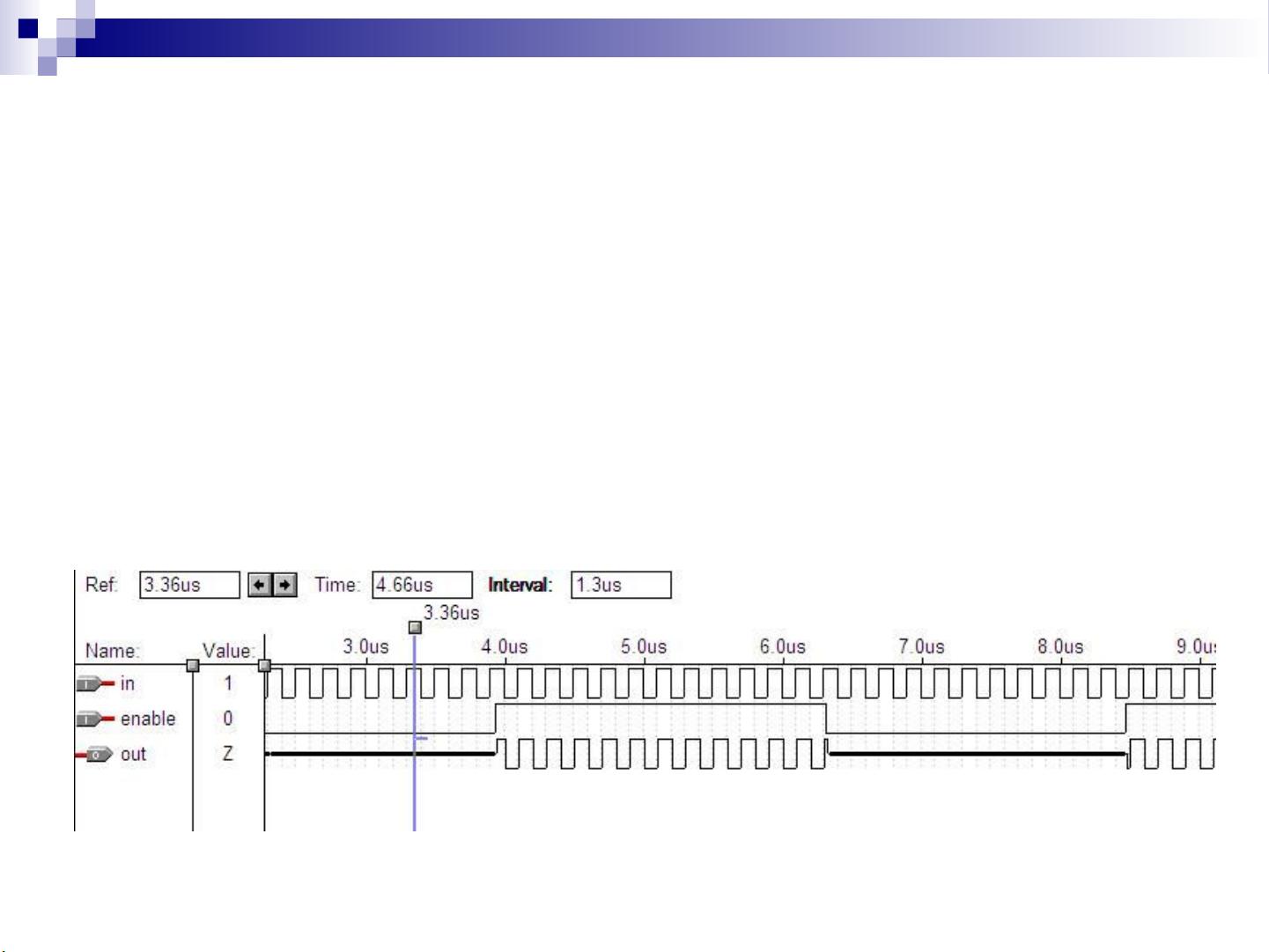

在学习Verilog HDL的基本语法时,学生们需要掌握模块、端口、数据类型、运算符、赋值语句、顺序语句、组合逻辑和时序逻辑等概念。Verilog HDL的语法严谨而灵活,可以帮助工程师们更好地实现数字系统设计。通过学习Verilog HDL,工程师们可以更好地理解数字逻辑电路的运作原理,提高设计的效率和准确性。

总之,通过数字电子技术基础第9章关于Verilog HDL基本语法的学习,学生们可以了解Verilog HDL的起源、发展历程以及其在数字系统设计中的重要性。掌握Verilog HDL的基本语法是成为一名优秀的数字电子工程师的必备技能,能够帮助工程师们更好地设计、分析和验证数字系统,提高工作效率和准确性。通过不断学习和实践,工程师们可以不断提升自己在数字系统设计领域的技术水平,为数字电子技术的发展做出更大的贡献。Verilog HDL作为一种强大的硬件描述语言,将在数字电子技术的领域中发挥越来越重要的作用,成为未来数字系统设计的重要工具。

2021-09-21 上传

2022-04-08 上传

2021-09-24 上传

2023-06-09 上传

2024-01-06 上传

2023-05-24 上传

2023-06-06 上传

2023-04-28 上传

2023-06-02 上传

wxg520cxl

- 粉丝: 25

- 资源: 3万+

最新资源

- 单片机串口通信仿真与代码实现详解

- LVGL GUI-Guider工具:设计并仿真LVGL界面

- Unity3D魔幻风格游戏UI界面与按钮图标素材详解

- MFC VC++实现串口温度数据显示源代码分析

- JEE培训项目:jee-todolist深度解析

- 74LS138译码器在单片机应用中的实现方法

- Android平台的动物象棋游戏应用开发

- C++系统测试项目:毕业设计与课程实践指南

- WZYAVPlayer:一个适用于iOS的视频播放控件

- ASP实现校园学生信息在线管理系统设计与实践

- 使用node-webkit和AngularJS打造跨平台桌面应用

- C#实现递归绘制圆形的探索

- C++语言项目开发:烟花效果动画实现

- 高效子网掩码计算器:网络工具中的必备应用

- 用Django构建个人博客网站的学习之旅

- SpringBoot微服务搭建与Spring Cloud实践