LVDS接口在远程数据传输中的并行转串行设计

DOC格式 | 1.42MB |

更新于2024-06-24

| 46 浏览量 | 举报

"远程数据传输中并行转串行LVDS接口设计说明书本科毕设论文"

本文档详细阐述了在远程数据传输中采用并行转串行LVDS接口的设计方案,旨在解决高速数据传输的需求。LVDS(Low Voltage Differential Signaling)是一种低电压差分信号技术,因其低功耗、高速传输特性而被广泛应用于通信领域,特别是在基站、大型交换机等设备中。

1.1 课题研究背景和意义

随着数字信号处理技术的进步,对高速数据的处理和传输能力提出了更高要求。传统的并行I/O接口由于电路结构和传输线的局限,无法满足高速微处理器和其他高带宽应用的需求。因此,LVDS接口技术因其独特的优势,成为了解决高速数据传输瓶颈问题的重要选择。

1.2 国内外研究现状

LVDS技术在国内外的研究和应用都取得了显著进展,尤其在通信系统中,其应用范围不断扩展。3G技术的快速发展进一步推动了LVDS接口在高速数据传输中的应用。

1.3 LVDS简介

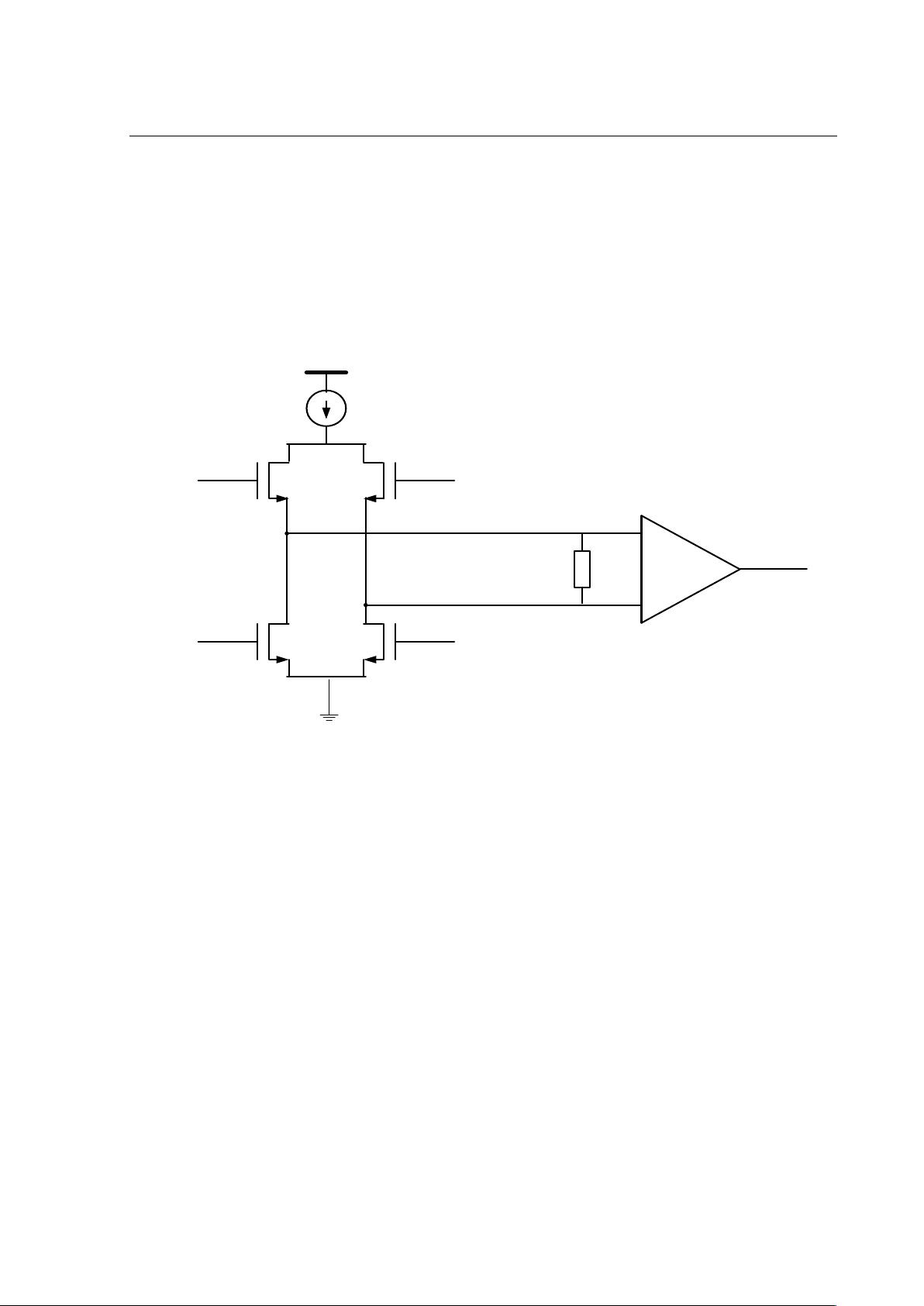

LVDS是一种使用小幅度差分信号进行数据传输的技术,它通过两个反相信号线进行数据传输,降低了噪声影响,提高了信号质量,并且能实现低功耗运行。

1.4 FPGA简介

FPGA(Field-Programmable Gate Array)是可编程逻辑器件,具有灵活的架构,能够根据设计需求配置成不同的逻辑功能。在LVDS接口设计中,FPGA可以用于实现并行到串行转换、时钟管理和控制逻辑等功能。

1.5 本课题研究内容和安排

本课题主要研究LVDS接口的FPGA实现,包括系统整体结构设计、LVDS工作原理的理解、FPGA结构和特性的分析,以及硬件电路设计和软件程序的编写与调试。

2. 理论基础

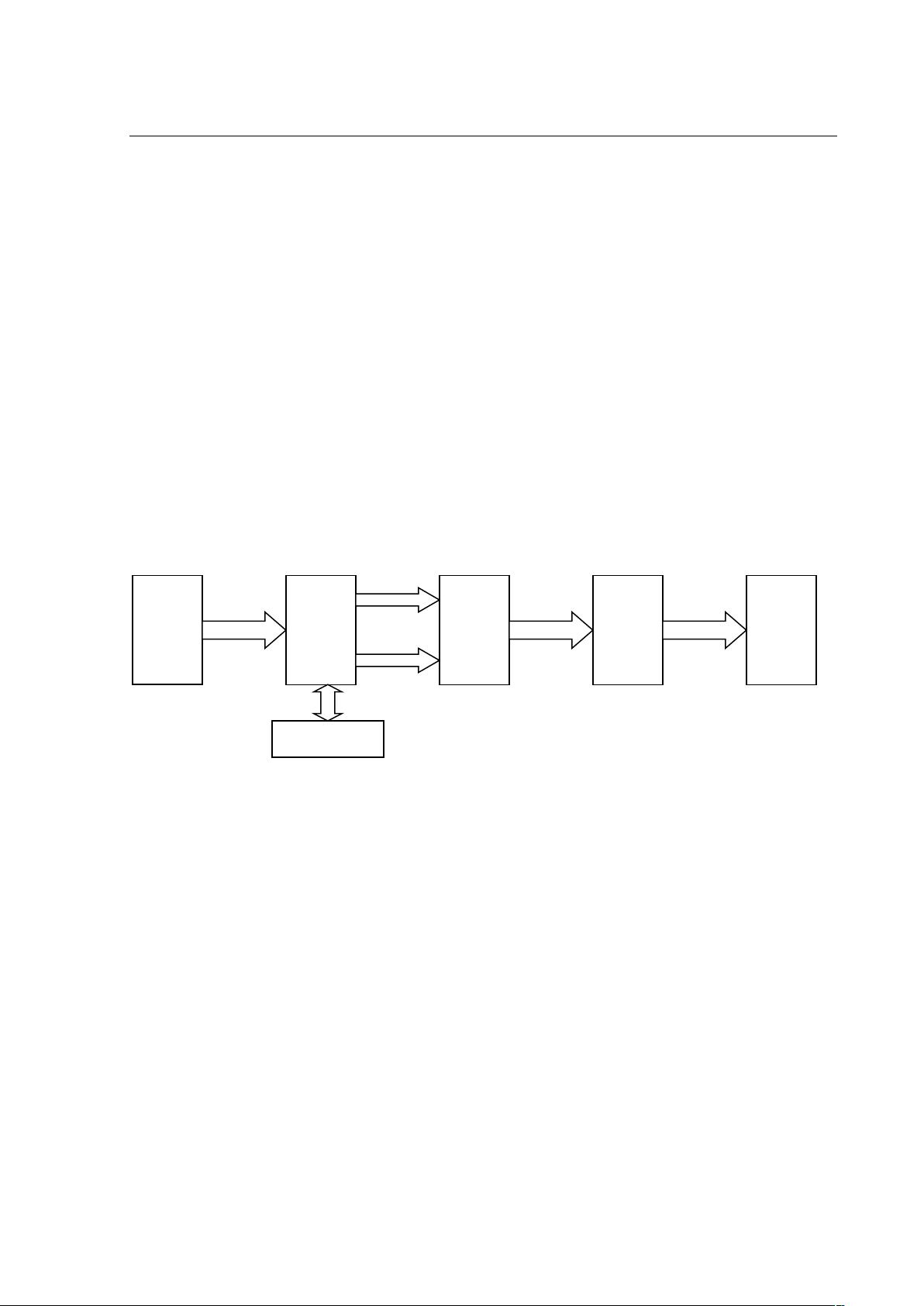

这部分详细介绍了系统的总体架构,LVDS的工作原理,FPGA的结构和特点,以及并行接口和串行接口的区别。还探讨了光耦合器在接口设计中的作用。

3. 整体硬件电路设计

硬件电路设计涵盖了从整体电路结构到各个关键模块的详细设计,如FPGA内部的控制模块、FIFO缓存、时钟管理模块、配置电路、串化器配置电路、驱动电路、存储器SDRAM电路、电源电路、程序下载电路、时钟电路、LED显示电路、开关控制电路和并行数据输入电路等。

4. 系统软件设计

软件设计部分包括系统程序的详细设计,如晶振倍频、并行转串行转换程序和分频程序的编写,以及系统的仿真和调试过程。

5. 总结与展望

论文最后总结了研究的主要成果,并对未来可能的研究方向进行了展望,如优化电路性能、提高传输速率和稳定性等方面。

附录部分提供了系统程序代码、硬件电路图和PCB板图等具体实现细节,供读者参考。

这篇本科毕业设计论文深入探讨了LVDS接口在远程数据传输中的应用,为理解和实现高速数据传输解决方案提供了宝贵的理论和实践指导。

相关推荐

xinkai1688

- 粉丝: 397

最新资源

- 掌握MATLAB中不同SVM工具箱的多类分类与函数拟合应用

- 易窗颜色抓取软件:简单绿色工具

- VS2010中使用QT连接MySQL数据库测试程序源码解析

- PQEngine:PHP图形用户界面(GUI)库的深入探索

- MeteorFriends: 管理朋友请求与好友列表的JavaScript程序包

- 第三届微步情报大会:深入解析网络安全的最新趋势

- IQ测试软件V1.3.0.0正式版发布:功能优化与错误修复

- 全面技术项目源码合集:企业级HTML5网页与实践指南

- VC++6.0绿色完整版兼容多系统安装指南

- 支付宝即时到账收款与退款接口详解

- 新型不连续导电模式V_2C控制Boost变换器分析

- 深入解析快速排序算法的C++实现

- 利用MyBatis实现Oracle映射文件自动生成

- vim-autosurround插件:智能化管理代码中的括号与引号

- Bitmap转byte[]实例教程与应用

- Qt YUV在CentOS 7下的亲测Demo教程