优化异构多核处理器的全高清H264解码系统设计与性能提升

147 浏览量

更新于2024-08-28

收藏 796KB PDF 举报

随着移动互联网的蓬勃发展,高清多媒体视频和3D游戏的日益流行,单核嵌入式硬件平台已经无法满足这些应用的复杂计算需求。异构多核处理器,特别是其在视频编解码领域的强大优势,已经成为嵌入式处理器架构发展的主流。传统的解决方案通常依赖于异构多核处理器中的数字信号处理器(DSP)进行高清视频编解码,如DaVinci平台的DSP能实现720P视频的实时解码,显著提升了速度和性能。

然而,尽管DSP在加速视频处理方面有所贡献,它在运行过程中需要对信箱(Mailbox)和直接内存访问(DMA)进行精细配置,这可能导致片上通信带宽的消耗增加,进而降低了核间通信的效率。此外,与专用硬件编解码器相比,DSP的编解码效率仍有待提高。

本文关注的焦点是基于TISocOMAP4430这种异构多核处理器的全高清H264解码系统设计。该处理器特别之处在于集成了双核Cortex-A9高性能处理器,双核Cortex-M3协处理器以及集成的IVA-HD多媒体硬编解码加速引擎。IVA-HD引擎内部包含多个针对不同编解码优化的加速引擎,每个引擎拥有独立的数据存储,减少模块间的竞争,提高资源利用率。

设计的关键技术包括:

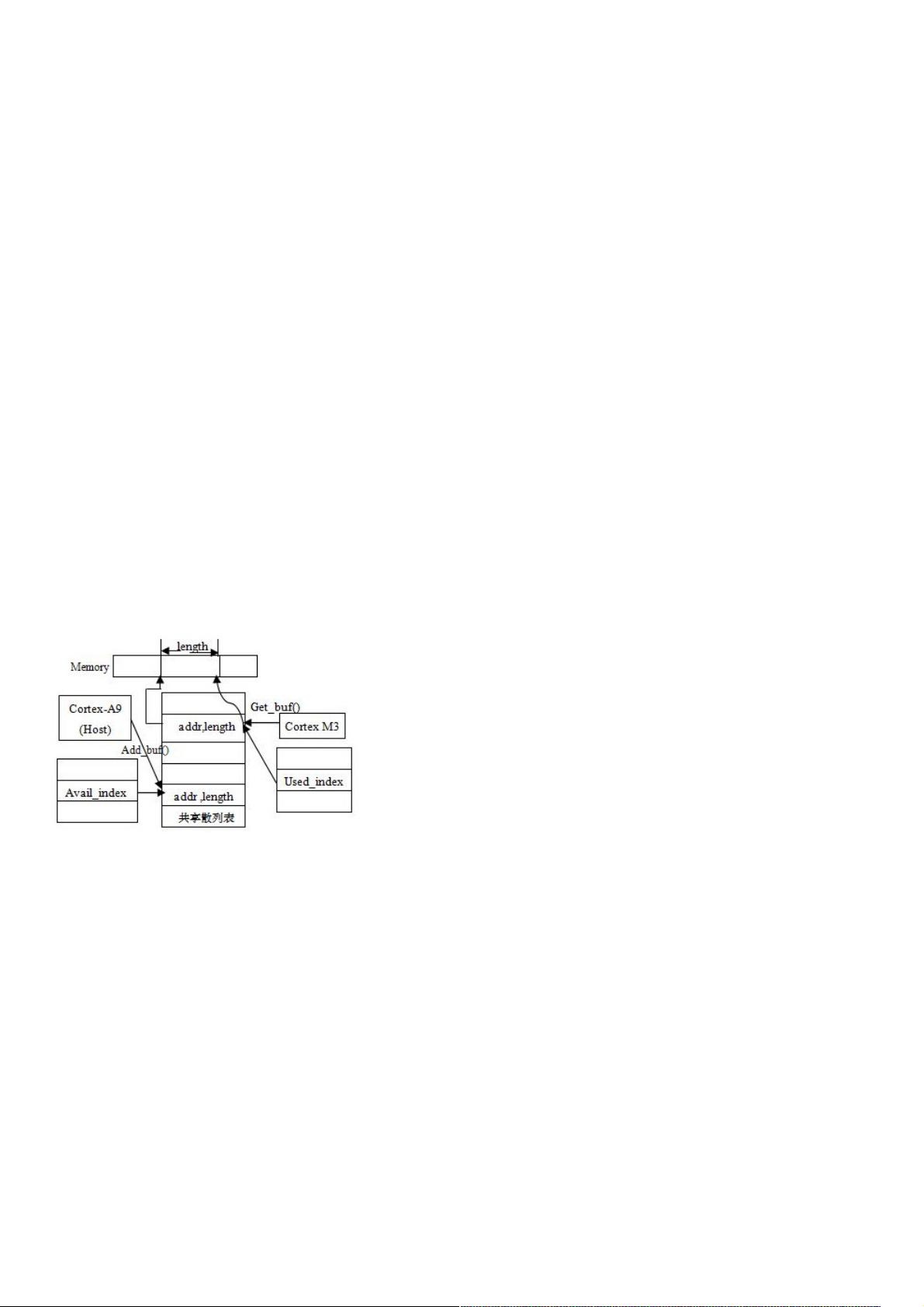

1.1 virtio缓存队列和RPMsg消息框架:这些技术被用于建立基于异步通知的主处理核心(Cortex-A9)与协处理核心(Cortex-M3)之间的高效通信。virtio缓存队列提供了一种大容量数据传输的方式,而RPMsg则支持灵活的消息传递模型,允许低延迟和异步操作,这对于实时视频解码至关重要。

1.2 内部资源管理:Cortex-A9负责系统的整体管理和复杂任务,如操作系统调度、音频解码和用户界面交互,而Cortex-M3作为辅助核心,专门负责协同IVA-HD引擎进行高效的H264解码任务。这种分工协作有助于优化资源分配和性能表现。

通过这种设计,文章旨在通过整合异构多核的优势和优化的通信机制,提升全高清H264解码的性能,确保在移动设备上提供流畅的多媒体体验。后续内容可能还会深入探讨系统架构的实现细节、性能测试结果以及优化策略,以证明该设计的有效性和实用性。

197 浏览量

115 浏览量

点击了解资源详情

115 浏览量

114 浏览量

197 浏览量

2020-07-27 上传

113 浏览量

114 浏览量

weixin_38668754

- 粉丝: 3

- 资源: 972

最新资源

- arhaica:古代Web的Milti-Domain内容发布系统

- MeetingAppointment.zip_.net mvc_C#_bootstrap .net_mvc_预约

- grao:PoC Stara Zagora GRAO个人数据泄露

- 数字图像处理知识点总结.zip

- 网钛远程桌面管理助手 v3.10

- estimo:评估浏览器执行您JavaScript代码的时间

- NLP4SocialGood_Papers:有关NLP for Social Good的最新论文的阅读清单

- 影刀RPA系列公开课5:手机操作自动化.rar

- 毕加索用于光刻的图像加载组件-Android开发

- PGAT-开源

- fruit-recognition-master.zip_QT图像识别_opencv_qt 图像处理_qt 图像识别_水果种类识

- 影刀RPA系列公开课5:手机操作自动化.rar

- 74项环流指数读取软件

- kosa:知识组织系统(KOS)的轻量级聚合器

- 最新版面试宝典最终版.zip

- Shibboleth-Multi-Context-Broker:Shibboleth多上下文代理