联想PCB EMI设计规范要点:电容处理与时钟线策略

联想的PCB EMI设计规范是一份详细的电子电路板(PCB)电磁兼容(EMI)设计指导文档,由联想电子有限公司制定,旨在确保产品在满足功能需求的同时,能够有效降低电磁干扰,提高系统稳定性。该文档适用于MBR部门,自2000年6月6日起生效。

在规范中,特别强调了IC电源管理的重要性。首先,每个集成电路(IC)的电源引脚应配备至少0.1微法(μF)的去耦电容,例如对于BGACHIP,还需要额外在BGA的四个角落添加0.1μF和0.01μF的电容,共计8个,目的是为电源提供快速响应,减少电压波动对信号传输的影响。

针对时钟线路的设计,建议优先布线并遵循严格的规则。对于频率高于66兆赫兹(MHz)的时钟线,每个过孔的最大使用数量不超过2个,平均不超过1.5个;频率低于66MHz的线缆,限制在3个过孔,平均不超过2.5个。长于12英寸的高频率(大于20MHz)时钟线,过孔数不得超过2个。此外,为保证时钟信号完整性,要求在过孔附近添加旁路电容,尤其是在第二层(地层)和第三层(电源层)之间,电容间距最大不能超过300密尔(MIL),确保信号在换层后路径连续。

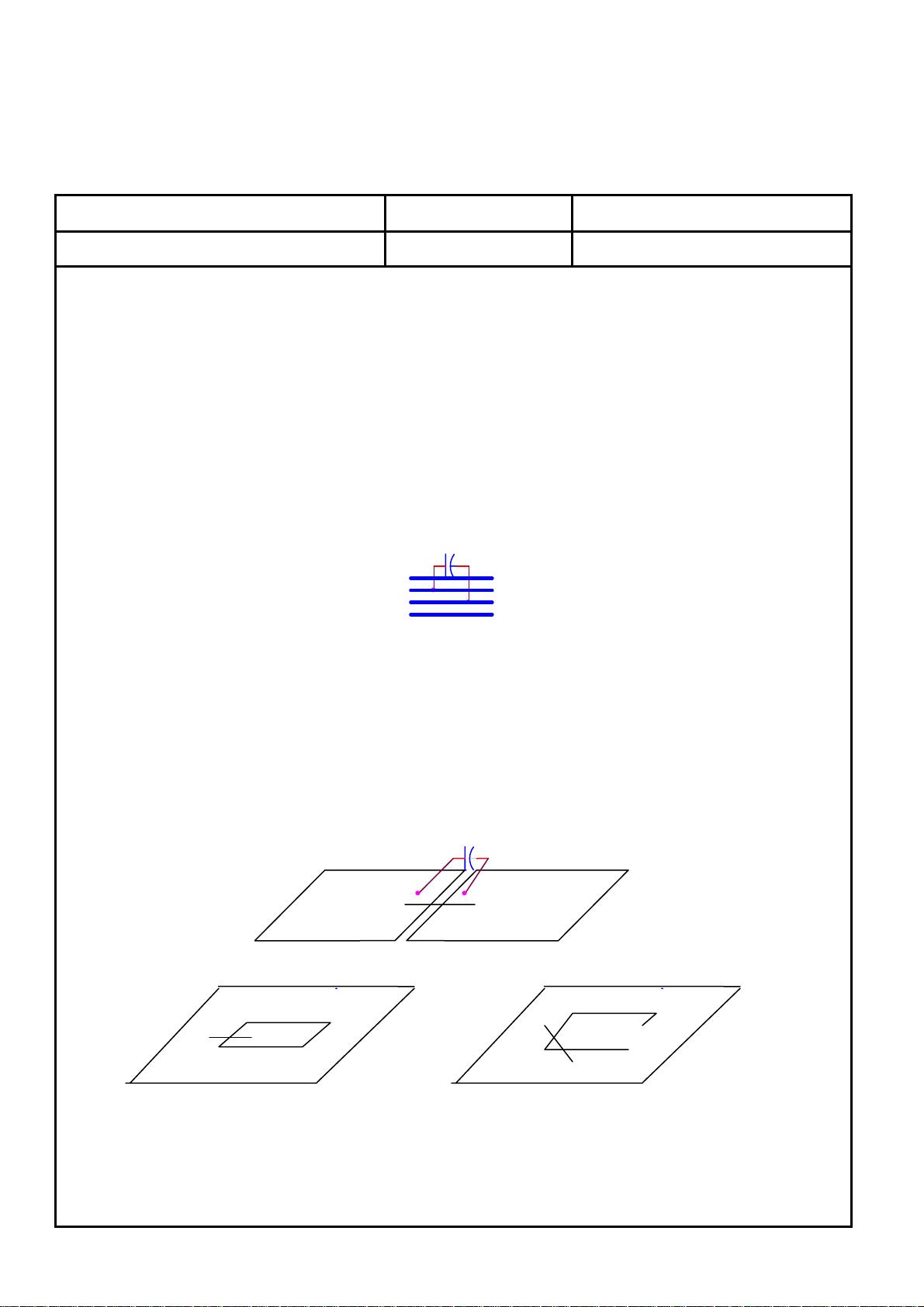

规范还特别提到避免时钟线穿岛走线,即在电源或地岛之间穿越。如果无法避免,对于频率大于等于66MHz的时钟线,应尽量不穿岛;若必须穿岛,应在穿岛处附近添加去耦电容形成镜像通路,如图6.1所示,使用0.1μF电容来减小干扰。

这份规范涵盖了电源线、时钟线等多个关键环节的EMI设计策略,对PCB工程师在实际设计过程中提供了实用的指导,帮助他们优化电路板布局,降低电磁辐射,从而提升产品质量和用户体验。

点击了解资源详情

103 浏览量

2015-02-08 上传

121 浏览量

2020-11-12 上传

2010-06-08 上传

2020-08-20 上传

156 浏览量

176 浏览量

kevin-ge

- 粉丝: 1

- 资源: 3

最新资源

- 紫黄扁平化工作总结图表大全PPT模板

- stuntz-strategies.github.io:stuntzstrategies.com

- GitRainbow-crx插件

- 煤渣:干净,响应Swift的MkDocs主题

- 基于modbus协议的大屏数据监控,使用modbus slave模拟数据,串口服务器获取温湿度.zip

- office2007驱动AccessDatabaseEngine.zip

- sample-quarkus-speaker:这是一个如何使用JAX-RS RESOURCES,Hibernate Panache以及如何准备在Openshift中使用S2I的项目的示例。

- Free fire generator-crx插件

- farmaciaJS:法玛西亚

- AngularJs-and-grunt-with-java-spring

- 数据结构课后答案

- sqlite-utils:用于操纵SQLite数据库的Python CLI实用程序和库

- SpringBoot-atguigu-resource:Bilibili SpringBoot_2019权威教程CRUD实验静态资源文件

- 蓝色复古花卉文艺范图表下载PPT模板

- duplichecker for chrome-crx插件

- binwalk-master.zip