FPGA实现SDRAM控制器:数据读写与LED验证

需积分: 16 146 浏览量

更新于2024-07-17

1

收藏 1.26MB PDF 举报

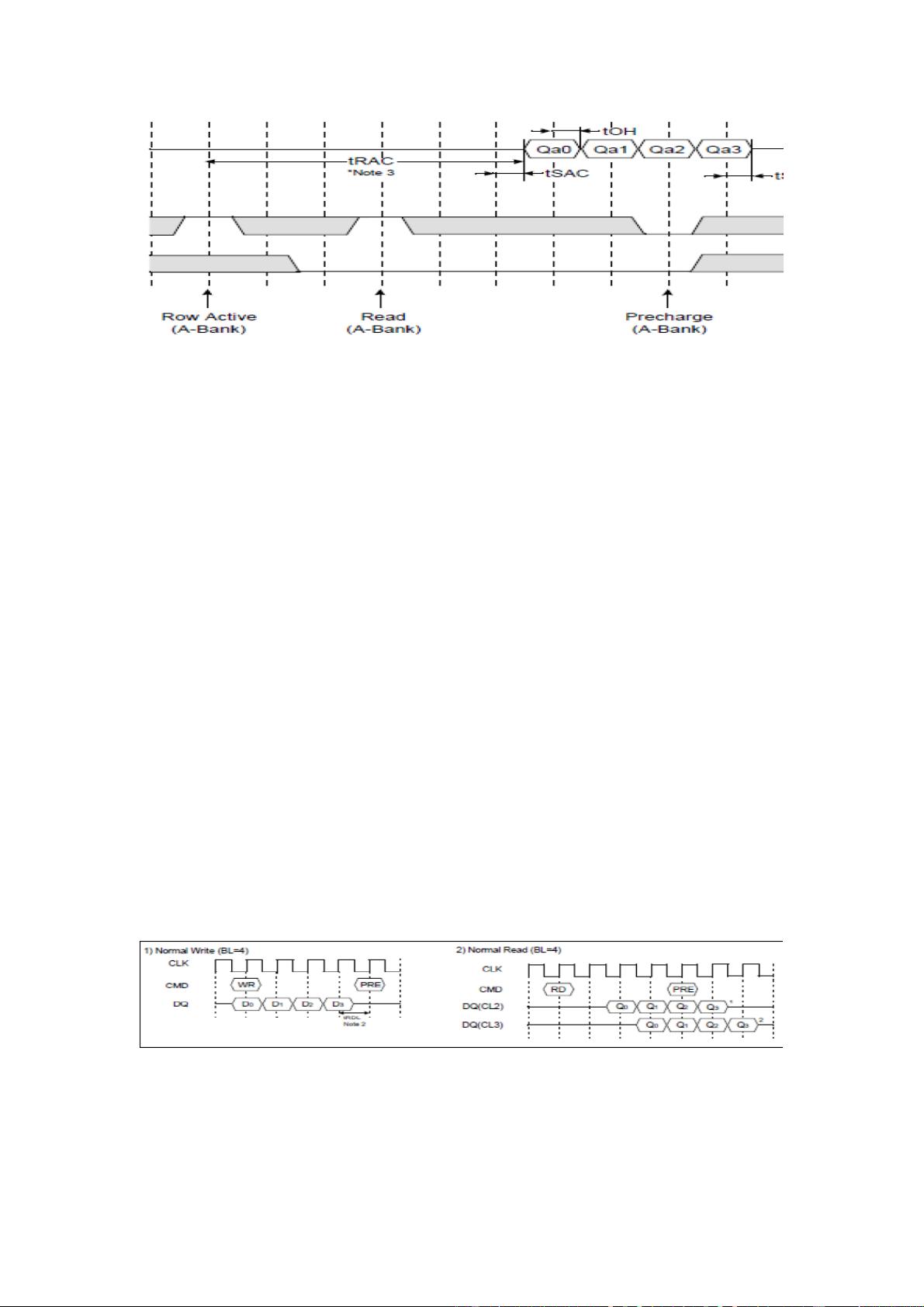

"基于FPGA的SDRAM控制器设计旨在教授如何使用FPGA实现SDRAM控制器,以便进行数据的写入和读出操作。实验通过在SDRAM中写入固定数据,然后读取并比较,若读取数据与写入数据一致则点亮LED灯。实验涉及的关键元件包括SDRAM,它是一种高速、大容量且成本效益高的存储器。控制器设计需理解SDRAM的各个端口及其功能,例如CLK时钟、CKE时钟使能、CS_n片选等。此外,还需掌握SDRAM的指令集,如自动刷新操作和突发操作,这些是确保SDRAM正常工作的重要环节。自动刷新用于保持数据完整性,而突发操作则提高了连续数据传输的效率。"

在这个实验中,学生将学习如何利用FPGA(Field-Programmable Gate Array)构建SDRAM控制器,这是一个关键的硬件设计任务。FPGA允许设计者自定义逻辑电路,使其能根据特定需求定制SDRAM控制器。SDRAM控制器是连接FPGA和SDRAM之间的桥梁,管理所有的读写操作和内存刷新。

实验目标是掌握SDRAM的接口信号和操作指令。例如,`RAS_n`和`CAS_n`信号用于选择行和列地址,`WE_n`控制写入操作,而`BA[1:0]`用于选择不同的内存Bank。此外,数据掩码`DQM`允许选择性地禁用数据总线上的写入或读取,`DQ[15:0]`是双向数据总线,用于传输数据。

SDRAM的自动刷新操作是确保数据存储稳定性的重要机制,因为它定期刷新每个行以防止数据丢失。这个过程包括预充电、执行刷新命令、等待适当的延迟时间,并可能进行背靠背刷新。突发操作则是SDRAM提高性能的一种方式,它允许连续的数据在多个时钟周期内快速传输,通常用于连续访问内存中的数据块。

实验通过简单的读写比较和LED反馈,帮助学生直观地验证他们的控制器设计是否正确。这样的实践不仅加深了对SDRAM和FPGA接口的理解,也为更复杂的系统设计打下了坚实的基础。通过这个实验,学生可以学习到数字系统设计的基本原理,以及如何在实际项目中应用这些原理。

2021-07-13 上传

2023-07-30 上传

2023-08-02 上传

2023-05-15 上传

2023-05-27 上传

2023-09-17 上传

2023-12-21 上传

梦翼师兄

- 粉丝: 4

- 资源: 10

最新资源

- 前端面试必问:真实项目经验大揭秘

- 永磁同步电机二阶自抗扰神经网络控制技术与实践

- 基于HAL库的LoRa通讯与SHT30温湿度测量项目

- avaWeb-mast推荐系统开发实战指南

- 慧鱼SolidWorks零件模型库:设计与创新的强大工具

- MATLAB实现稀疏傅里叶变换(SFFT)代码及测试

- ChatGPT联网模式亮相,体验智能压缩技术.zip

- 掌握进程保护的HOOK API技术

- 基于.Net的日用品网站开发:设计、实现与分析

- MyBatis-Spring 1.3.2版本下载指南

- 开源全能媒体播放器:小戴媒体播放器2 5.1-3

- 华为eNSP参考文档:DHCP与VRP操作指南

- SpringMyBatis实现疫苗接种预约系统

- VHDL实现倒车雷达系统源码免费提供

- 掌握软件测评师考试要点:历年真题解析

- 轻松下载微信视频号内容的新工具介绍