FPGA实现数字钟控制器设计与分析

需积分: 10 39 浏览量

更新于2024-07-31

收藏 340KB PPT 举报

"基于FPGA数字钟控制器设计"

在本文中,我们将探讨如何使用FPGA(Field-Programmable Gate Array)技术设计一个数字钟控制器。该控制器能够显示24小时制的时、分、秒,并具备多种功能,如清零、时间调整以及整点报时。设计过程主要依赖于Max+plusⅡ软件,这是一种广泛用于FPGA设计的工具。

首先,设计任务包括实现一个能够计时、显示和控制的电子钟。这个数字钟需要具备以下功能:

1. 24小时循环计时,显示2位的小时、分钟和秒。

2. 通过千分频生成1Hz的时钟源,这对于精确计时至关重要。

3. 使用LED动态显示时、分、秒,提供清晰的视觉反馈。

4. 设有清零功能,允许用户重置时间。

5. 提供调节小时和分钟的选项,方便设置时间。

6. 整点报时功能,每当小时变化时触发报时。

数字钟的核心组成部分包括:

1. 脉冲电路:这部分的任务是接收输入的基准脉冲,通过分频产生1Hz的时基脉冲,同时生成扫描电路所需的脉冲源。

2. 计数电路:设计60进制(秒)和24进制(时)计数器,同时包含对分钟的60进制计数器。计数器间通过进位信号相连,使得秒进位到分,分进位到时,形成完整的计时链。

3. 扫描电路:负责秒、分、时六位数码管的动态扫描,使得每个时间单元依次被选中并在LED上显示。

4. 显示电路:使用BCD(二进制编码十进制)译码器将计数器的输出转换为适合LED显示的格式。

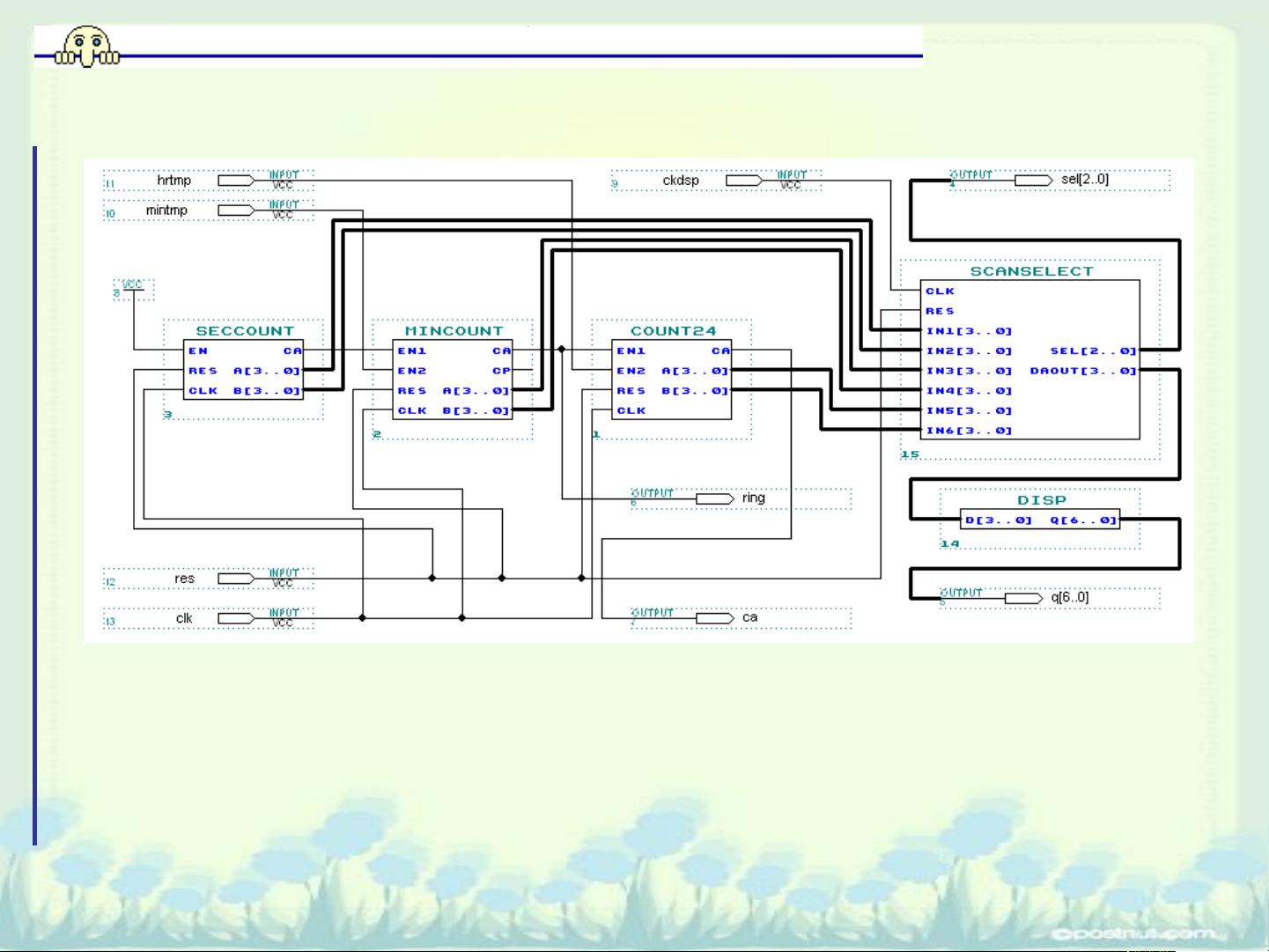

设计中采用了EPM7128SLC84-6 FPGA芯片,内部包含了五个关键模块:

1. 秒计数器(seccount):这是一个60进制BCD计数器,接收1Hz时钟信号,输出个位和十位的BCD码,并产生进位信号。

2. 分计数器(mincout):基于秒计数器的进位信号,实现60进制计数。

3. 时计数器(count24):接受分计数器的进位,执行24进制计数。

4. LED动态显示扫描模块:根据扫描脉冲ckdsp,轮流选通秒、分、时的数码管。

5. LED显示译码器:将计数器的BCD码解码成LED可识别的形式。

VHDL语言用于编写这些模块的源代码,它是一种硬件描述语言,能够精确地描述逻辑电路的功能和行为。通过Max+plusⅡ,这些VHDL代码可以被综合、布局和布线,最终生成FPGA配置文件,加载到实际设备中实现数字钟的功能。

基于FPGA的数字钟控制器设计涉及到了数字逻辑设计的基础知识,包括分频器、计数器、扫描电路和译码器的构建。这种设计方法展示了FPGA在实现复杂数字系统中的灵活性和可编程性。

512 浏览量

1224 浏览量

104 浏览量

184 浏览量

117 浏览量

213 浏览量

chenshihui120

- 粉丝: 0

- 资源: 1

最新资源

- 【容智iBot】8iBot=RPA+AI:数字化生产力为企业赋能.rar

- 操作系统课件+实验.rar_mightpol_wonsps_操作系统_操作系统实验

- TestYo:测试

- iocage-plugin-zabbix5-server

- 时代变频器在纺织机械行业中的应用.rar

- 【容智iBot】7你知道AI人工智能对我们的意义吗?.rar

- gimp-plugin-pixel-art-scalers:Gimp插件,用于使用hqx,xbr和scalex等Pixel Art Scalers重新缩放图像

- SpringBoot2.7整合SpringSecurity+Jwt+Redis+MySQL+MyBatis完整项目代码

- tarsnapper:tarsnap包装器,使用gfs-scheme使备份失效

- HC110110017 链路状态路由协议-OSPF-ospf.rar

- AreSolutionsClinicMobile:Spring世博会命令行界面,API消费和Spring启动

- Map-Fu-开源

- webbrowser自动填表,并获取网页源码(iframe框架也可获取网页源码)

- janeway::milky_way:具有对象检查和许多其他功能的Node.js控制台REPL

- 批量单词翻译

- indicator:财务指标(EMA,MACD,SMA)