LS码在EDA/PLD及FPGA中的应用与实现

199 浏览量

更新于2024-08-31

收藏 300KB PDF 举报

"EDA/PLD中的LS码及其FPGA的实现"

本文主要探讨了LS码(Loose Synchronized)在EDA(电子设计自动化)/PLD(可编程逻辑器件)中的应用及其在FPGA(现场可编程门阵列)中的实现。LS码是一种由李道本教授提出的新型地址码,其设计目标是为了克服传统通信系统中,如CDMA(码分多址)系统,由于地址码如m序列、Gold序列和Walsh码的不理想相关性导致的自干扰问题。

LS码的关键特性在于其零相关性,这使得在特定的“零相关窗”内,码间干扰(ISI)和多址干扰(MAI)可以被有效地消除。这种特性将通信系统从干扰受限转变为噪声受限,提高了系统的整体性能和数据传输速率。由于LS码的这些优势,它可以显著降低对联合检测技术、智能天线技术的需求,仅需简单的功率控制即可实现高效通信。

在FPGA中实现LS码的扩频和解扩,不仅提供了高度的灵活性,还确保了数据传输的可靠性。FPGA广泛应用于软件无线电、雷达、图像处理和片上系统(SoC)等领域,因此LS码的这种实现方式对于现代通信系统具有重要意义。

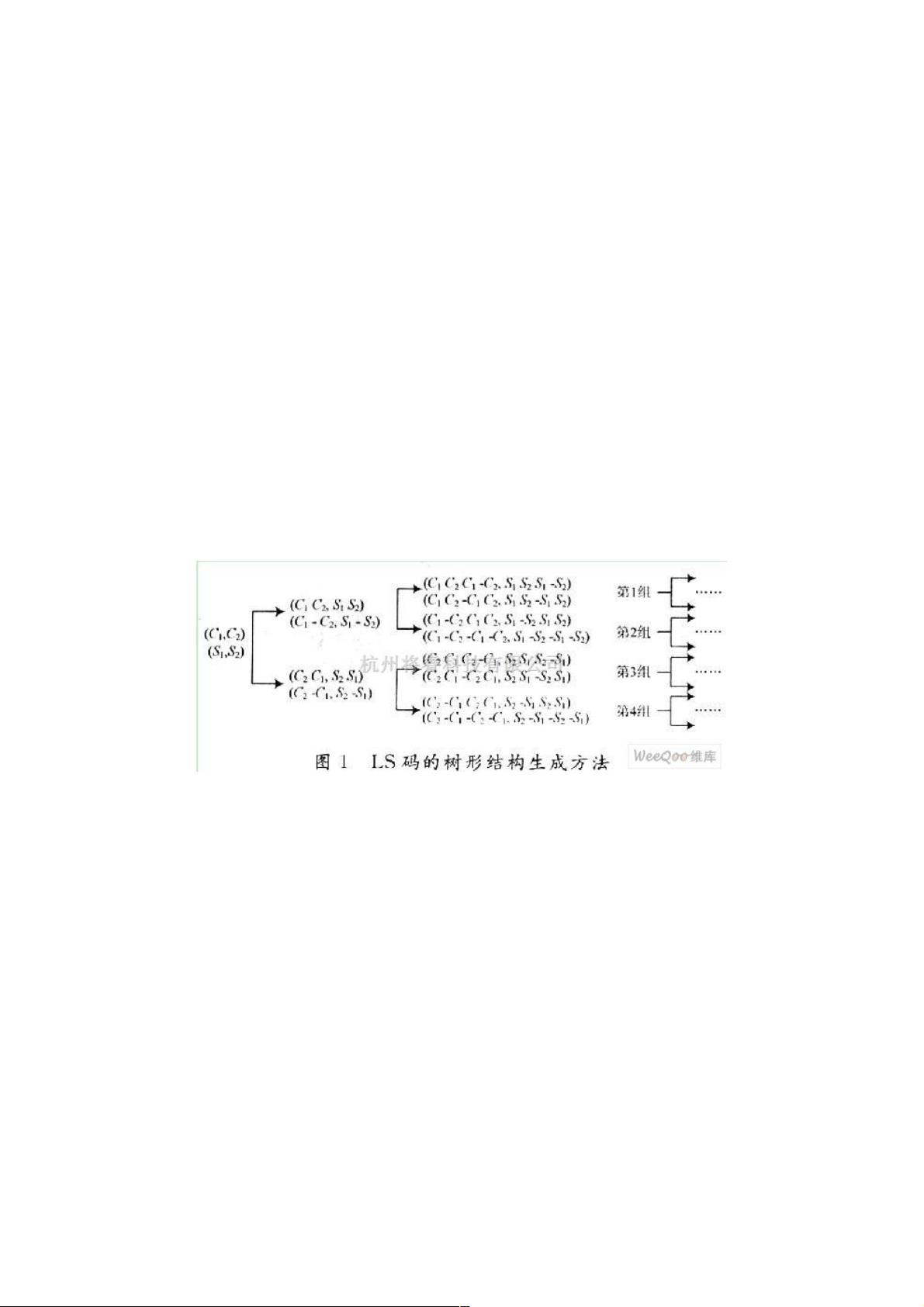

LS码的构造通常涉及多种方法,包括树形构造法、多项式生成法、与联合检测结合的组间零相关窗构造法以及Kronecker内积法。每种方法都保证了生成的LS码具备零相关窗特性,即在特定时延范围内,码之间的相关性为零,从而降低了干扰。

C码和S码是构成LS码的两个主要部分,它们各自的自相关和互相关值在特定范围内保持在一个理想的水平,这有助于进一步优化系统的抗干扰性能。通过精细调整LS码的生成参数,可以实现不同需求下的定制化通信系统。

在实际工程应用中,LS码的实现涉及到硬件描述语言(如VHDL或Verilog)编程,以及对FPGA内部资源的高效利用。这包括配置逻辑单元、触发器、存储器等,以实现LS码的生成、同步和解扩功能。同时,还需要考虑功耗、面积和速度等设计指标,以满足不同应用场景的需求。

LS码是通信领域的一个创新,它在FPGA中的实现为构建低干扰、高效率的通信系统提供了新的途径。随着EDA工具的进步和FPGA技术的不断发展,LS码的应用前景将更加广阔,有望在更多领域得到广泛应用。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2020-11-11 上传

2020-11-11 上传

2020-11-16 上传

点击了解资源详情

2017-12-29 上传

2023-02-28 上传

weixin_38681218

- 粉丝: 10

- 资源: 945

最新资源

- JHU荣誉单变量微积分课程教案介绍

- Naruto爱好者必备CLI测试应用

- Android应用显示Ignaz-Taschner-Gymnasium取消课程概览

- ASP学生信息档案管理系统毕业设计及完整源码

- Java商城源码解析:酒店管理系统快速开发指南

- 构建可解析文本框:.NET 3.5中实现文本解析与验证

- Java语言打造任天堂红白机模拟器—nes4j解析

- 基于Hadoop和Hive的网络流量分析工具介绍

- Unity实现帝国象棋:从游戏到复刻

- WordPress文档嵌入插件:无需浏览器插件即可上传和显示文档

- Android开源项目精选:优秀项目篇

- 黑色设计商务酷站模板 - 网站构建新选择

- Rollup插件去除JS文件横幅:横扫许可证头

- AngularDart中Hammock服务的使用与REST API集成

- 开源AVR编程器:高效、低成本的微控制器编程解决方案

- Anya Keller 图片组合的开发部署记录