80-Y0962-1 Rev. D 16 Confidential and Proprietary - Qualcomm Atheros, Inc.

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

QCA9882 Dual-Band 2x2 MIMO 802.11ac/abgn WLAN SoC Data Sheet Functional Specification

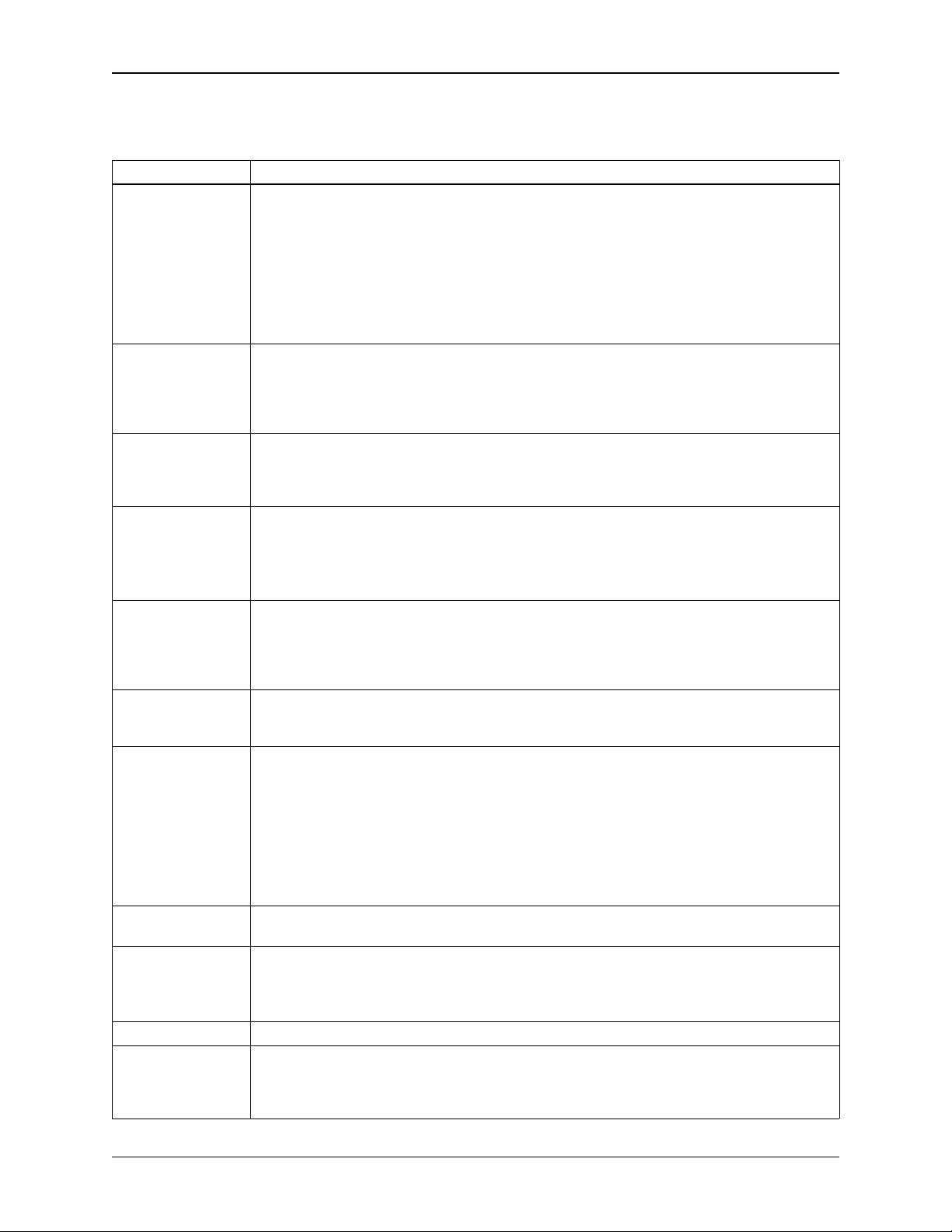

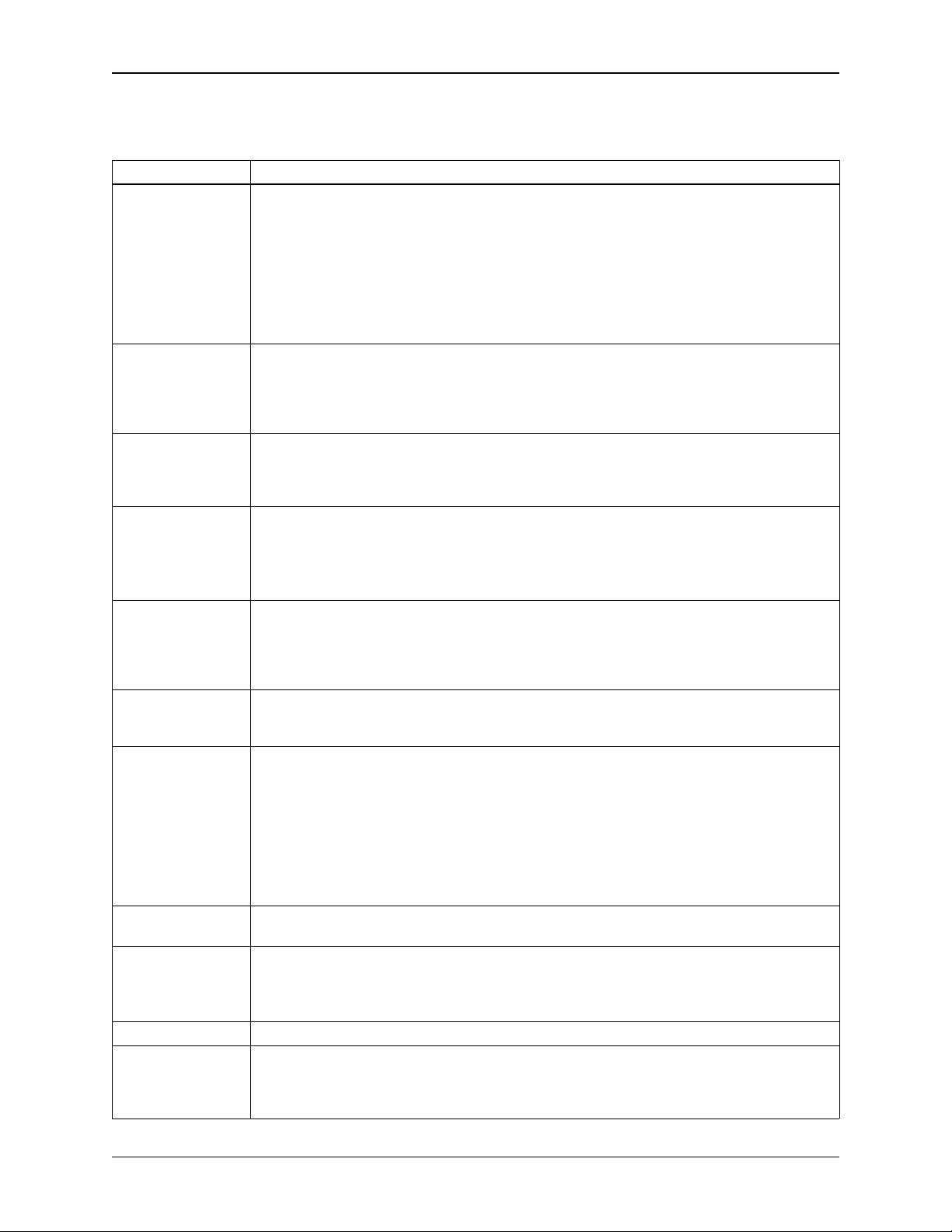

The QCA9882 is comprised of several internal functional blocks, as summarized in Table 3-1.

Table 3-1 Functional blocks

Block Description

AXI The AXI bus is accessed simultaneously by multiple masters in the PCIE host memory, CPU

memory, and all programmable registers. The WLAN portion of the AXI fabric supports split

transactions to achieve higher utilization on the PCIE bus.

All register access from the CPU route through the AXI fabric. A bridge converts AXI requests

to AHB requests, and the AHB arbiter selects between PCIE register access requests and

CPU register access requests on a round-robin basis. All register accesses for all modules

including the MAC, CE, and blocks such as GPIOs, RTC, or OTP use the APB protocol. A

bridge converts AHB requests into APB. It must be noted here that the entire AXI fabric, AHB,

and APB interfaces all run synchronously on the SoC clock domain. See AXI.

CE The copy engine (CE) establishes a communication channel between the firmware and the

host. It performs a DMA copy from one memory location (source memory) to another memory

location (destination memory), and it can perform this DMA copy operation in a batch, under

control of software. A copy involves a read operation from the source memory, followed by a

write operation to the destination memory.

WLAN Clocking The MAC/baseband clock domain runs off of the WLAN PLL. The PLL runs at either at

160 MHz or 176 MHz. The CPU/SoC clock domain runs off of the CPU PLL. The AXI fabric

together with the AHB and APB buses typically run at either half or quarter CPU clock. The

PCIE clock domain runs at 125 MHz.

CPU Core and

Memory Controller

The CPU is a Tensilica XTENSA 7.0 processor with a hardware abstraction layer (HAL) to

support low level WLAN activity with minimal support from the PCIE host.

The CPU is configured with a peripheral interface (PIF). The outbound PIF is used by the CPU

for register access. The inbound PIF is used by the other AXI masters (MAC and CE) to

access the data memory (DMEM) connected to the CPU.

MAC/Baseband/RF The integrated 2.4/5 GHz 802.11ac MAC/baseband/radio includes the features of maximal

likelihood (ML) decoding, low-density parity check (LDPC), and maximal ratio combining

(MRC). The MAC includes a offload engine (OLE) block responsible for A-MSDU scatter and

gather, L2 header encapsulation and decapsulation, IP/TCP/UDP checksum, and Rx

classification.

PCIE Core All programmable registers can be accessed by either the PCIE host or by the internal CPU.

The PCIE core provides a simple proprietary low-bandwidth controller (LBC) interface for

register accesses.

PCIE Configuration

Space Registers

The QCA9882 PCIE configuration space maps to the host memory space. All programmable

registers can be accessed either by the PCIE host or by the internal CPU. The PCIE core

provides a simple proprietary low-bandwidth controller (LBC) interface for register accesses. A

bridge converts this LBC interface into standard AHB. An AHB-AHB bridge synchronizes the

clock domain from the PCIE clock domain to the SoC clock domain.

Some additional registers are accessible only by the PCIE host. These registers run on the

PCIE clock domain and are not routed through the main AHB arbiter. They allow the PCIE host

to determine the sleep status of the SoC and to wake up the SoC if needed. See PCIE

configuration space register descriptions.

WLAN AHB Arbiter Selects between the PCIE register access requests and CPU register access requests on a

round-robin basis.

WLAN GPIOs All digital pins map to 16 GPIOs. These GPIOs are used for a variety of purposes such as BT

coexistence, UART, I

2

C, SPI, JTAG. Another set of digital outputs are the four antenna

switches used as scan outputs during ATPG testing. The 16 GPIOs are divided into GPIOs

dedicated to BT and to WLAN, 8 to BT and 8 to WLAN. See GPI/GPIO.

WLAN OTP WLAN one-time programmable (OTP) memory

WLAN RTC The RTC block controls the clocks and power going to other modules within the chip. Its inputs

consist of sleep requests from these modules and its outputs consists of clock enable signals

used to gate the clocks going to these modules. The RTC block also manages resets going to

other modules within the device.