i.MX 6Solo/6DualLite Applications Processors for Consumer Products, Rev. 3

16 Freescale Semiconductor

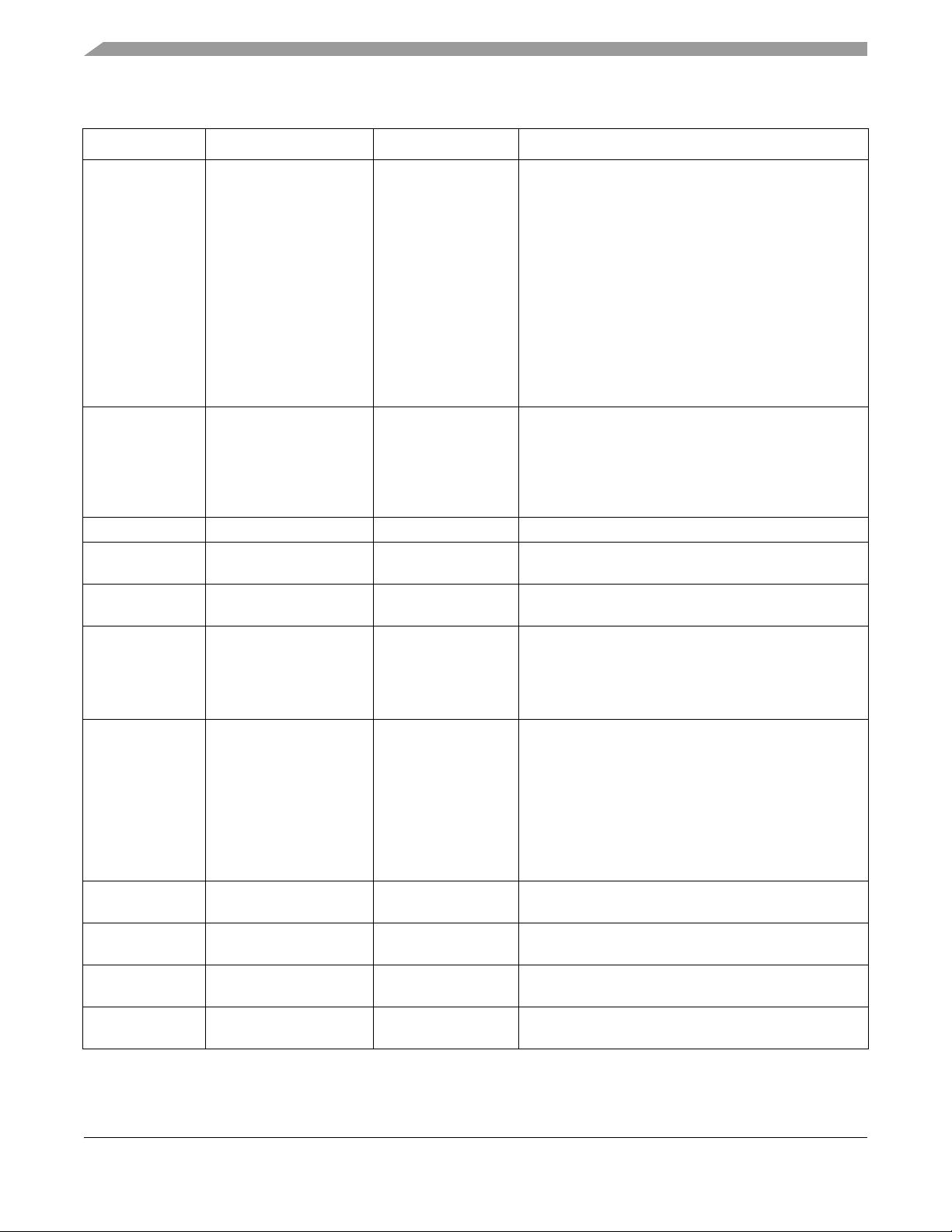

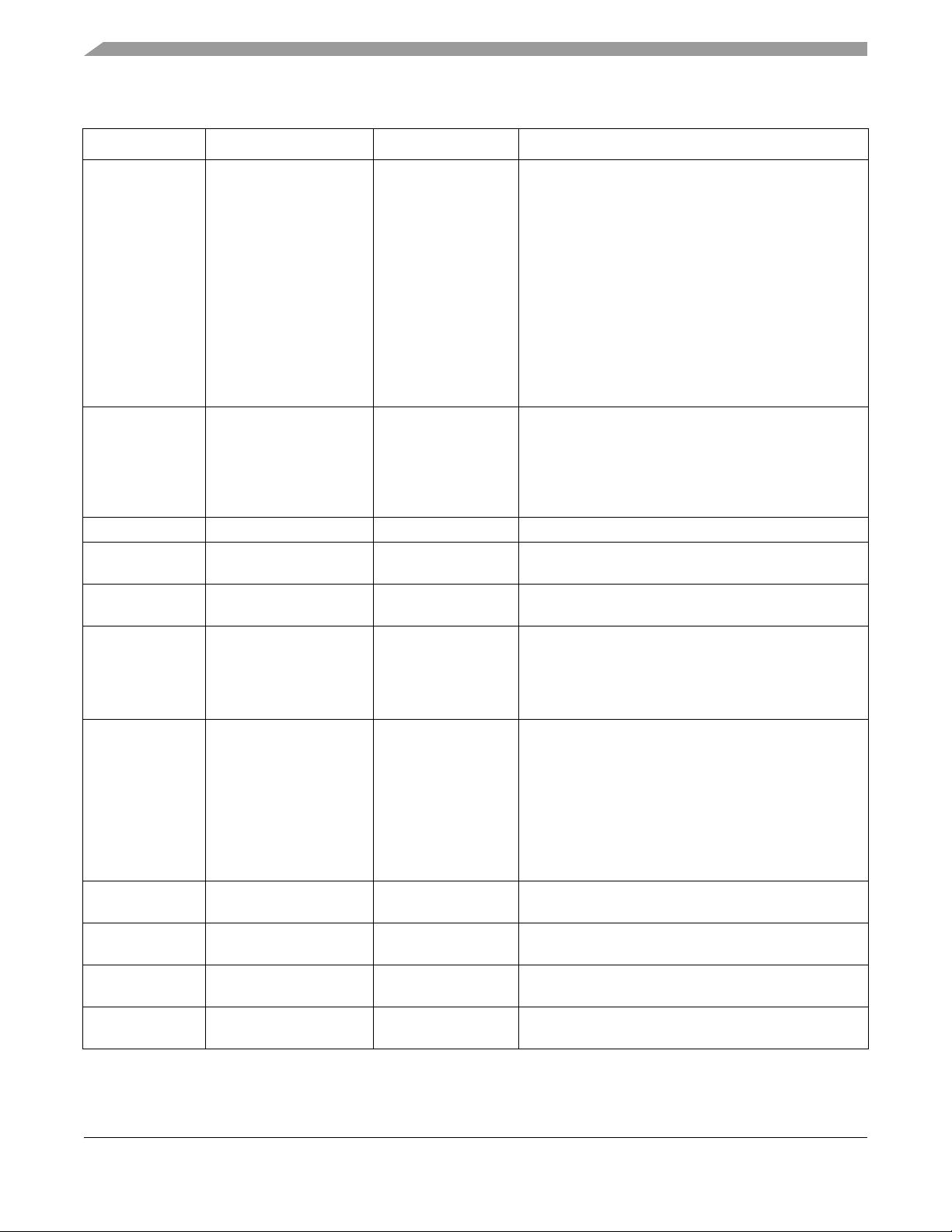

Modules List

OCOTP_CTRL OTP Controller Security The On-Chip OTP controller (OCOTP_CTRL) provides

an interface for reading, programming, and/or overriding

identification and control information stored in on-chip

fuse elements. The module supports

electrically-programmable poly fuses (eFUSEs). The

OCOTP_CTRL also provides a set of volatile

software-accessible signals that can be used for

software control of hardware elements, not requiring

non-volatility. The OCOTP_CTRL provides the primary

user-visible mechanism for interfacing with on-chip fuse

elements. Among the uses for the fuses are unique chip

identifiers, mask revision numbers, cryptographic keys,

JTAG secure mode, boot characteristics, and various

control signals, requiring permanent non-volatility.

OCRAM On-Chip Memory

controller

Data Path The On-Chip Memory controller (OCRAM) module is

designed as an interface between system’s AXI bus and

internal (on-chip) SRAM memory module.

In i.MX 6Solo/6DualLite processors, the OCRAM is

used for controlling the 128 KB multimedia RAM through

a 64-bit AXI bus.

OSC32KHz OSC32KHz Clocking Generates 32.768 KHz clock from external crystal.

PCIe PCI Express 2.0 Connectivity

Peripherals

The PCIe IP provides PCI Express Gen 2.0 functionality.

PMU Power-Management

functions

Data Path Integrated power management unit. Used to provide

power to various SoC domains.

PWM-1

PWM-2

PWM-3

PWM-4

Pulse Width Modulation Connectivity

Peripherals

The pulse-width modulator (PWM) has a 16-bit counter

and is optimized to generate sound from stored sample

audio images and it can also generate tones. It uses

16-bit resolution and a 4x16 data FIFO to generate

sound.

PXP PiXel Processing Pipeline Display Peripherals A high-performance pixel processor capable of 1

pixel/clock performance for combined operations, such

as color-space conversion, alpha blending,

gamma-mapping, and rotation. The PXP is enhanced

with features specifically for gray scale applications. In

addition, the PXP supports traditional pixel/frame

processing paths for still-image and video processing

applications, allowing it to interface with the integrated

EPD.

RAM

128 KB

Internal RAM Internal Memory Internal RAM, which is accessed through OCRAM

memory controller.

RAM

16 KB

Secure/non-secure RAM Secured Internal

Memory

Secure/non-secure Internal RAM, interfaced through

the CAAM.

ROM

96KB

Boot ROM Internal Memory Supports secure and regular Boot Modes. Includes read

protection on 4K region for content protection.

ROMCP ROM Controller with

Patch

Data Path ROM Controller with ROM Patch support

Table 3. i.MX 6Solo/6DualLite Modules List (continued)

Block Mnemonic Block Name Subsystem Brief Description