OpenRISC 1200 IP核规格初步草案:修订与更新

需积分: 16 108 浏览量

更新于2024-07-16

收藏 755KB PDF 举报

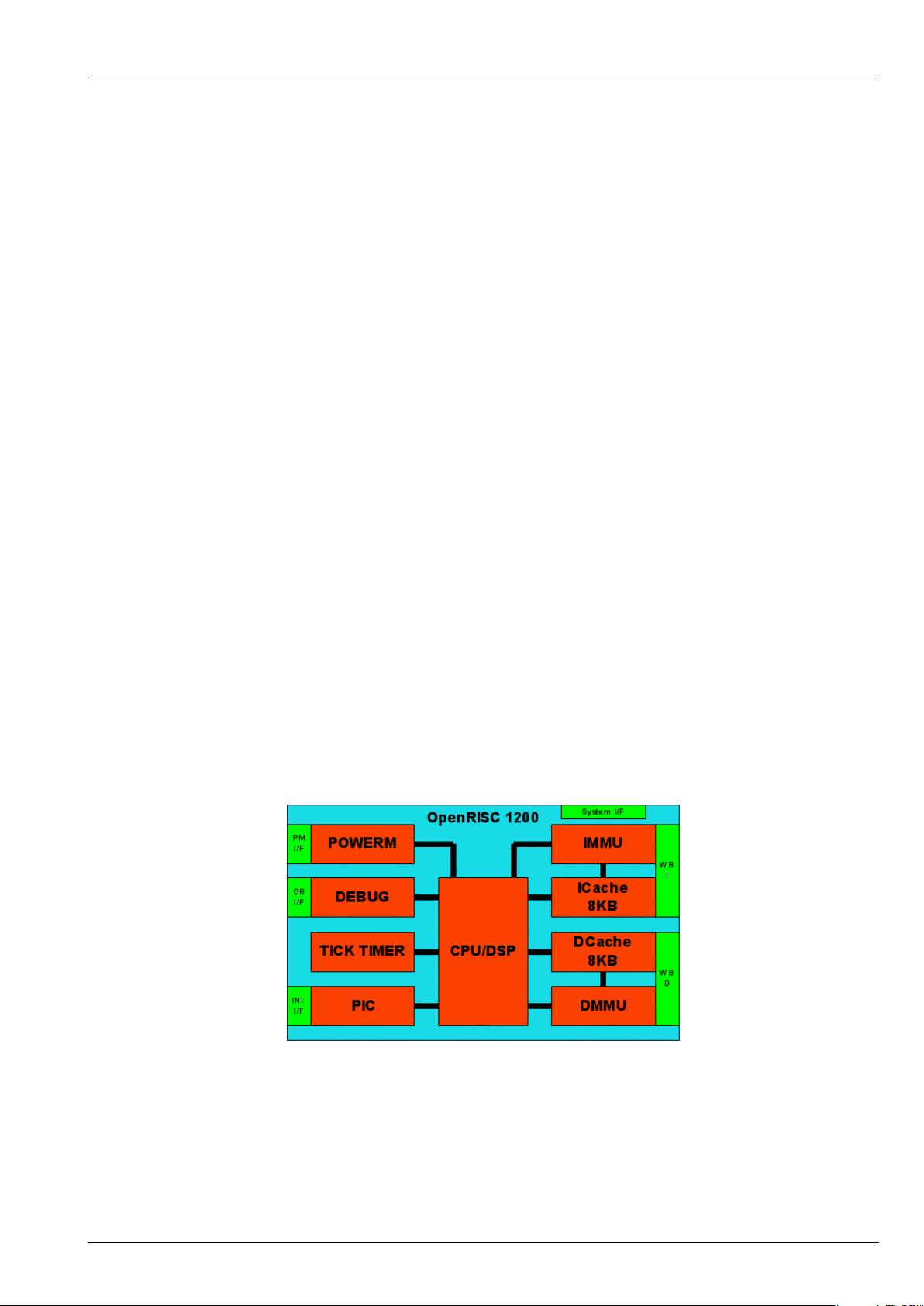

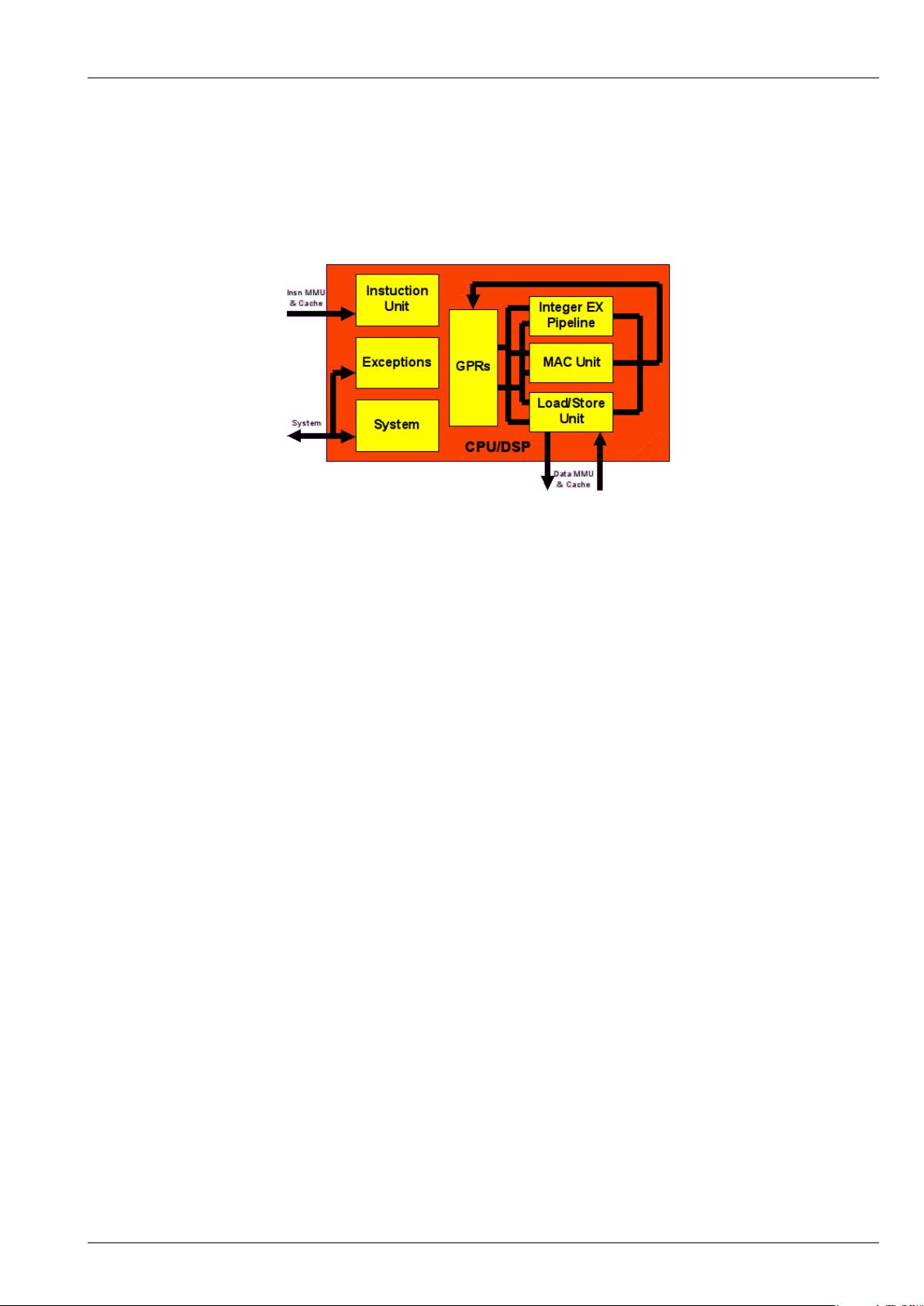

OpenRISC1200 IP Core Specification (Preliminary Draft) 是一份详细介绍了OpenRISC 1200微处理器核心架构的规格文档,该文档由Damjan Lampret和Julius Baxter共同编撰,历经多个版本的修订和完善。这份规格文件旨在提供关于OpenRISC 1200处理器的全面技术细节,包括但不限于硬件设计、指令集、架构特性、功能描述以及修订历史。

在"REVISION HISTORY"部分,我们可以看到文档从v0.1版本开始,初始草案由Damjan Lampret于2001年3月28日发布,随后经过多次迭代,如v0.2版本中第一次正式出版,v0.3版本完成大部分章节并修复了一些隐藏的错误,等待反馈以进行更新。随着与OR1K架构手册的同步(v0.4),文档进一步完善,特别是在v0.5版本中解决了已知的问题。

值得注意的是,v0.6版本对特殊处理寄存器(SPR)地址进行了调整,而在v0.7版本中,调试单元被简化以提高性能。到了v0.8版本,文档增加了关于浮点处理单元(FPU)实现、数据缓存写回能力的信息,以及处理器输入时钟的详细描述。此外,还对参考文档进行了更新,特别是指令执行阶段周期表,增加了除法操作周期,并对configuration registers(配置寄存器)中的位进行了相应调整,以保持与最新OR1200规范的兼容性。

v0.9版本进一步澄清了支持的OR1K指令集部分,明确了核心功能的明确边界,修复了核心时钟输入信息和指令执行阶段周期表的表述,提升了文档的精确性和一致性。

通过这份OpenRISC1200 IP Core Specification,用户可以了解到这款处理器的核心特性和设计决策,对于嵌入式系统开发者来说,这是一份至关重要的参考资料,能够帮助他们理解和优化基于OpenRISC 1200架构的应用程序。随着文档的不断更新,它反映了OpenRISC社区对技术演进的持续关注和努力。

252 浏览量

2013-12-03 上传

2024-01-10 上传

2024-06-26 上传

2024-06-26 上传

2023-04-21 上传

2023-08-02 上传

2024-10-13 上传

carl_andrew73

- 粉丝: 0

- 资源: 2

最新资源

- zlib-1.2.12压缩包解析与技术要点

- 微信小程序滑动选项卡源码模版发布

- Unity虚拟人物唇同步插件Oculus Lipsync介绍

- Nginx 1.18.0版本WinSW自动安装与管理指南

- Java Swing和JDBC实现的ATM系统源码解析

- 掌握Spark Streaming与Maven集成的分布式大数据处理

- 深入学习推荐系统:教程、案例与项目实践

- Web开发者必备的取色工具软件介绍

- C语言实现李春葆数据结构实验程序

- 超市管理系统开发:asp+SQL Server 2005实战

- Redis伪集群搭建教程与实践

- 掌握网络活动细节:Wireshark v3.6.3网络嗅探工具详解

- 全面掌握美赛:建模、分析与编程实现教程

- Java图书馆系统完整项目源码及SQL文件解析

- PCtoLCD2002软件:高效图片和字符取模转换

- Java开发的体育赛事在线购票系统源码分析